RDL 技术是先进封装异质集成的基础,广泛应用扇出封装、扇出基板上芯片、扇出层叠封装、硅光子学和 2.5D/3D 集成方法,实现了更小、更快和更高效的芯片设计。OSAT、 IDM和代工厂在这条道上的竞争日益激烈。如今RDL L/S 扩展到最先进 2μm及以下。未来三年将进入亚微米,赋能扇出封装更高效能集成。本文为各位看官汇报了相关趋势展望与企业技术进展。

随着先进封装的深入进展,重新分布层(RDL)技术获得了巨大的关注。这种革命性的封装技术改变了我们封装 IC 的方式。

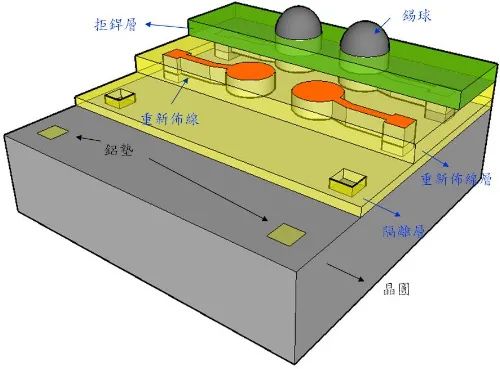

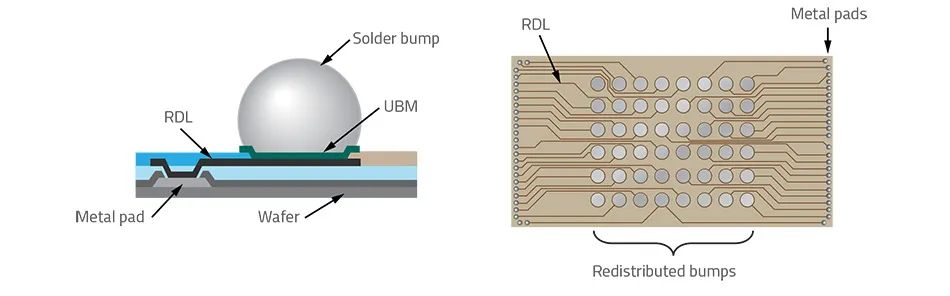

再分布层,RDL(Re-distributed layer),是实现芯片水平方向电气延伸和互连,面向 3D/2.5D 封装集成以及FOWLP的关键技术。它在芯片表面沉积金属层和相应的介电层,形成金属导线,并将IO端口重新设计到新的、更宽敞的区域,形成表面阵列布局。这项技术使得芯片间的键合更薄、工艺更简单。RDL技术有助于设计人员能够以紧凑且高效的方式放置芯片从而减少器件的整体占地面积。

CoWoS-R 插图,CoWoS-R 是台积电开发的一种 3D 集成技术,可在单个封装中堆叠多个芯片图源:TSMC

降低设备成本:RDL 技术消除了昂贵且耗时的引线键合和倒装芯片键合工艺,减少了设备所需的元件数量,有助于降低设备成本。还用于创建需要小外形尺寸的高性能 IC。

减少占地面积:RDL将多个芯片集成到单个封装中,从而减少器件的整体占地面积。这有助于打造更微型更紧凑的电子元件,这对智能手机、可穿戴设备和物联网设备至关重要。

芯片上的重新分布层 (RDL) 图源:Lam Research

最后的芯片扇出 WLP 相对于 FCBGA 和 PoP 架构将封装厚度减少了 50%。图源:三星

改善电气性能:RDL 中介层因具有极小的信号通孔尺寸,而大幅改善了 SerDes 信号完整性 (SI),并且因 RDL 金属厚度而改善了内存 SI。此外,采用的低损耗介电材料有助于降低介电损耗。

提高设计灵活:RDL 介质层利用精细的线路宽度和间距减少了路由干绕,提供了一种在 IC 内路由信号和电源的方法,支持更多的引脚数量。I/O触点间距更灵活、凸点面积更大。

封装应用广泛:广泛用于MEMS器件、传感器、功率器件、存储器、微处理器和图形处理器的封装。

技术趋势与挑战

RDL的技术进步对先进封装意义非常。如今,4层RDL已经成熟,良率已达到99%的水平,约85%的封装需求可以通过4层 RDL 来满足,未来几年,布线层数从4层增加到8层以上。头部厂商封装业务 RDL L/S 将从2023/2024年的2/2μm发展到2025/2026的1/1μm,再跨入到2027年以后的0.5/0.5μm。

RDL技术是一个复杂的过程,通常涉及半加成工艺,包括电介质沉积、湿法或干法蚀刻、阻挡层和籽晶层沉积以及镀铜。需要掩膜设备、涂胶机、溅射台、光刻机、刻蚀机以及其他配套工艺。

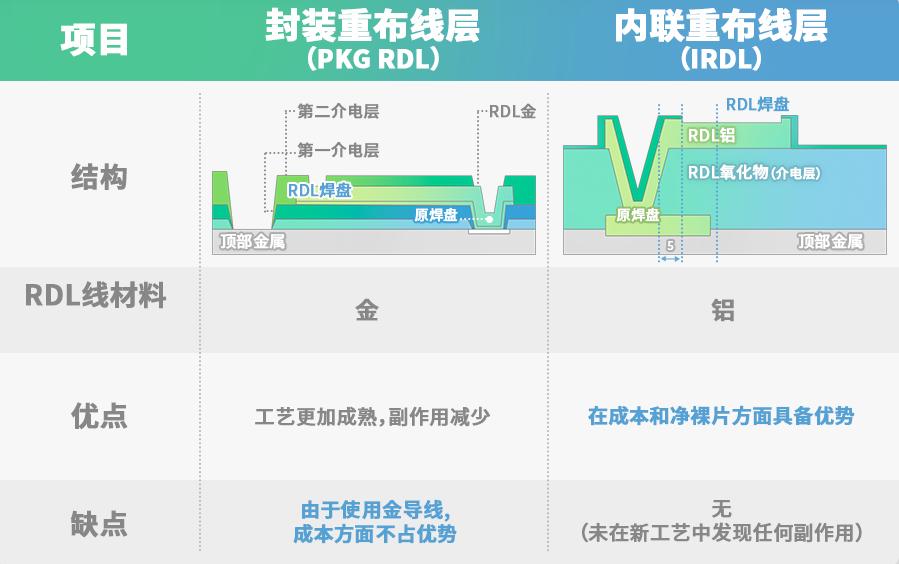

内联重布线(IRDL)层是一种先进的FAB技术,能够降低流程成本,可以在不损害现有芯片架构的前提下,将IO焊盘重新放置到封装所需的位置。这项技术可以缩减成品厚度,有力地推动SK海力士成为移动市场技术领导者。图源:SK海力士

先进扇出和异构封装中的问题包括芯片移位、芯片翘曲、芯片间应力以及 RDL 走线损坏的风险。RDL 工艺涉及在有机聚酰亚胺 (PI) 或聚苯并恶唑 (PBO) 薄膜的狭窄迹线内镀铜。新工艺旨在提高 RDL 粘附力,同时减少热循环过程中的机械应力和热应力。为了管理复杂的相互作用,先进的建模、材料工程和晶圆工艺正在投入使用,以确保稳健的 RDL 制造。

为了实现高密度、高带宽的芯片互连,推动RDL 技术的进步,国内同仁仍需要在L/S 1/1μm 细线条光刻、实现RDL 高 I/O 密度和精细 I/O 间距的微孔加加工技术、低介电常数和低耗损因子的介电材料上和半加成法上,实现设备工艺的精细化。

从国产设备端,封装内部 L/S 往更细方向发展,给国产光刻步进机提出更高要求;高端应用的封装尺寸普遍大于 1 reticle size,需引入更大尺寸 reticle size的光刻设备;2μm 以下 L/S 布线检测的国产 AOI 设备仍有很大发展空间。

| 企业 | FC | WLP | 2.5/3D | Chiplet | RDL |

| 日月光 | √ | √ | √ | √ | >6层L/S 1-1.5 μm |

| 安靠 | √ | √ | √ | √ | >4层 L/S 1-2 μm |

| 台积电 | √ | √ | √ | √ | 6-14层 L/S 2 μm及以下 |

| 三星 | √ | √ | √ | √ | >4层 L/S 2 μm |

| 长电科技 | √ | √ | √ | √ | 5层L/S2μm |

| 通富微电 | √ | √ | √ | √ | 5层L/S2μm |

| 华天科技 | √ | √ | √ | √ | >4层 L/S 2 μm |

头部企业封装品种RDL现有技术对比来源:未来半导体

厂商技术方案进展

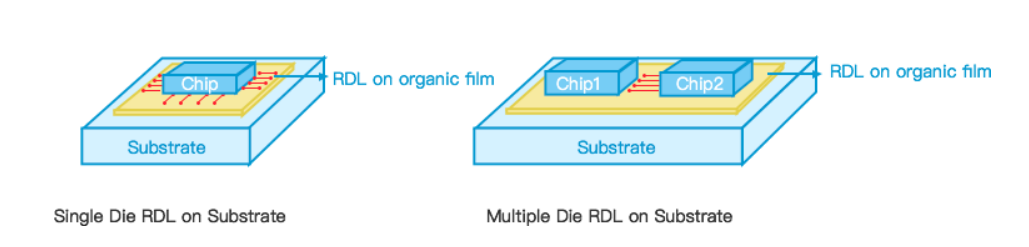

扇出型晶圆级封装(FOWLP)作为新的异构集成技术,与传统的2.5D/3D 结构相比,可以实现薄、高密度和低成本的封装。其中就体现了RDL成本低的优势,也是RDL最关键的技术,可用于创建具有小外形尺寸的高性能封装。

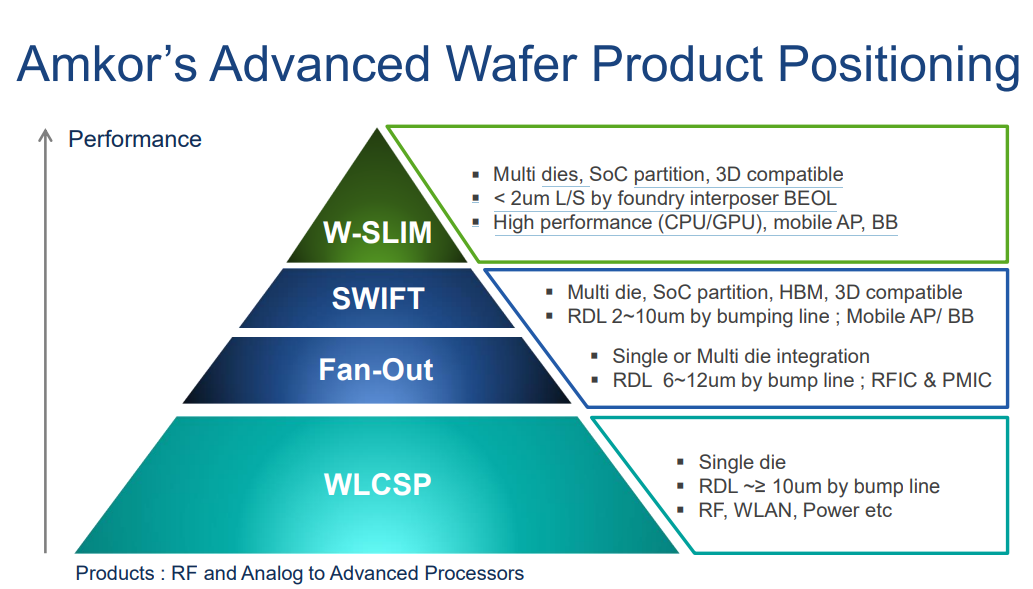

FOWLP受到一线公司的封装技术支持,并以各自的产品命名,如台积电的 InFo-Wlp,英飞凌/日月光/STATS ChipPAC的eWLB、安靠的SWIFT、Deca的M-Series,JCAP的ECP,Nepes的RCP,SPIL的TPI-FO等。

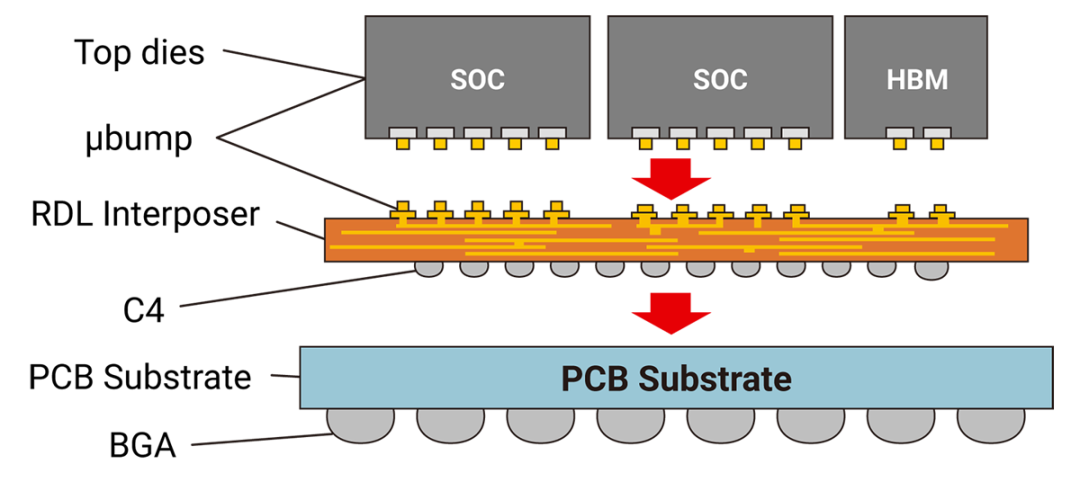

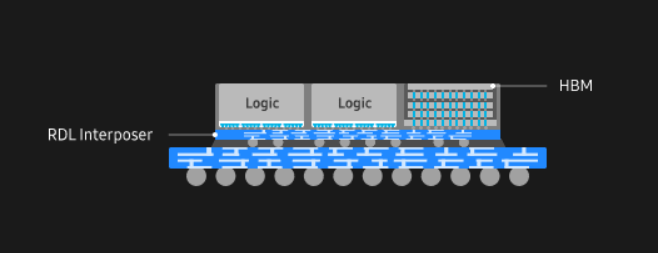

台积电为片上系统 (SoC)、存储器件和功率器件等各种应用提供广泛的 RDL 技术解决方案,一个人寂寞狂奔。台积电面向HPC应用应用的是CoWoS应用。其中CoWoS-R利用InFO技术和RDL中介层实现HBM和SoC集成,也是低成本方案。CoWoS-L结合了CoWoS-S和InFO技术的优点,使用夹层与LSI(局部硅互连)芯片进行互连,使用 RDL层进行电源和信号传输,提供灵活的集成。

台积电目前向包括 NVIDIA 和 AMD 在内的一系列客户提供 CoWoS 服务,用于其当前和即将推出的 AI GPU。半导体设计的转变和对先进封装的依赖促使台积电扩大其 CoWoS 设施以满足不断增长的需求。

InFO是一个创新的晶圆级系统集成技术平台,具有高密度RDL,可实现移动、高性能计算等各种应用的高密度互连和性能。相较于CoWoS方案,InFO则采用RDL代替硅中介层,无须TSV,性价比更高。

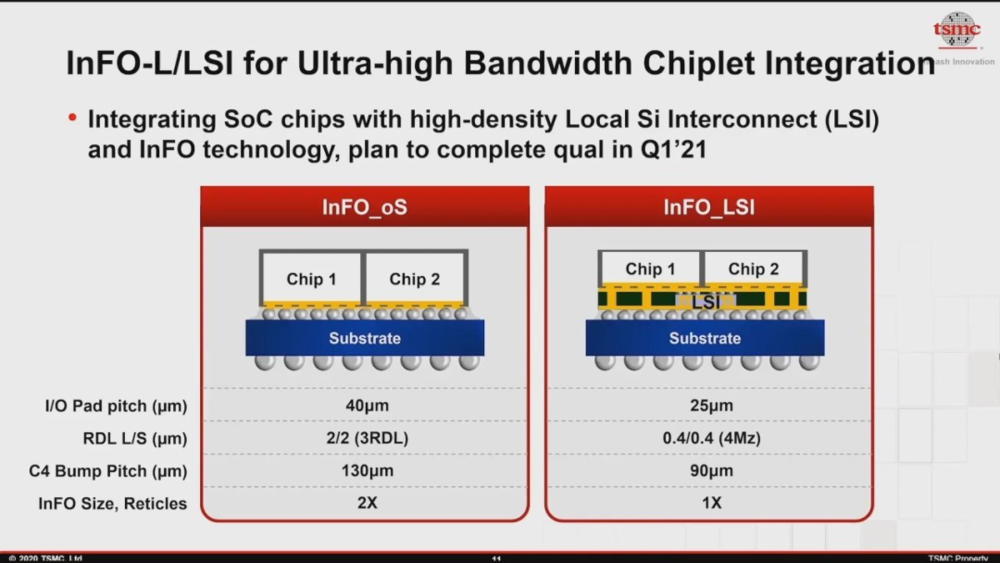

图源:台积电

标准封装具有核心基板,先进集成扇出每侧都有 2 至 5 层重新分布层 (RDL),台积电的InFO_oS 将这一概念提升到了一个新的水平。InFO_oS 利用 InFO 技术具有更高密度的 2/2μm RDL 线宽/间距,它提供多达 14 个重新分布层 ,可实现芯片之间非常复杂的布线。在芯片附近的基板上还有一层更高密度的布线层。Info_LSI技术是InFO_oS的升级版,此种封装使用硅桥(RDL L/S:0.4/0.4μm)以及RDL层代替整块硅达到了性能与成本的平衡。

InFO 用在了苹果 iPhone和Mac系列产品、在特斯拉的Dojo超算以及AMD巨兽级芯片MI300上。iPhone 15 Pro 搭载 A17 Pro APL1V02 应用处理器即采用铝作为再分布层 (RDL)。Tesla D1 小芯片包含3个窄RDL层和 3个厚RDL层。

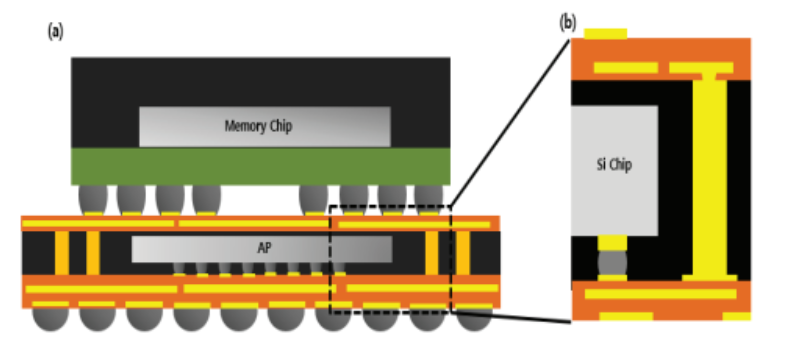

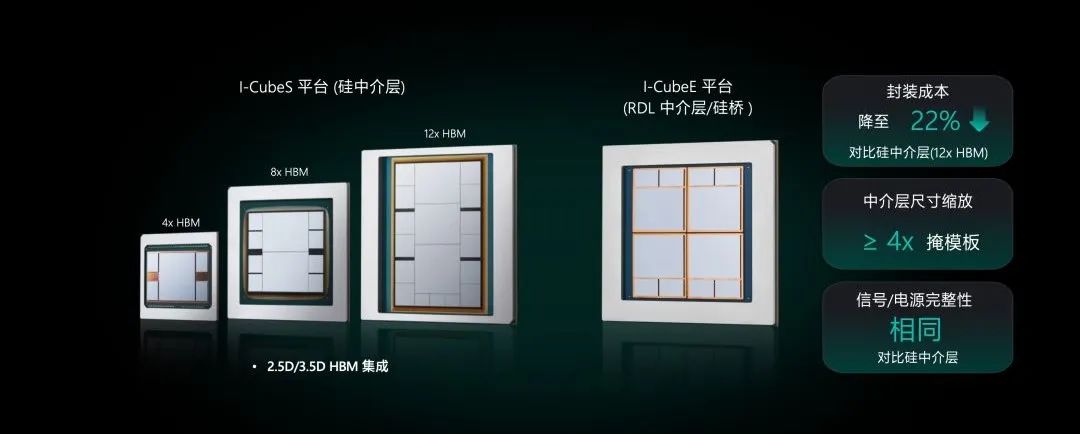

在这个全球加速转变的时代,同时应对恶霸的步步蚕食,三星正在针对AI、5G及HPC的成本/算力/性能/延迟/带宽/功能迭代集成解决方案。其中 I-CubeE采用集成硅桥的RDL中介层,对比现有硅中介层降低22%封装成本,且能够利用嵌入 FO-PLP 中间并用作接口的硅桥的小 L/S 优势硅芯片之间。除了提供信号与电源完整性,支持大于掩模板(Reticle)4倍以上的大尺寸封装。

图源:三星

R-Cube是三星电子的低成本 2.5D RDL 中介层技术,该技术通过高密度 RDL实现逻辑到逻辑和逻辑到 HBM(高带宽内存)模块的连接,相比H-Cube/X-Cube,更具备成本低、快速的周转时间、设计灵活性和信号完整性。Samsung Foundry 正在开发一款 2.5D 无硅通孔 RDL 中介层技术,配备 2/2um 的L/S,以及集成了 4 个 HBM 模块的大型中介层(约为 1600mm²)。

三星半导体半导体先进封装(AVP)业务团队正在致力于开发基于RDL、硅中介层/硅桥接和TSV堆叠技术的下一代2.5D和3D高级封装解决方案。据悉,三星计划明年推出其解决方案,并将其称为SAINT的高级互连技术(SAINT S、SAINT D、SAINT L),以与台积电广受欢迎的CoWoS封装技术竞争。

当前,三星正在争夺大量 HBM 内存订单,这些订单将继续为NVIDIA 的下一代 Blackwell AI GPU提供动力。还赢得了 AMD 下一代 Instinct 加速器的订单,但与台积电深度绑定的 NVIDIA 控制90%人工智能市场相比,该订单比例不足为傲。

正是这项技术的兴起,使得封装厂能够在扇出封装技术方面与头部晶圆代工厂展开竞争。包括 ASE、Amkor 和JCET在内的 OSAT提供多种具有先进 RDL 工艺的封装类型。

ASE 集团为内存、微处理器和图形处理器等各种应用提供广泛的 RDL 技术解决方案。其 VIPack 先进封装平台,利用先进的重布线层制程、嵌入式整合以及2.5D/3D 封装技术实现超高密度和性能设计的三维异质封装结构。其中FOCoS-CF 和 FOCoS-CL解决方案具备高层数(>6 层)和细线/间距(L /S = 1μm/1μm),适用于需要高密度芯片间连接、高输入/输出计数和高速信号传输的应用。

图源:ASE

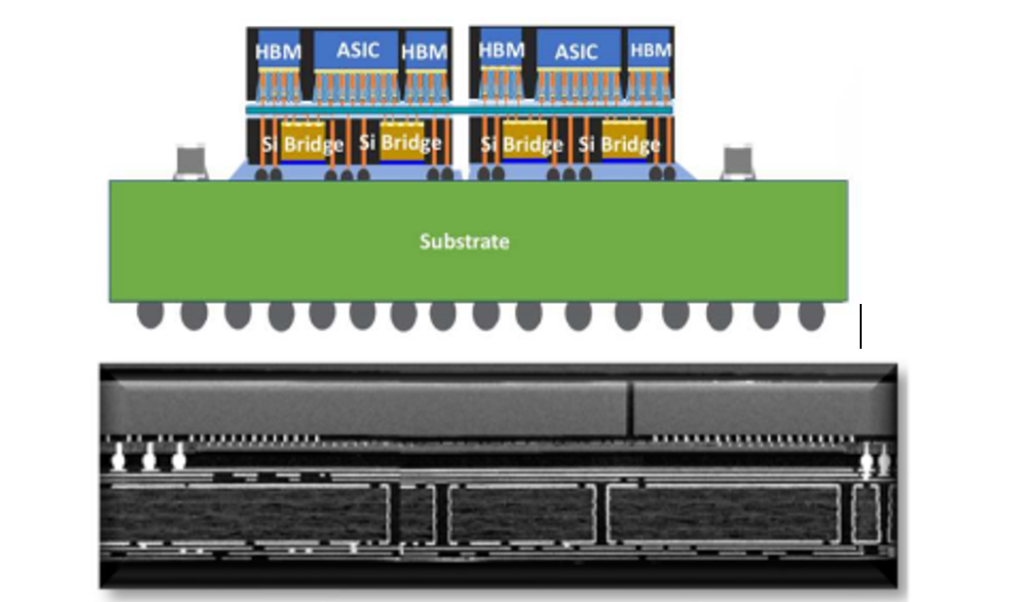

FOCoS(Fan-Out Chip on Substrate)封装技术可实现小芯片与多达五层的多个 RDL 互连、1.5/1.5μm 的较小 RDL L/S 以及 34x50mm²的大扇出模块尺寸的集成。它还提供广泛的产品组合集成,例如具有高带宽内存 (HBM) 的专用集成电路 (ASIC) 和具有 Serdes 的 ASIC,涵盖 HPC、网络、人工智能/机器学习 (AI/ML) 和云端。此外,由于消除了硅中介层并降低了寄生电容,FOCoS 比 2.5D Si TSV 表现出更好的电气性能和更低的成本。

FOCoS-CF 由两个面朝下的 ASIC 小芯片组成,通过 Cu 过孔直接与 RDL 连接,并且 Si 芯片和扇出 RDL (L/S 2/2 um) 之间没有微凸块;FOCoS-CL 由并排配置的三个小芯片(1 个 ASIC 芯片和 2 个 HBM)构建而成。ASIC 芯片和 2 个 HBM 通过 RDL (L/S 2/2 um) 和 Cu 微凸块连接。

FOCoS-Bridge是一种 2.5D 封装,它具有 ASIC和 HBM 两个芯片,两者通过嵌入 RDL 的硅桥芯片实现超细间距互连,硅桥芯片 (L/S 0.6/0.6 um) 嵌入扇出 RDL 层 (L/S 10/10 um),用于在 ASIC 和 HBM 之间建立连接。

扇出基板桥接芯片 (FOCoS-B) 原理图(上图)和横截面图(下图)可实现比 RDL 更小的芯片到芯片连接 (0.8μm)。资料来源:ASE/IEDM

日月光看好人工智能驱动的长期半导体需求,正在扩大马来西亚槟城工厂的产能。到今年底,日月光将有46座智能工厂,占全球半导体后段专业封测代工(OSAT)产业出货量比重约32%,占台湾地区OSAT出货量比重超过50%。

安靠科技是一家全球半导体封装和测试服务提供商。Amkor Technology 为传感器、MEMS 器件和功率器件等各种应用提供广泛的 RDL 技术解决方案。

图源:安靠

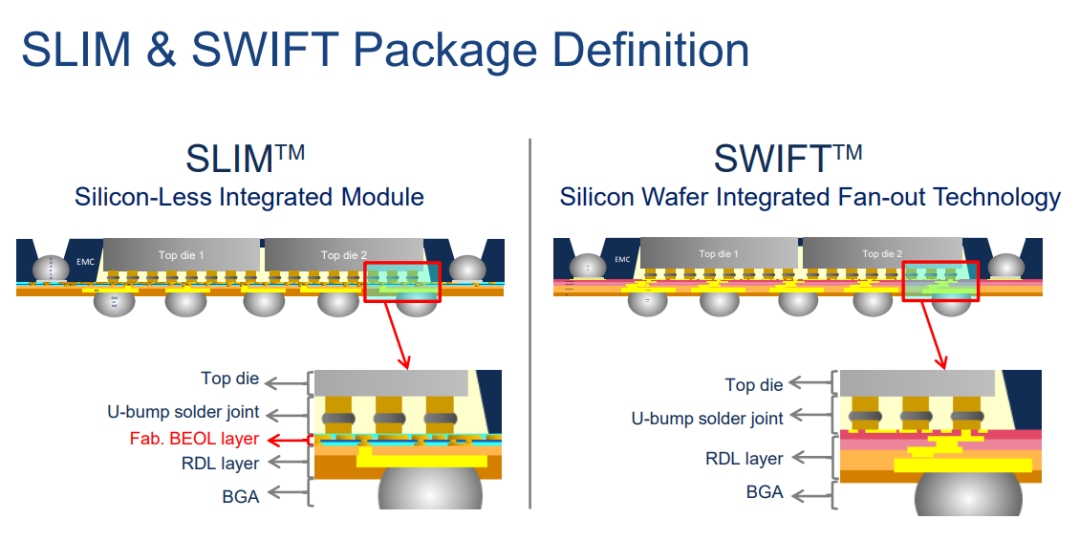

安靠的硅片集成扇出技术 ( SWIFT /HDFO) 旨在在更小的占地面积内提供更高的 I/O 和电路密度。SLIM及SWIFT方案均采用TSV-less工艺,其中SWIFT是Amkor的最先进的高密度扇出结构,可以实现 2/2 μm 线/间距特性,从而实现通常使用2.5D TSV 的SoC 分区和网络应用所需的非常高密度的芯片到芯片连接。细间距芯片微凸块为应用处理器和基带设备等先进产品提供高密度互连。SLIM利用前道代工,在硅片表面的无机介质层上制作1µm,甚至亚微米金属布线,L/S小于 2um。

图源:安靠

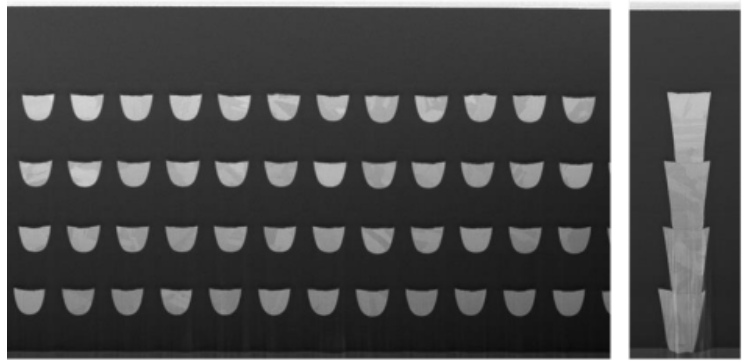

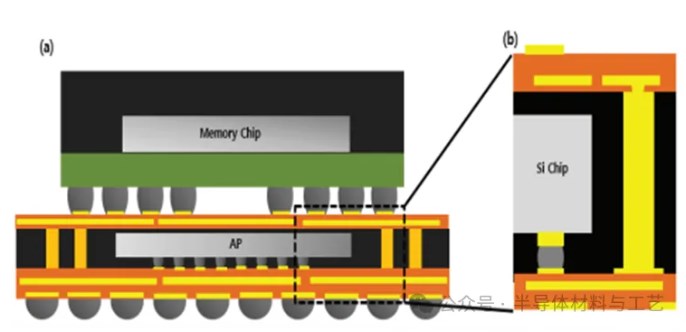

HDFO高密度扇出性封装是基于SWIFT开发而成的异构芯片封装方案, 先将有微凸块的芯片贴合至RDL预布线的介质层,也就是中段组装流程,切单后再倒装至FCBGA 基板以完成异构芯片封装。该技术保持了高密度连线,出色的信号质量,无需TSV,在GPU 和FPG、服务器市场上进一步降低封装成本。

具有 2/1μm L/S 和 2μm 通孔堆叠的 4 层 RDL。图源:Amkor

10月份,总投资16亿美元的安靠越南芯片封测工厂开始运营。Amkor正在提高先进封装生产能力,2023年初为3000晶圆/月,预计到2024年上半年,2.5D封装量将达到5000个晶片/月。到2024年,英伟达预计将占安靠2.5D封装产量的70-80%。

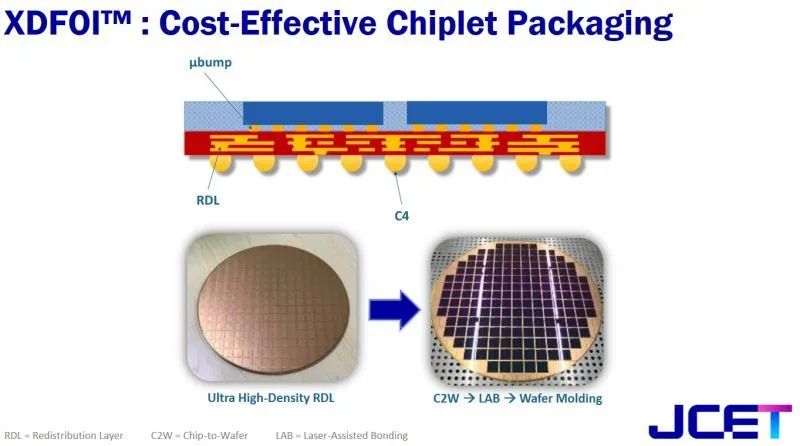

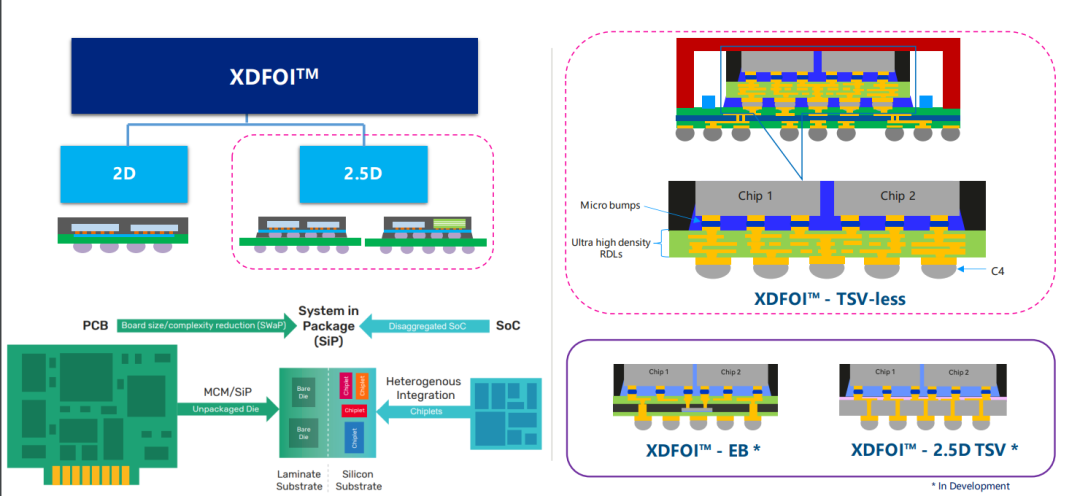

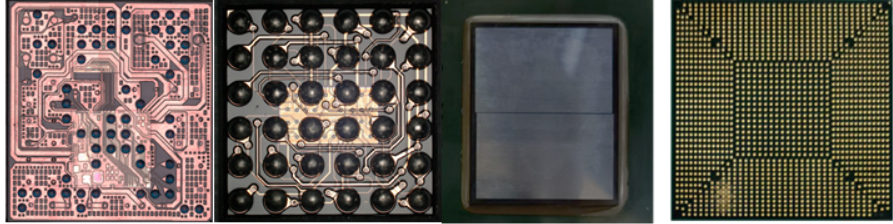

在RDL技术能力上,长电科技拥有国内领先的XDFOI平台,该平台是一种基于 RDL 的高性价比小芯片封装解决方案,专为异构集成量身定制。可实现线宽和线距低至 2 微米的多个重新分布层 (RDL)。此外,极窄的凸点间距互连技术和大封装尺寸允许集成多个芯片或小芯片、高带宽存储器和无源元件。

图源:长电/linkedin

XDFOI将一个或多个逻辑芯片(CPU/GPU等)、I/O芯片和/或高带宽内存芯片(HBM)放置在RDL堆栈中介层(RSI)上,形成高度集成的异构封装。XDFOI可以将高密度fcBGA基板“小型化”,将部分分布层转移到RSI基板上,利用RSI线宽和线距缩小至2微米的优势,减少芯片互连间距,实现更高效率以及灵活的系统集成。另外,部分SoC互连可以转移到RSI,实现基于Chiplet的结构创新和芯片的高性能和低成本。

目前长电科技XDFOI已有稳定量产的2.5D RDL高性能封装方案,并持续推进多样化方案的研发及量产,向国内外客户提供面向小芯片架构的高性能先进封装解决方案,在行业技术及量产经验均居于领先。从产能布局,长电科技是国内最大参与者之一。长电科技临港工厂是国内首个大规模专业生产车规级芯片成品的先进封装基地。公司计划在2025年上半年实现设备进厂,然后进入到量产的阶段。

图源:长电/semi

通富微电有面向高性能计算研发和量产的 VisionS 2.5D/3D Chiplet方案,自建2.5D/3D产线全线通线,1+4产品及4层/8层堆叠产品研发稳步推进;基于ChipLast工艺的Fan-out技术,实现5层RDL超大尺寸封装(65×65mm);超大多芯片FCBGA MCM技术,实现最高13颗芯片集成及100×100mm以上超大封装。在FO系列中,提供Chip First和Chip last两种方案, 重分布L/S为2/2um,应用于MIC、RF、CPU、GPU和网络。

图源:通富微电

公司通过在多芯片组件、集成扇出封装、2.5D/3D等先进封装技术方面的提前布局,并且完成高层数再布线技术开发,不断强化与客户的深度合作,满足客户AI算力等方面需求。

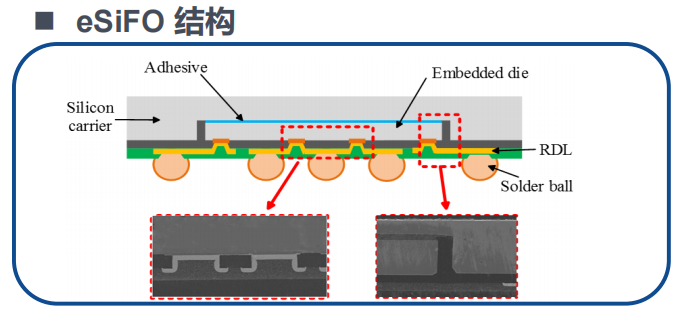

华天科技三维晶圆级封装平台3D Matrix 旗下有eSiFO和eSinC。在高密度晶圆级扇出型封装技术L/S为2/2um,RDL Layer为 6 P5M,封装尺寸15×15mm。eSiFO通过在硅基板上刻蚀凹槽,将芯片正面向上放置且固定于凹槽内,芯片表面和硅圆片表面构成了一个扇出面,在这个面上进行多层再布线,并制作引出端焊球,最后进行切割、分离和封装。

图源:华天科技/CSPT2023

eSinC将多颗芯片集成,用硅基取代塑封料,实现的封装尺寸最大可以达到40mm×40mm,未来RDL线宽线距越来越小,层数会越来越多。eSinC技术结合fine pitch RDL、hybrid bond、高级基板等平台技术,可以进一步提升封装密度,建立完整的Chiplet封装平台。

华天科技正在大力发展高端芯片的晶圆和成品测试业务,积极扩充高端测试产能规模。华天上海华天南京华天江苏三大工厂新封装项目明年起将陆续迎来量产。

甬矽电子正在积极布局先进封装相关领域,通过实施Bumping项目掌握的RDL及凸点加工能力,为公司后续开展晶圆级封装、扇出式封装及2.5D/3D封装奠定了工艺基础。公司致力于不断缩小线宽,目前最小线宽可达5um,最小线间距可达5um。公司运用于量产产品上的细线宽为最小线宽8um,最小线间距8um。

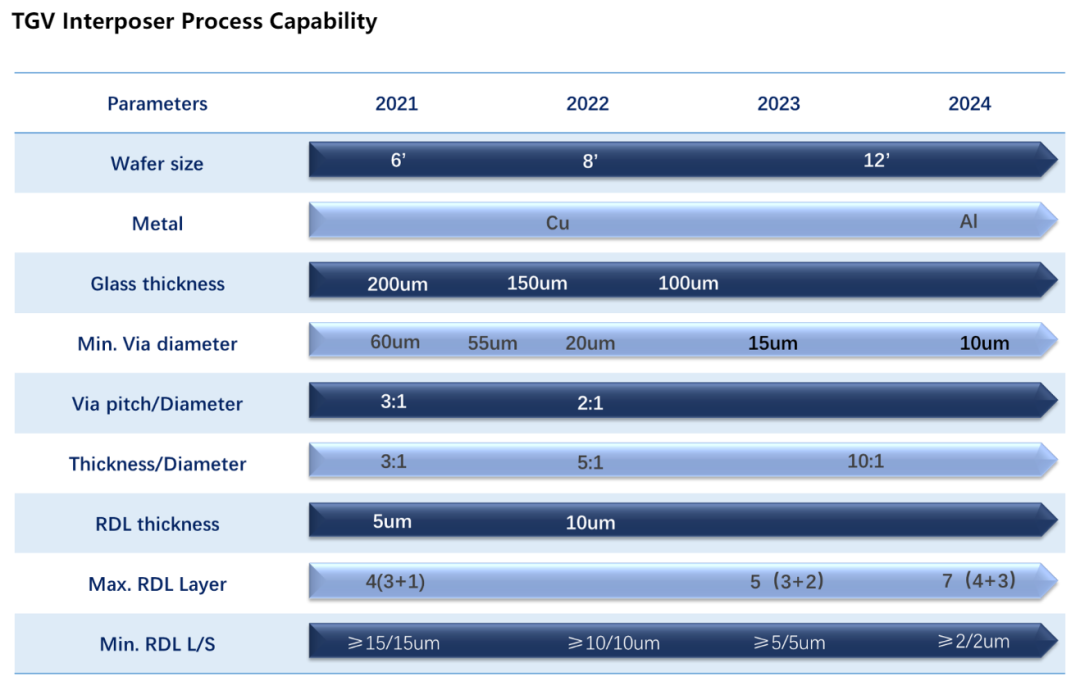

云天半导体开发了滤波器三维封装、新型扇出封装技术、玻璃通孔技术以及IPD技术,在玻璃通孔方向,用大马士革工艺在玻璃基表面制备三层RDL堆叠;采用无机薄膜材料作为介质层进行制备;实现更细更高精度的金属布线。2.5D TGV 将现有的5层 RDL L/S 5um 推进至 2024年的 7层 L/S 5um,广泛应用在射频组件、光电集成、MEMS。相关技术已经进入量产阶段,为国内众多合作企业和科研机构提供了高效代工服务。

图源:厦门云天

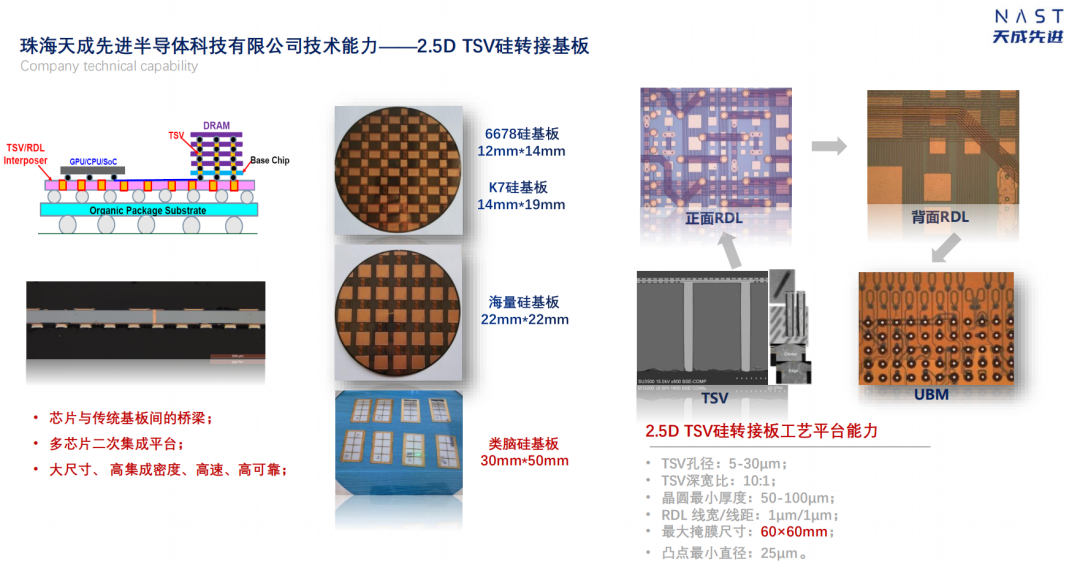

珠海天成先进半导体技术能力上,2.5D TSV硅转接基板上,集成产品 RDL L/S可做到 3μm,正面4层RDL,硅基TSV转接板最大尺寸30×50mm,可实现GPU、CPU、多层存储器的高密度、高速、高可靠集成;在3D TSV 堆叠可实现8层RDL L/S 1μm;且可以实现芯片晶圆直接加工TSV互连、TSV硅转接基板堆叠、多芯片TSV晶圆埋置堆叠。公司规划总投资超30亿元,其中一期总投资约16.5亿元,可实现年产24万片12英寸TSV立体集成晶圆产品,于2024年底实现通线。

图源:天成先进

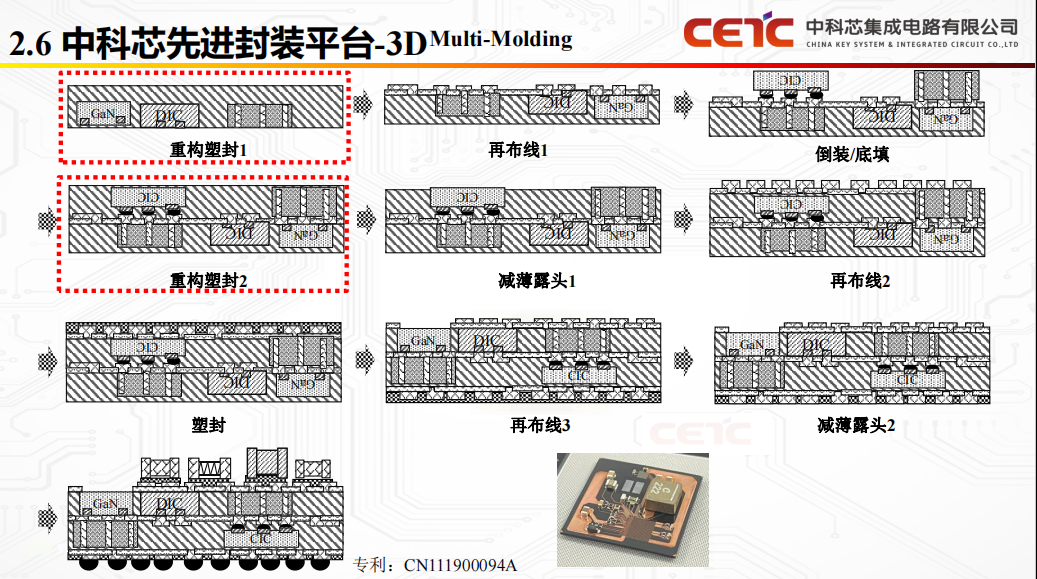

芯德科技是一家快速成长的半导体高端封测科技新锐。拥有高密度重布线扇出结构FOCT-R技术平台,实现了同质异质芯片间的互连;并且可以整合两种具有不同特点的基板:高层数的基板,更精密的再布线转接板(RDL Interposer);还可以进一步实现更大的2.5D封装,并降低基板层数。使用再布线和凸块技术,实现最小2μm的线宽,2um间距的布线。芯德科技推出单芯片HPFO技术,采用Interposer来有效降低基板的制造层数。目前公司实现QFN、CSP、LGA/SIP、FCBGA、FCCS的量产。公司Chiplet扬州工厂预计2024年完工;10月份,芯德科技完成6元融资持续助力CHIPLET等高端封测领域布局。

青岛新核芯 Hyper 2D是一种新封装结构进行异质整合,优势在于此结构无需制备TSV interposer可使成本更具竞争力,其线宽限距可达2/2 um以下。主要制程均制作于载体基板上,可以压缩制作时间并控制其良率,大大提升生产效率。另有FOStrip 新型扇出型封装技术,轻薄短小、性能好、散热佳,封装厚度减薄到0.6 mm以下,同时金属线的跨距制作能力微缩到5um。

图源:青岛新核芯

中科智芯产品主要集中在晶圆凸点/芯片规模封装(WLCSP,Bumping)、扇出型封装(Fanout WLP)、系统集成、三维堆叠封装以及晶圆测试等高端封测业务。一期规划两个厂的晶圆级封装产能为月产>3万片。实现重布线层与层、芯片之间高精度对位是公司晶圆级封装的四大关键技术之一,晶圆级扇入封装的重布线宽/线距 ≥ 5um/5um。

图源:中科芯

中科芯晶圆级封装解决方案上,针对RDL向内再布线,封装体尺寸等于原来芯片尺寸,I/O数量一般小于200个;针对扇出型封装RDL可以同时向内/向外布线,封装体尺寸大于原芯片尺寸,I/O数量可达10000个左右。目前,中科芯初步具备CoWoS-R工艺能力,RDL First,4P5M布线,最小线宽线距10μm,5层RDL,已开始生产相关产品。拥有自主JY12英寸晶圆级扇出型先进封装工艺线。从市场导入到产品交付,全周期质量管控,具备一站式先进封装代工服务能力。

盛合晶微以先进的12英寸高密度凸块和再布线加工起步,致力于提供中段硅片制造和测试服务,SmartAiP是世界首个超宽频双极化的5G毫米波天线芯片晶圆级集成封装工艺,融合了多层双面再布线(RDL)技术。3DFO是SmartPoser技术平台衍生出的晶圆级系统集成技术,具有高密度RDL和TIV特性。公司实现了近存计算芯片大尺寸全RDL走线封装结构的量产。成品尺寸达到1600mm²,采用了盛合晶微4层RDL再布线加工工艺。

审核编辑:刘清

-

传感器

+关注

关注

2578文章

55516浏览量

793996 -

芯片设计

+关注

关注

15文章

1172浏览量

56780 -

IC封装

+关注

关注

4文章

196浏览量

27724 -

MEMS器件

+关注

关注

2文章

55浏览量

13342 -

图形处理器

+关注

关注

0文章

202浏览量

27571

原文标题:先进封装技术之争 | RDL线宽线距将破亚微米,赋能扇出封装高效能低成本集成

文章出处:【微信号:封装与高速技术前沿,微信公众号:封装与高速技术前沿】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

两种高效能电源设计及拓扑分析

中小车企 ASPICE 落地实战:低成本高效能研发体系搭建

高效能V系列新品:锁定1000流明以下商业与住宅照明市场

功率级低成本高效功率窃取设计方案

PCB设计中线宽线距的重要性

Manz亚智科技RDL制程打造CoPoS板级封装路线, 满足FOPLP/TGV应用于下一代AI需求

Manz亚智科技RDL制程打造CoPoS板级封装路线,满足FOPLP/TGV应用于下一代AI需求

RDL线宽线距将破亚微米赋能扇出封装高效能低成本集成

RDL线宽线距将破亚微米赋能扇出封装高效能低成本集成

评论