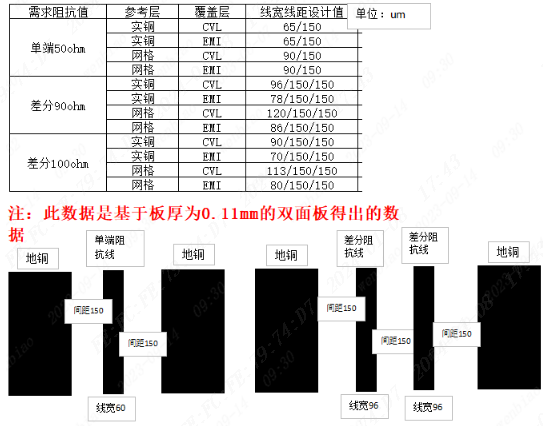

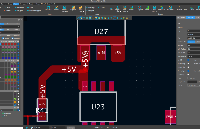

PCB一般板厂用SI9000来计算阻抗,但FPC我用SI9000模拟了几次都不准,刚好*** FPC可以免费打样了,后面就直接打样,用TDR方式测出阻抗,再打切片测量铜厚,基材厚度,线宽线距,反推再修正的方式,整了3次才把阻抗线宽及线距整出来,结果如下:

注:CVL表示只贴了阻焊膜,EMI表示是贴了屏蔽膜的,另外屏蔽膜是接了地的,如果不接地会有影响

以上数据是基于FPC板厚0.11mm,基材PI厚度25um,铜厚12um(成品铜厚15-18um)的,不同基材会有所不同,数据仅供参考,需要打样验证!

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

阻抗

+关注

关注

17文章

983浏览量

48751 -

FPC

+关注

关注

72文章

1008浏览量

66802 -

PCB

+关注

关注

1文章

2264浏览量

13204

发布评论请先 登录

相关推荐

热点推荐

揭秘PCB设计生死线:走线宽度、铜厚与温升如何决定电流承载力?

一站式PCBA加工厂家今天为大家讲讲PCB走线与过孔的电流承载能力有受什么影响?PCB走线与过孔的电流承载能力的影响因素。PCB走线与过孔的电流承载能力受线宽、铜厚、温升、层别及散热条

华秋DFM软件丨操作教程——工具菜单-阻抗计算篇

值 ,再选择 阻抗层 ,找到阻抗对应的模板,再输入 原始线宽线距 ,如参考层特别比如隔层参考,需要手动选择参考层。

② 参数输入完毕后点击

发表于 08-27 19:13

lcr阻抗仪与TDR阻抗仪有什么区别吗?

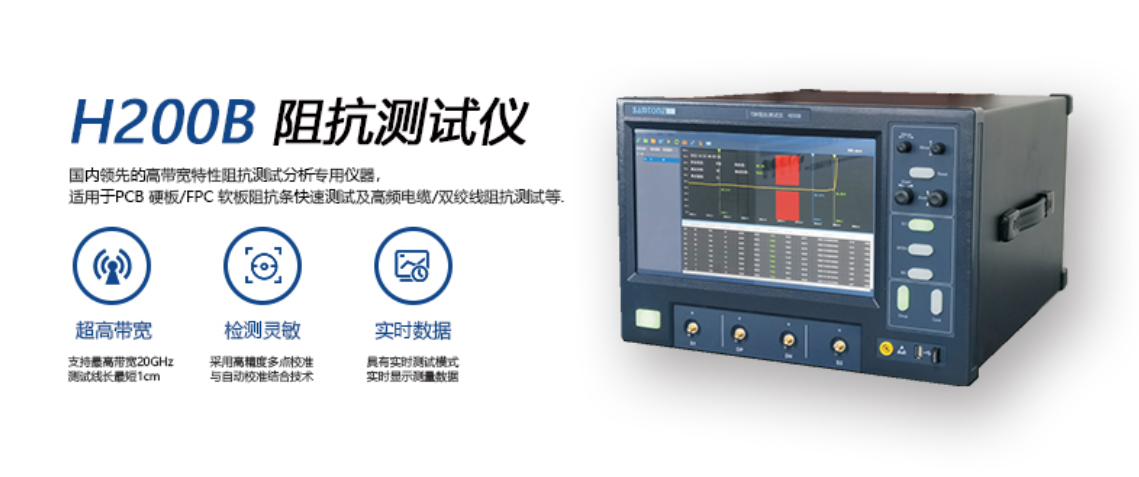

测量范围的限制,LCR测试仪在高频段的测量能力有限。 而TDR阻抗测试仪,如班通(Bamtone)H系列,则是基于时域反射原理(TDR)设计而成的高带宽特性阻抗测试分析专用仪器。主要应用于高频范围内的阻抗测试,如PCB硬板、

FPC如何重塑现代蓝牙耳机设计与性能

日常使用中的冲击与振动,提升连接可靠性和产品寿命。

5.简化组装,提高良率: FPC通常作为一个整体模块进行安装,减少了传统飞线焊接的点位和复杂度,降低了组装难度和潜在故障点,提高了生产效率和一致性

发表于 07-04 11:47

Allegro Skill布线功能之调整差分的线宽线距

在进行高速PCB设计的过程中,当PCB板的叠层结构发生变化时,为了保持信号的完整性,我们不得不对高速信号线的线宽进行相应的调整。那么这种调整是必要的,因为不同的叠层结构会对信号的阻抗产生影响。手动去

Allegro Skill布线功能之改变线宽介绍

会对信号的阻抗产生影响。手动去逐一更改这些高速信号线的线宽是一项非常繁琐且耗时的工作,它不仅不能提高我们的设计效率,反而会因为工作量巨大而降低整体的设计效率。

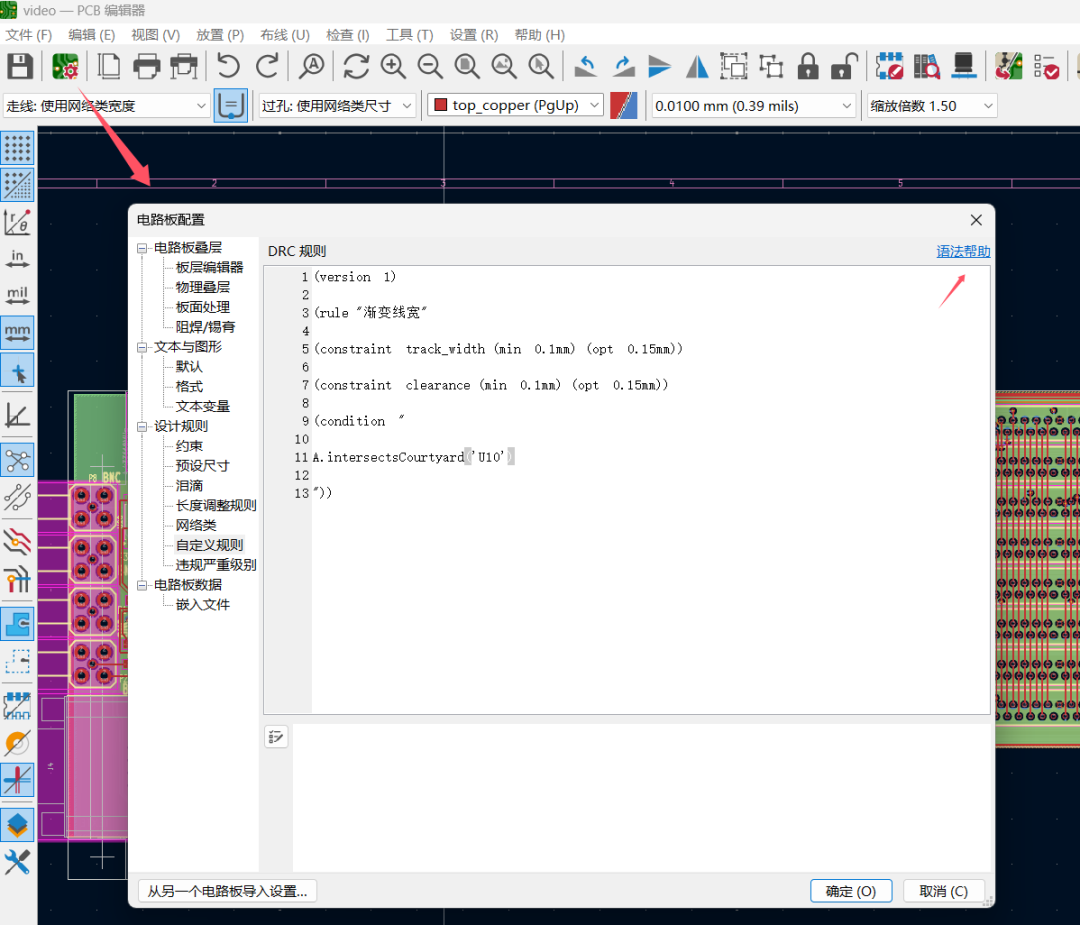

如何在特定区域设置线宽、线距规则

“ 今天偷个懒,分享一个 Hayden 大佬提供的自定义规则,非常实用。可以在特定区域(如BGA器件范围内)定义特殊的线宽、线距规则。 ” 就是下面这段自定义规则,表示 U10

PCB走线,盲目拉线,拉了也是白拉!

布置在阻抗控制层上,须避免其信号跨分割。

2、 布线窜扰控制

a) 3W原则释义

线与线之间的距离保持3倍线宽。是为了减少线间串扰,应保证线间距足够大,如果

发表于 03-06 13:53

从定位到质检:传感器如何重塑FPC裁切与AOI检测的精度边界?

生产效率和产品质量。凭借深厚的技术积累和创新能力,明治针对3C行业设备提出智能升级解决方案,旨在全面提升厂商自动化、智能化水平。↓随着FPC线宽/线距向50μm以

DLPC3478 RGB FPC长度最大可以达到多少?

如果在我们这类应用下FPC长度最大可以达到多少?规格书上是否由关于该内容的描述如果有,麻烦请指出。

2,RGB 时钟信号150MHZ,单端是否也有阻抗要求?

3,FPC如果我们自己设计是否需要一个完整的参考GND?

发表于 02-18 07:56

把ADS850的数据接口和时钟信号通过FPC线连接至FPGA,当FPC线缆大于5cm,会导致丢位,错位现象,怎么处理?

之前把ADS850的数据接口和时钟信号通过FPC线连接至FPGA,发现当FPC线缆大于5cm(10cm,12cm,15cm)时,采样值为01 1111 1111 1111到10 0000 000

发表于 02-11 07:27

传输线特征阻抗是设计中最重要的因素

,从电池吸收恒定的电流,传输线就等同于一个电阻,并且阻值恒定。我们称之为传输线的浪涌阻抗。

同样,当信号沿传输线向前传播时,每传播一定的距离,信号会不断地探查信号

发表于 01-21 07:11

TUSB8041的阻抗怎么计算?

根据官网给的手册画好了pcb连线的时候,发现USB有些需要差分信号线,但是官网数据手册上只是写了必须设计阻抗在90欧姆左右,并不是很了解怎么计算,希望大佬给点提示,线宽和线

发表于 12-16 06:05

FPC阻抗线宽线距参考

FPC阻抗线宽线距参考

评论