了解高频半导体器件各个元件之间的电磁 (EM) 耦合对于满足设计规范和确保现场可靠运行至关重要。这些电磁相互作用不仅包括硅芯片,还延伸到封装它的封装。然而,可能只有在项目接近尾声时,IC或系统设计人员才能创建和仿真同时包含片上金属和封装层的EM模型。在片上金属模型中加入封装层会导致性能下降,从而导致违反规范的情况并不少见。为了避免这种情况,Ansys提供了一种解决方案,可以轻松地将封装层添加到硅技术的金属堆叠中,以便在设计过程的早期提取具有片上层和封装层的完整模型。

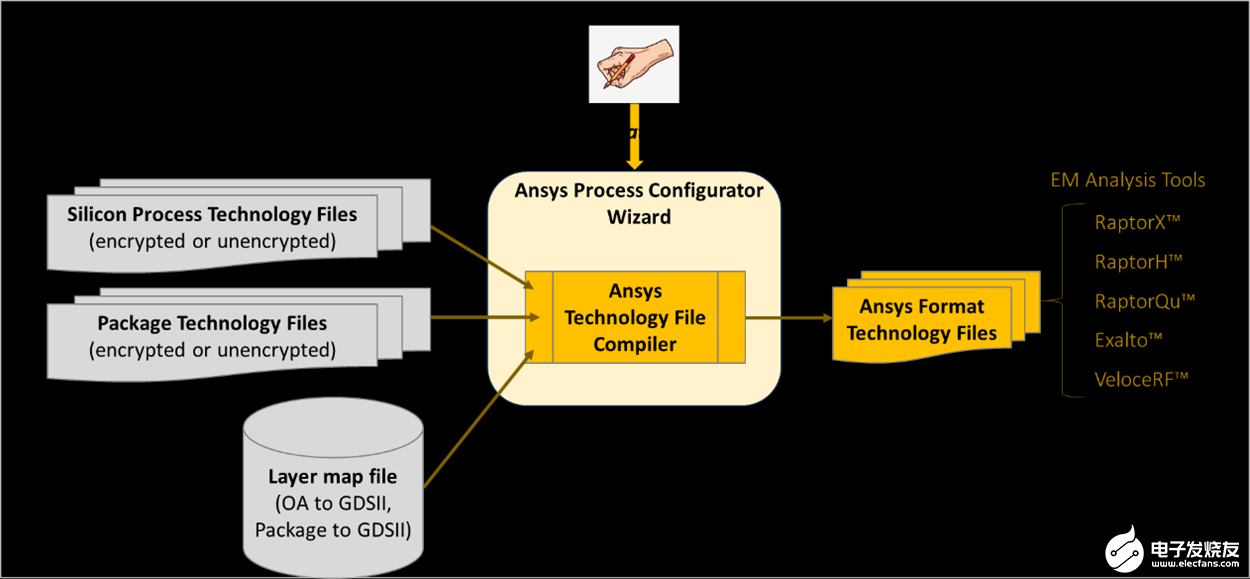

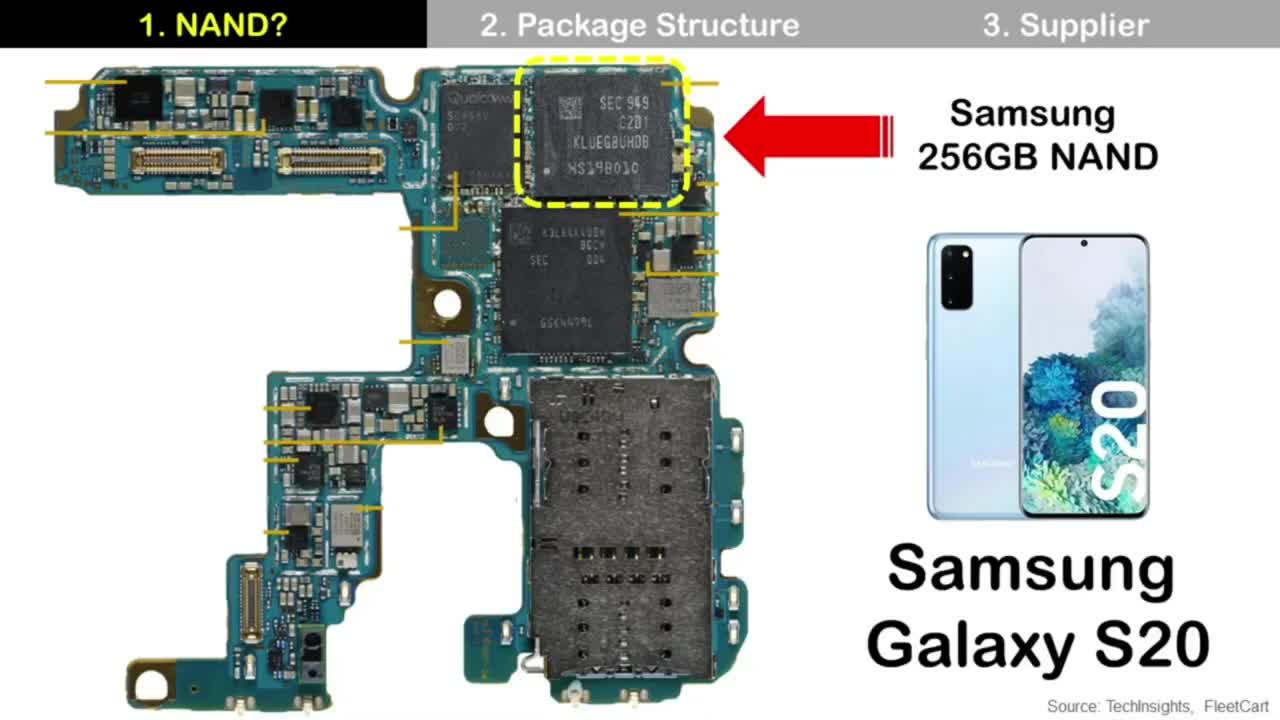

Ansys的片上电磁分析工具套件可在LVS前设计阶段(Ansys RaptorX™)和LVS后签核阶段(Ansys Exalto™)的IC布局上运行。芯片分析可以包括部分封装布局和/或封装层,以提取完整的EM模型,该模型可以使用SPICE电路仿真器进行仿真。Ansys工具依赖于有关每层制造中使用的互连工艺技术的精确信息。硅晶圆代工厂以各种格式提供工艺信息,包括设计规则手册(DRM)和技术文件(如iRCX、ITF和ICT文件),这些文件可能是未加密的,也可能是加密的。捕获技术堆栈的过程通过将晶圆代工厂提供的工艺技术信息映射到OpenAccess或GDSII流格式的物理布局信息上,编译一系列Ansys格式的技术文件(见图1)。这些编译的技术文件还支持其他Ansys片上EM工具,包括AnsysVeloceRF™(电感器件布局综合)和Ansys RaptorQu™(用于超导量子设计)。

RaptorX是一款硅优化的电磁求解器,它带有一个非常有用的向导,称为Process Configurator,可以轻松创建和修改Ansys技术文件,即使对于复杂的芯片封装配置也是如此。如图1所示,Process Configurator创建的Ansys技术文件可以仅包含晶圆代工厂金属叠层,也可以包含晶圆代工厂金属叠层以及选定的附加封装层。铸造厂金属堆叠的工艺配置器向导的输入是铸造厂提供的工艺信息。如果需要共提取裸片层和封装层,则还需要包含目标层的封装层信息。

图1:Ansys Process Configurator向导使设计人员能够轻松控制芯片封装配置,并实现假设分析

如果晶圆代工技术文件未加密,或者封装层信息未加密,则Process Configurator向导将允许您通过编辑芯片和/或封装层的属性并编译不同版本的Ansys技术文件来探索各种与工艺相关的“假设”场景。工艺配置器允许设计人员添加或减少基板、背板、导体、电介质和通孔,包括硅通孔 (TSV)。可以使用 Process Configurator 编辑的技术属性包括金属厚度、金属电导率、介电厚度和介电常数。为了完成Ansys技术文件,编译器还需要GDS流层映射文件和层映射信息。

为“假设”实验修改未加密技术的一些示例包括:

修改基板厚度和性能,以探索通过基板耦合的影响

在探索性 3DIC 堆叠中添加 TSV

为晶圆上晶圆 (WoW) 技术设置技术文件

添加封装层以查看它们对 EM 设备的影响 - 如以下示例所示

Process Configurator 的输入文件和信息可以使用 UI 和批处理模式命令脚本进行处理。Process Configurator的输出是Ansys EM工具套件使用的已编译的Ansys过程技术文件。Process Configurator 具有非常有用的功能,可以可视化技术横截面,从而轻松验证技术层的正确顺序和连通性。未加密的技术层属性(如厚度、电阻率和介电常数)也会显示在横截面查看器中。如果该技术是加密的,则横截面查看器会显示层序列和连通性,但层厚度不会缩放,并且不会报告材料属性。

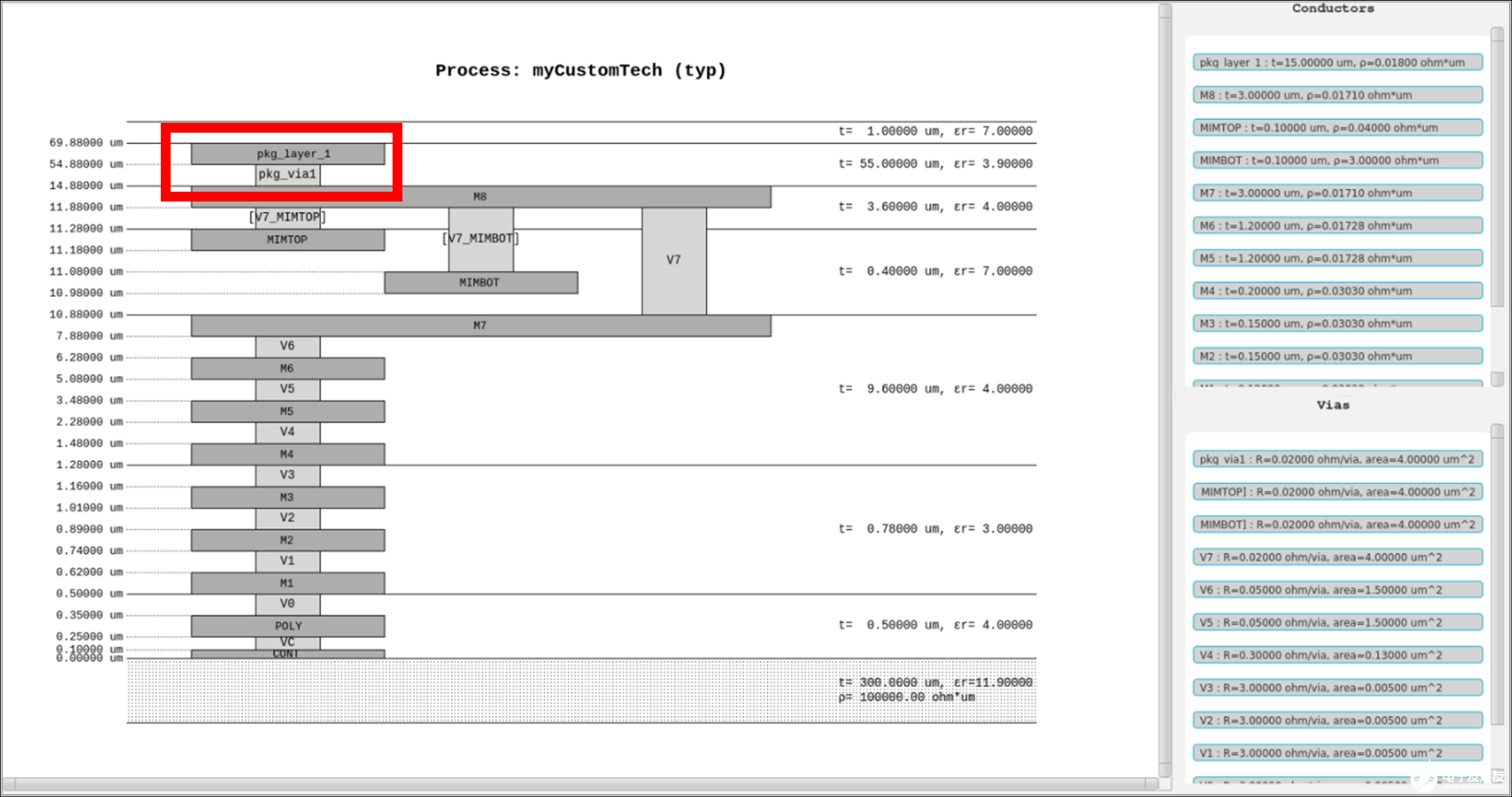

下面的图 2 显示了一个虚构的示例技术文件的堆叠。左图显示底层的衬底特性、从衬底开始的累积层高、左侧的层和通孔名称,以及介电厚度和介电常数(er) 在右边。右面板中的导体部分列出了导体的厚度和电阻率 (r),过孔部分显示了通孔电阻和面积。

图 2:Process Configurator 显示未加密的硅堆叠示例,其中报告了所有参数,并按比例显示了导体厚度

下面图 3 中的红色框突出显示了已添加到堆叠中的通孔层和封装层。这种叠加(包括封装层和通孔)用于以下段落中描述的仿真结果,这些段落显示了封装层如何影响 EM 器件的性能。

图 3:未加密的芯片堆叠示例,其中添加了红色框中突出显示的封装层

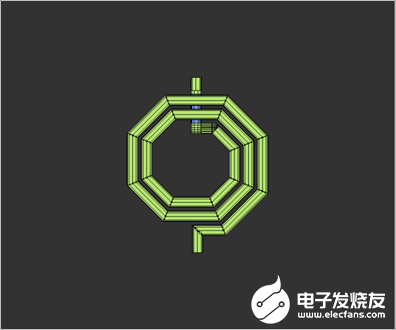

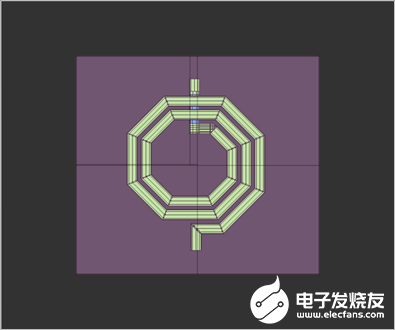

为了说明如何使用Process Configurator来探索封装对芯片的影响,我们创建了一个简单的布局示例:它由一个EM器件(一个单端八角形螺旋电感器)组成,该器件是使用RaptorX提取的。然后,在SPICE级电路仿真器中对得到的电气模型进行仿真,以分析性能,然后首先在其上方放置封装层,然后再次不使用封装层。下面的图4显示了RaptorX的物理网格,用于不带封装层的电感器。

图4:Ansys RaptorX的无封装层电感器物理网格

接下来,使用相同的电感器,但在其上方放置了一个矩形的封装层。下面的图 5 显示了包含封装层的电感器的 RaptorX 网格。

图5:Ansys RaptorX的电感物理网格,包括覆盖封装层

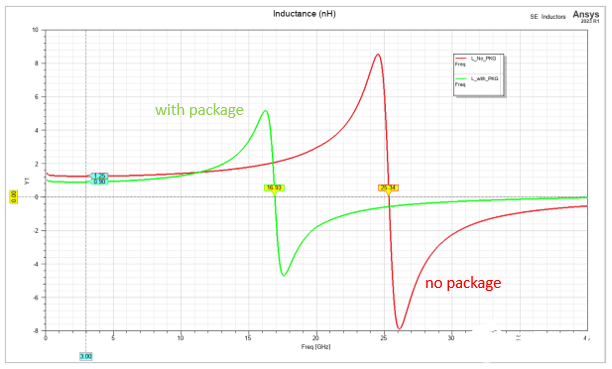

RaptorX为每个电感器生成了一个S参数模型,然后对整个频率范围内的电感和品质因数进行了仿真。图6显示了两个电感器在整个频率范围内的电感。比较封装层(绿色)在3 GHz时的电感图,与没有封装层的模型(红色)的仿真结果相比,电感降低了28%,谐振频率降低了33%。

图 6:电感频率变化图,显示了在仿真中添加封装层的显著影响

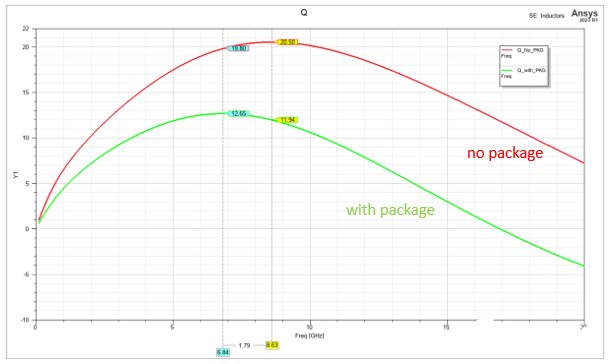

在下面的图7中,两个电感器的质量因数(Q)绘制了整个频率。比较所包含封装层(绿色)的 Q 仿真图,与没有封装层(红色)的模型的仿真结果相比,最大 Q 值降低了 38%,最大 Q 峰值频率降低了 21%。

图 7:质量因数与频率的关系图,显示了在仿真中添加封装层的显著影响

总之,这些仿真结果说明了在仿真中包含封装层时所看到的器件行为的明显变化。对封装层和片上金属进行建模可以揭示性能下降,这可能会违反规范或导致器件故障。Ansys开发了Process Configurator,使IC和系统设计人员能够非常轻松地捕获最复杂的多层封装配置,并促进快速实验。它鼓励采用左移方法,并进行早期的假设探索,以帮助设计人员找到优化最终产品的最佳解决方案,并避免后期的意外。

审核编辑:黄飞

-

IC

+关注

关注

36文章

6471浏览量

186315 -

电感器

+关注

关注

20文章

2651浏览量

73925 -

芯片设计

+关注

关注

15文章

1171浏览量

56775 -

晶圆代工

+关注

关注

6文章

883浏览量

49821 -

电磁耦合

+关注

关注

2文章

30浏览量

13648

发布评论请先 登录

电源模块的可靠性设计有何秘籍?

封装对高频芯片设计有何影响吗?

封装对高频芯片设计有何影响吗?

评论