SPI有四种工作模式

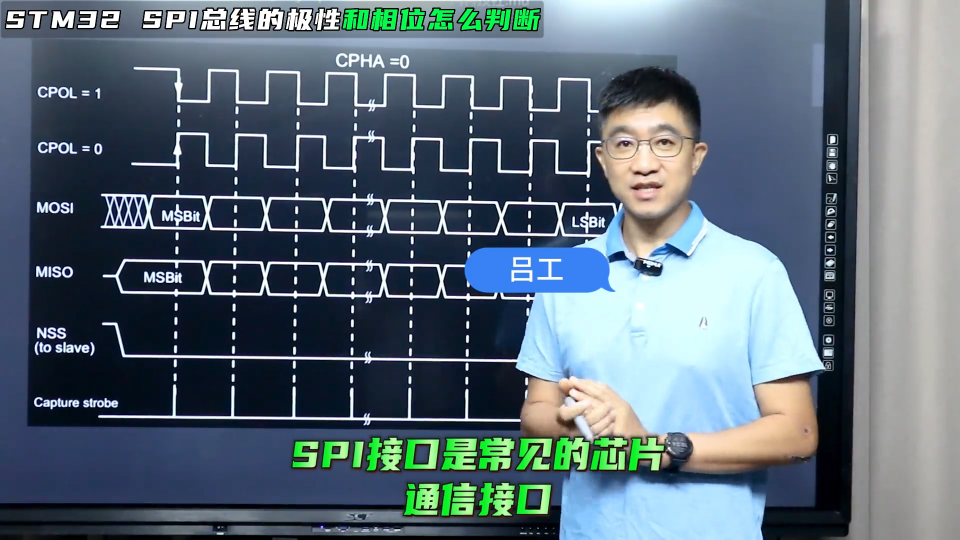

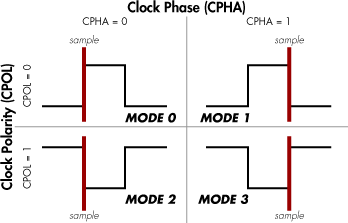

SPI(Serial Peripheral Interface)总线有四种工作模式,这些模式通过配置时钟极性(CPOL)和时钟相位(CPHA)来确定数据传输的时机和方式。以下是这四种工作模式:

1. 模式0(CPOL = 0,CPHA = 0):时钟空闲状态为低电平(0),数据在时钟的下降沿采样和/或输出。这意味着数据在时钟的上升沿进行采样,数据在时钟的下降沿进行输出。

2. 模式1(CPOL = 0,CPHA = 1):时钟空闲状态为低电平(0),数据在时钟的上升沿采样和/或输出。这意味着数据在时钟的下降沿进行采样,数据在时钟的上升沿进行输出。

3. 模式2(CPOL = 1,CPHA = 0):时钟空闲状态为高电平(1),数据在时钟的上升沿采样和/或输出。这意味着数据在时钟的下降沿进行输出,数据在时钟的上升沿进行采样。

4. 模式3(CPOL = 1,CPHA = 1):时钟空闲状态为高电平(1),数据在时钟的下降沿采样和/或输出。这意味着数据在时钟的上升沿进行输出,数据在时钟的下降沿进行采样。

这些模式允许SPI设备和主设备在不同的时钟极性和时钟相位条件下进行数据传输。根据特定的SPI设备和应用需求,可以根据其规范配置适当的工作模式。

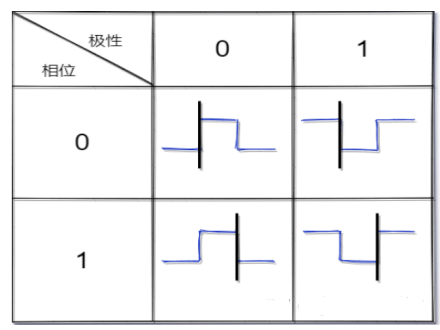

SPI相位和极性

SPI有四种工作模式,取决于相位(CPHL)和极性(CPOL)两个因素。CPOL表示时钟线在空闲时候的状态

CPOL=0: SCLK在空闲时属于低电平状态CPOL=1: SCLK在空闲时属于高电平状态CPHA表示采样时刻

CPHA=0:表示每个周期的第一个时钟沿采样

CPHA=1:表示每个周期的第二个时钟沿采样

优点:相比于IIC而言,传输速率快,且数据传输灵活,拥有独立的数据线,双方可以同时收发数据。缺点:需要占用更多的硬件资源,没有应答信号,不能对传输的数据做检查。

spi总线一般使用几条线分别是什么

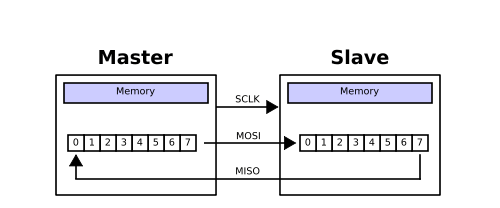

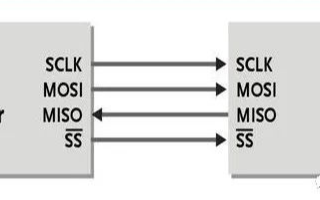

SPI(Serial Peripheral Interface)总线通常使用4条线进行连接,这些线分别是:

1. 主时钟线(SCK):主设备通过该线发送时钟信号,用于同步数据传输。

2. 主输出/从输入线(MOSI):主设备通过该线发送数据给从设备。

3. 主输入/从输出线(MISO):从设备通过该线将数据发送给主设备。

4. 片选线(SS):用于选择和启用与主设备通信的特定从设备。片选线为每个从设备提供一个独立的信号线。

SPI总线可以灵活配置,可以根据具体需要增加或减少信号线的数量。例如,一些SPI设备可能不需要使用片选线(SS),因为它们只与一个主设备通信,而其他设备可能需要使用多个片选线以支持与多个主设备的通信。

审核编辑:黄飞

-

数据传输

+关注

关注

9文章

2082浏览量

67200 -

SPI

+关注

关注

17文章

1867浏览量

99949 -

总线

+关注

关注

10文章

3017浏览量

91338 -

SPI总线

+关注

关注

4文章

106浏览量

28374

发布评论请先 登录

SPI总线小结

SPI中的极性CPOL和相位CPHA介绍

SPI总线概述

浅谈SPI总线

AD7606 SPI通信的时钟极性和时钟相位要求是什么?

SPI总线接口与简单配置

SPI时钟极性和时钟相位

SPI总线的相位和极性

SPI总线的相位和极性

评论