什么是锁相环

锁相环 (PLL) 是电子系统中最通用、最灵活和最有价值的电路配置之一,因此在许多应用中都有使用。它用于时钟重定时和恢复,作为频率合成器和可调谐振荡器,仅举几个例子。

因此,在包括无线电接收器和测试设备在内的许多 RF 设备项目中都可以找到 PLL。根据其具体实现,它可以服务于近直流到 GHz 和更高的频率,在系统和电路中发挥许多关键作用。

锁相环的工作原理

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

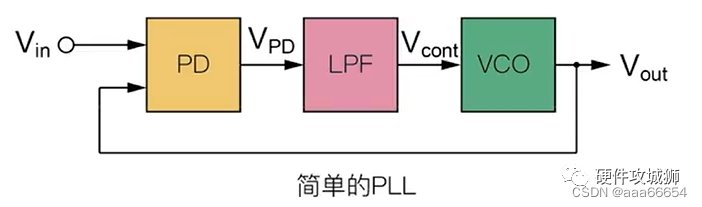

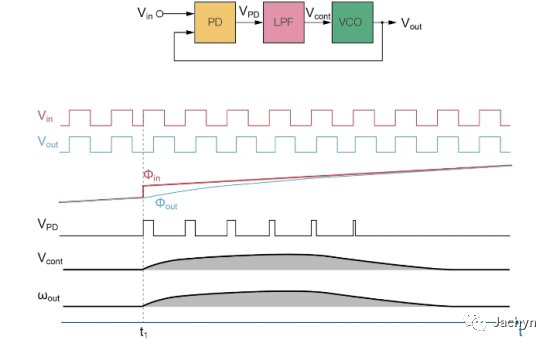

最基础的锁相环系统主要包含三个基本模块:鉴相器(Phase Detector:PD)、环路滤波器(L00P Filter:LF)其实也就是低通滤波器,和压控振荡器(Voltage Controlled Oscillator:VCO)。有了这三个模块的话,最基本的锁相环就可以运行了。但我们实际使用过程中,锁相环系统还会加一些分频器、倍频器、混频器等模块。(这一点可以类比STM32的最小系统和我们实际使用STM32的开发板)

图 锁相环基本模块

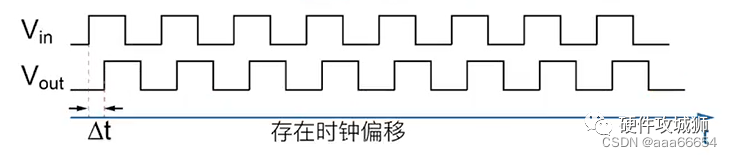

图 输入信号和输出信号存在相位差

锁相环的应用

锁相环在调制和解调中的应用

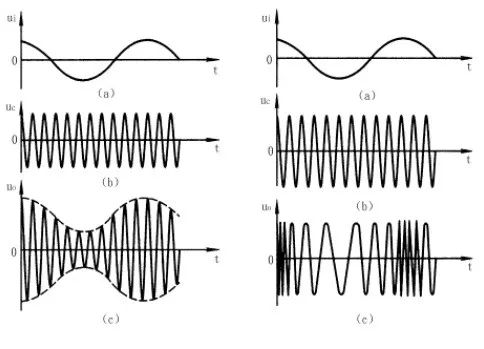

所谓的调制就是用携带信息的输入信号ui来控制载波信号uc的参数,使载波信号的某一个参数随输入信号的变化而变化。载波信号的参数有幅度、频率和位相,所以,调制有调幅(AM)、调频(FM)和调相(PM)三种。

调幅波的特点是频率与载波信号的频率相等,幅度随输入信号幅度的变化而变化;调频波的特点是幅度与载波信号的幅度相等,频率随输入信号幅度的变化而变化;调相波的特点是幅度与载波信号的幅度相等,相位随输入信号幅度的变化而变化。调幅波和调频波的示意图如图8-4-4所示。

上图的(a)是输入信号,又称为调制信号;图(b)是载波信号,图(c)是调幅波和调频波信号。

解调是调制的逆过程,它可将调制波uo还原成原信号ui。

锁相环在频率合成电路中的应用

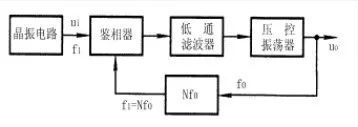

在现代电子技术中,为了得到高精度的振荡频率,通常采用石英晶体振荡器。但石英晶体振荡器的频率不容易改变,利用锁相环、倍频、分频等频率合成技术,可以获得多频率、高稳定的振荡信号输出。

输出信号频率比晶振信号频率大的称为锁相倍频器电路;输出信号频率比晶振信号频率小的称为锁相分频器电路。锁相倍频和锁相分频电路的组成框图如图8-4-7所示。

图中的N大于1时,为分频电路;N小于1时,为倍频电路。

锁相环PLL对相位阶跃的响应

Vpd 刚开始相位很大,脉冲比较长,后面逐渐变小,脉冲慢慢变短。

Vcont通过低通滤波器将信号变得缓和。

out会随着Vcont慢慢变化。

总之,锁相环电路是一种功能强大的信号处理电路,通过对输入信号与参考信号的相位比较、平滑处理、频率控制和分频等操作,实现对输入信号的同频且相位锁定的输出。锁相环电路在通信系统、数字信号处理和控制系统等领域具有广泛的应用前景。

-

调制解调

+关注

关注

0文章

76浏览量

22171 -

锁相环

+关注

关注

36文章

637浏览量

91316 -

振荡器

+关注

关注

28文章

4195浏览量

143206 -

频率合成器

+关注

关注

5文章

368浏览量

33910 -

PLL电路

+关注

关注

0文章

94浏览量

7146

发布评论请先 登录

LabVIEW锁相环(PLL)

锁相环(PLL)电路设计与应用

锁相环PLL学习记录

锁相环PLL学习记录

评论