(1)抖动,英文名称为"jitter”。

这个jitter,有很多种定义[1,2]。

在说明这几种定义之前,我们先来对时钟,也就是clock的周期做一个定义。

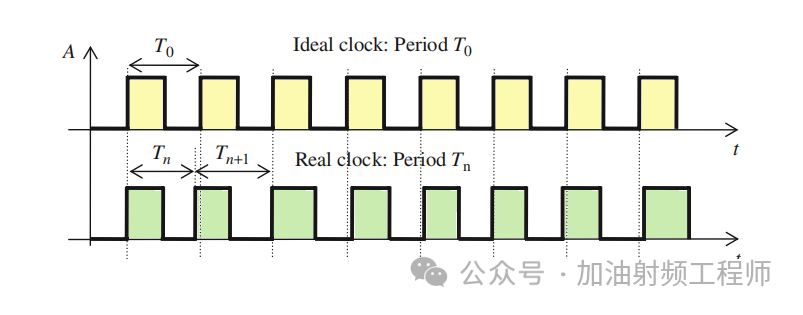

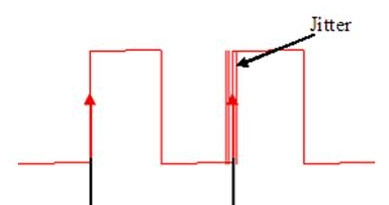

假设有一个理想的时钟,那它的周期是恒定的,记为T0。但是现实世界中的时钟是不理想的,这个不理想的时钟,每一个周期可能都不一样,记为Tn,如下图所示。

现在来说一下,那些各种各样定义的抖动。

第一种抖动,叫做period jitter,也称为cycle jitter.

它是不理想时钟的周期Tn与理想时钟的周期T0之间的差别,即:

第二种抖动,称为cycle-to-cycle jitter。

它是不理想时钟的周期Tn+1与Tn之间的差别,即:

第三种抖动,称为cumulative jitter。

cumulative jitter表示cycle jitter在经过N个周期后的累积。

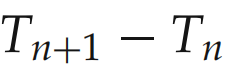

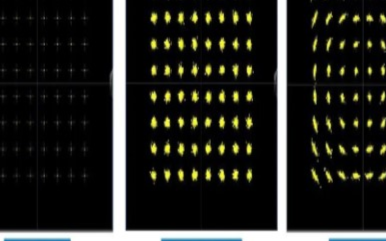

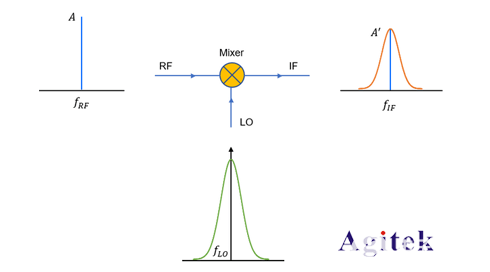

(2)但是,话说,对于射频工程师而言,或者说经常用相噪仪的射频工程师来说,看到的jitter,可能经常是RMS jitter,如下图所示。

那这个RMS jitter又是指啥?是上面三种抖动中的一种么?

呃,这个从[1,2,3]中,我推测,应该是指cumulative jitter。

在文献2中,有这样一段话,即:

从这段话,可以推出TIE和accumulated jitter等价。这个accumualted和上面的cumulative, 中文翻译过来,一个是积累,一个是累积,意思差不多吧。

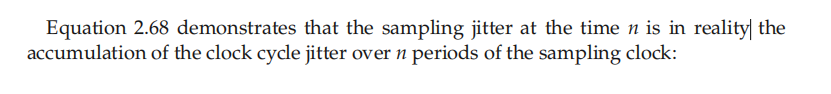

在文献1中,有这样一段话:

还有这样一幅图:

这文章中的推导,我读了3遍,还是云里雾里。不过总的来说,结论传达的意思,估摸着应该是这么一个意思。

Sampling jitter,实际上也是Phase jitter,或者Cumulative Jitter。

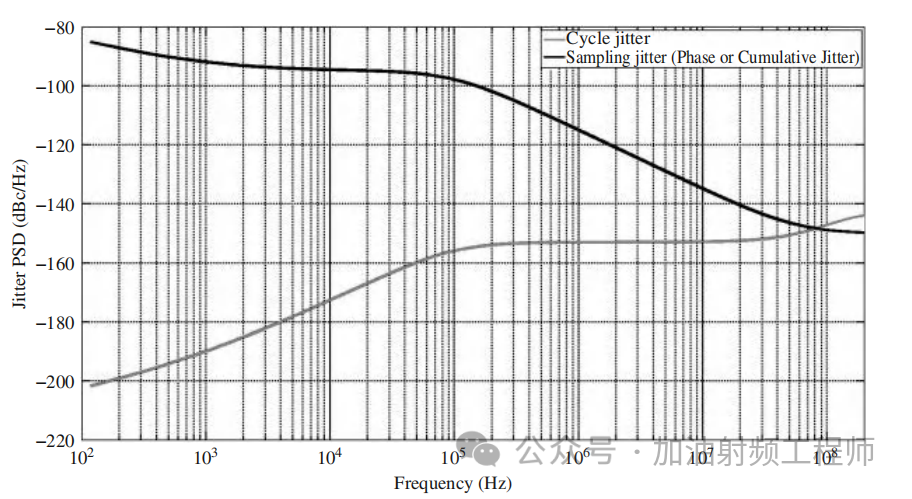

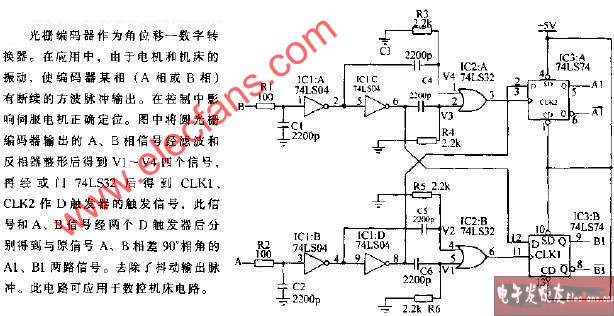

在文献[3]中,对TIE(Time Interval Error)的解释,如下图。

从这幅图来看,TIE和cumulative jitter的定义一致,cumulative jitter定义的是cycle jitter的累积,而cycle jitter=Tn-T0,也就是到n个时钟周期时,其时钟沿与理想时钟沿的差别。

(3)对于ADC来说,影响ADC的SNR的,则是sampling jitter[1]。

-

射频

+关注

关注

106文章

5944浏览量

172791 -

抖动

+关注

关注

1文章

70浏览量

19332 -

时钟

+关注

关注

11文章

1953浏览量

134547

原文标题:讨论_相噪仪上的抖动对应的是哪种抖动定义?

文章出处:【微信号:加油射频工程师,微信公众号:加油射频工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

时钟抖动和相噪及其测量方法

LMX2572改变功率配置字,相噪会发生变化,为什么?

HMC704底噪没有抖动的现象

LDO噪声对射频频综输出相噪的影响介绍

R&S推出超低灵敏度相噪分析和VCO测试仪R&S FSWP

相噪与时钟抖动测试方法

浅谈相噪仪上的抖动

浅谈相噪仪上的抖动

评论