1 月 4 日,澜起科技发布新款 DDR5 寄存时钟驱动器芯片(DDR5 RCD04),数据传输率高达 7200MT/s,比首代 RCD 提高 50%。

RCD 组件用于缓存内存控制器传来的指令信号等数据,DB 则负责缓存来自内存设备或 DRAM 的数据信号。它们结合使用可实现全部信号的缓存功能。单用 RCD 的内存模块为 RDIMM,再加 DB 的组合模式称为 LRDIMM。

据悉,澜起科技已向主流内存制造商提供 DDR5 RCD04 样品,以助力其推进新一代内存产品研发。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

控制器

+关注

关注

114文章

17646浏览量

190265 -

DRAM

+关注

关注

40文章

2373浏览量

188173 -

RCD

+关注

关注

1文章

111浏览量

29407

发布评论请先 登录

相关推荐

热点推荐

瑞萨电子推出第六代DDR5 RCD,传输速率达9600MT/s

电子发烧友网综合报道 日前,瑞萨电子宣布推出业界首款面向DDR5寄存双列直插式内存模块(RDIMM)的第六代(Gen6)寄存时钟驱动器(RCD

澜起科技推出支持9200 MT/s速率的DDR5时钟驱动器(CKD)芯片

澜起科技今日正式推出新一代DDR5时钟驱动器(CKD)芯片,该芯片最高支持9200 MT/s的数

速率最高达7200MT/s!澜起科技DDR5第四子代RCD芯片量产

电子发烧友网综合报道 2025年10月27日,澜起科技正式宣布,已完成DDR5第四子代寄存时钟驱动器芯片

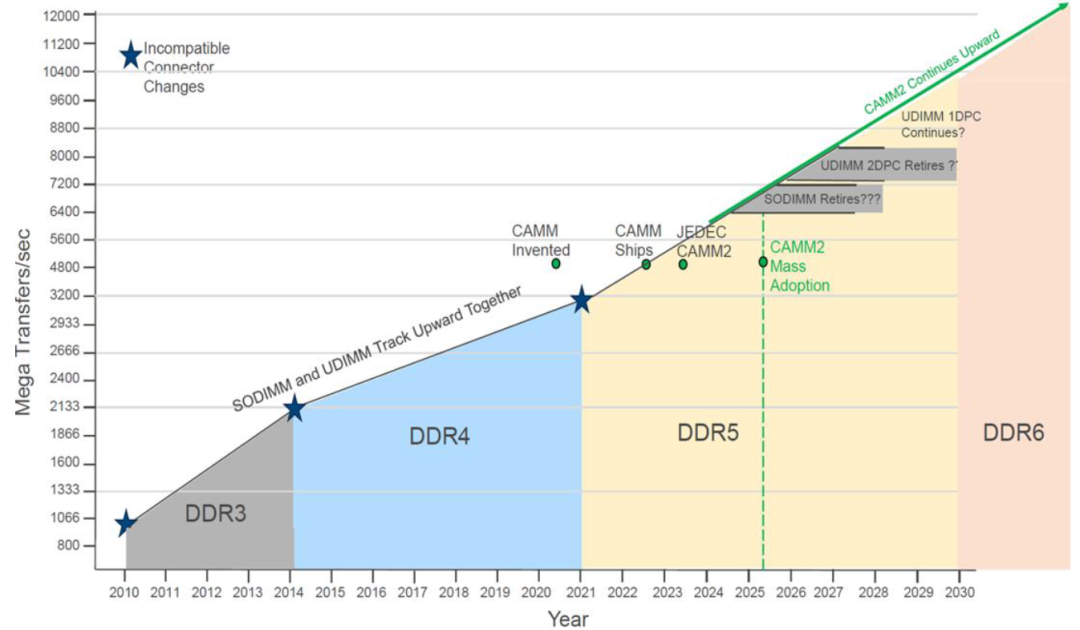

DDR5 设计指南(一):DDR5 VS LPDDR5

“ 本文将详细介绍 DDR5、LPDDR5 的技术细节以及 Layout 的规范要求。然后比较 CAMM2 模组与 SODIMM 的差别。 ” 本文将介绍什么是 DDR5,DDR5

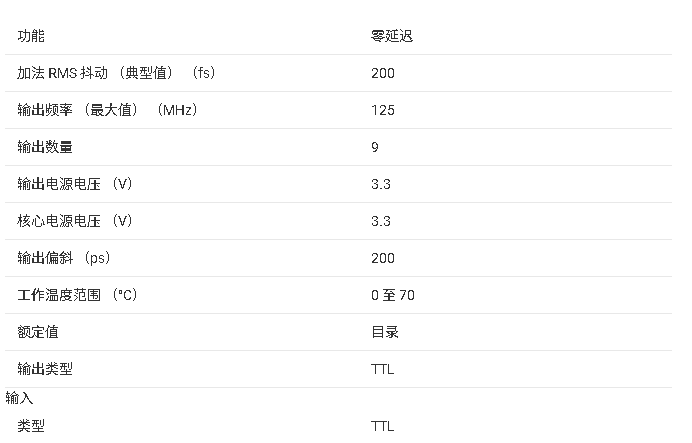

CDC509 3.3V相位锁定环时钟驱动器技术文档总结

CDC509 是一款高性能、低偏斜、低抖动、锁相环 (PLL) 时钟驱动器。它使用 PLL 在频率和相位上将反馈 (FBOUT) 输出精确对齐到时钟 (CLK) 输入信号。它专为与同步 DRAM 一起使用而设计。CDC509 的

CDCLVP215 低电压双差分1:5 LVPECL时钟驱动器技术文档总结

CDCLVP215时钟驱动器将两倍的一对差分时钟对LVPECL(CLKA、CLKB)分配给5对差分LVPECL时钟(QA0..QA4、QB0..QB4)输出,

精准时钟,驱动未来 ----澜起科技发布多款高性能时钟芯片

上海2025年8月8日 /美通社/ -- 澜起科技今日宣布,继时钟发生器芯片成功量产后,公司旗下时钟缓冲

威刚工控发布DDR5 6400高性能内存

产品均内置了先进的时钟驱动器(CKD)芯片,确保了数据传输的高速与稳定。同时,为了满足不同用户的需求,威刚提供了8GB、16GB与32GB三种存储容量选项,用户可以根据自己的实际需求进行选择。 在

澜起科技成功送样DDR5第二子代MRCD与MDB套片

近日,澜起科技宣布了一项重要研发进展:其自主研发的第二子代多路复用寄存时钟驱动器(MRCD)和第二子代多路复用数据缓冲器(MDB)套片,已成

澜起科技最新MRCD与MDB套片成功送样

澜起科技今日正式宣布,其最新研发的第二子代多路复用寄存时钟驱动器(MRCD)和多路复用数据缓冲器(MDB)套片,已经成功向全球各大内存厂商送

创见推出DDR5 6400 CUDIMM内存条

玩家及高效能工作需求者设计。它在标准DDR5 UDIMM的基础上导入了CKD客户端时钟驱动器芯片,原生支持更高传输速率,能有效减少数据传输延迟,特别适合需要更高带宽和稳定性的高性能桌面电脑系统。 对于游戏玩家来说,在运行大型3A

澜起科技成功送样DDR5第二子代MRCD和MDB套片

澜起科技今日宣布,其最新研发的第二子代多路复用寄存时钟驱动器(MRCD)和多路复用数据缓冲器(MDB)套片已成功向全球主要内存厂商送样。该套

澜起科技推RCD04 DDR5寄存时钟驱动器芯片

澜起科技推RCD04 DDR5寄存时钟驱动器芯片

评论