时钟XOR自门控(Self Gating)基本思路和时钟门控类似,都是当寄存器中的数据保持不变时,通过关闭某些寄存器的时钟信号来降低设计的动态功耗。不过XOR 自门控是利用异或门(XOR)将存储在寄存器中的数据与到达寄存器的数据引脚的数据进行比较,输出门控时钟使能信号。

在讲解XOR自门控之前,先回顾一下时钟门控(Clock Gating)技术的缺点。

时钟门控使用条件:

代码中有确定的门控时钟使能信号或者有门控时钟使能译码逻辑存在。比如下面代码中的EN信号:

input [n:0] D;

input CLK,EN;

output [n:0] Q;

always@ (posedge CLK)

begin

if (EN)

Q<=D;

end

时钟门控的缺陷:

从上面代码能看出,要想使用时钟门控技术,对代码风格有一定的要求,得有时钟门控信号。这可是硬伤,毕竟设计中不可能所有的寄存器都能找到这样逻辑,也不能保证所有写Verilog代码的人都有这样的觉悟。

因此,这就导致设计中有些寄存器组无法采用门控时钟技术。

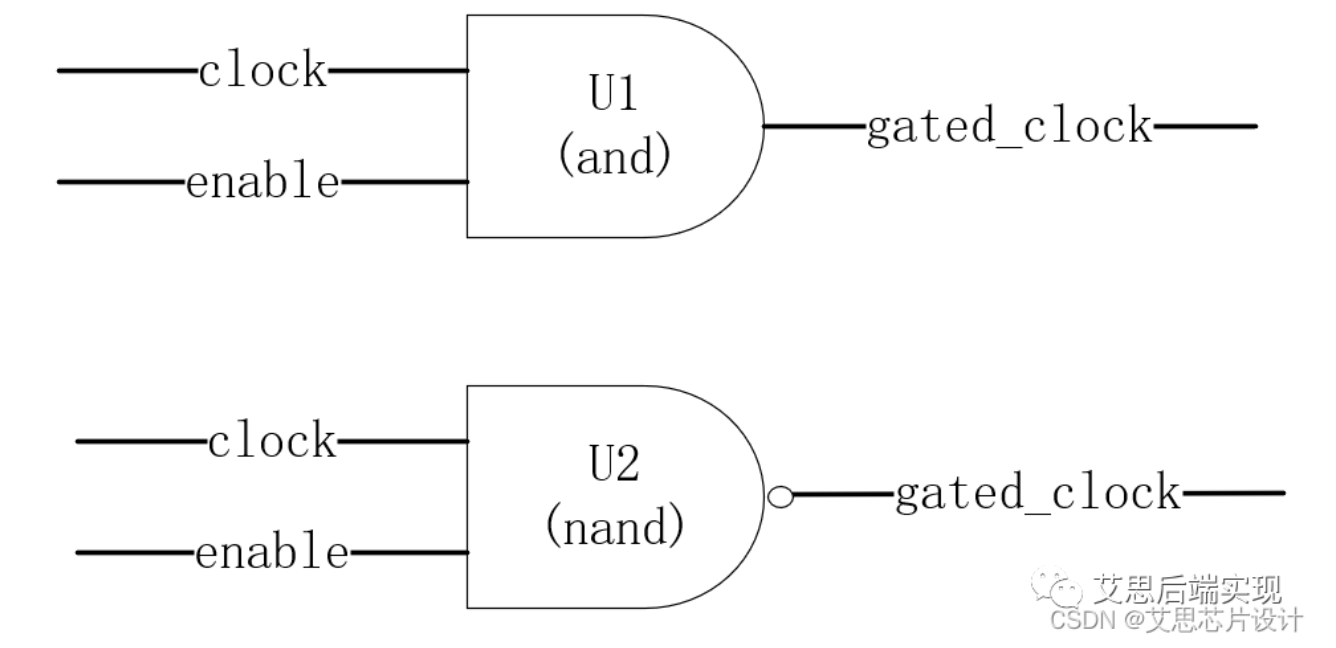

XOR自门控与时钟门控的不同之处:

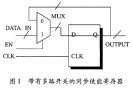

与时钟门控的不同之处在于,时钟门控技术依赖于现有设计中的使能条件,而XOR 自门控则利用异或门(XOR)将存储在寄存器中的数据与到达寄存器的数据引脚的数据进行比较,输出门控时钟使能信号。如果数据不变,则由异或门直接关断寄存器的时钟输入信号。下图显示了插入XOR自门控单元产生门控时钟使能信号的原理。

XOR自门控单元

XOR自门控的优点:

默认情况下,工具仅支持非门控时钟寄存器上的XOR自门控。

以下是XOR自门控的优点:

•有些情况,某些寄存器的使能条件无法从现有逻辑推断出,因此无法用传统的门控时钟技术来关断它们的时钟信号。这种情况下可以使用XOR自门控来关断它们的时钟信号;

•时钟门控和XOR自门控并不冲突,可以同时使用。对于那些已经采用门控时钟关断的寄存器,可以使用下面的命令允许在这些寄存器上采用XOR自门控:

set_self_gating_options

-interaction_with_clock_gating

采用了该技术之后,这些寄存器时钟信号的关断时间可能会增加。

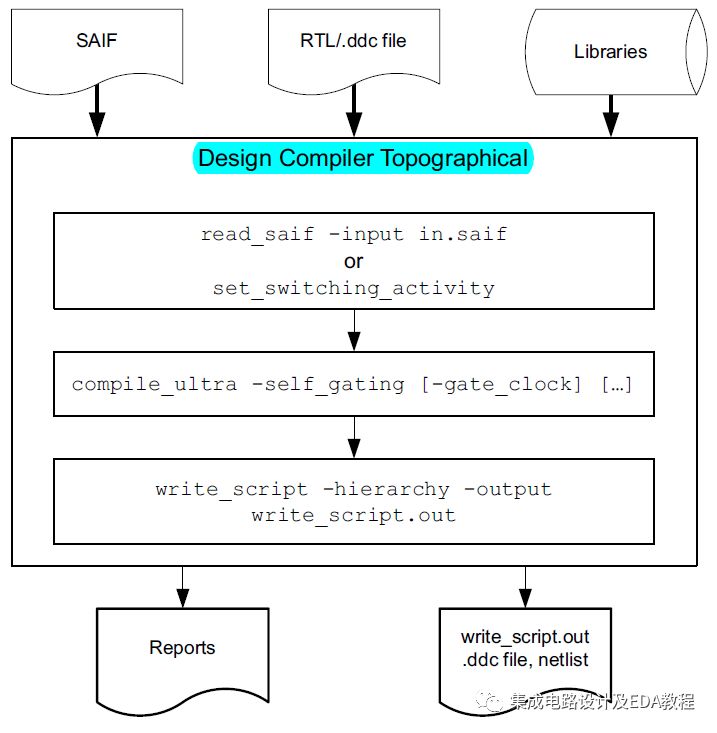

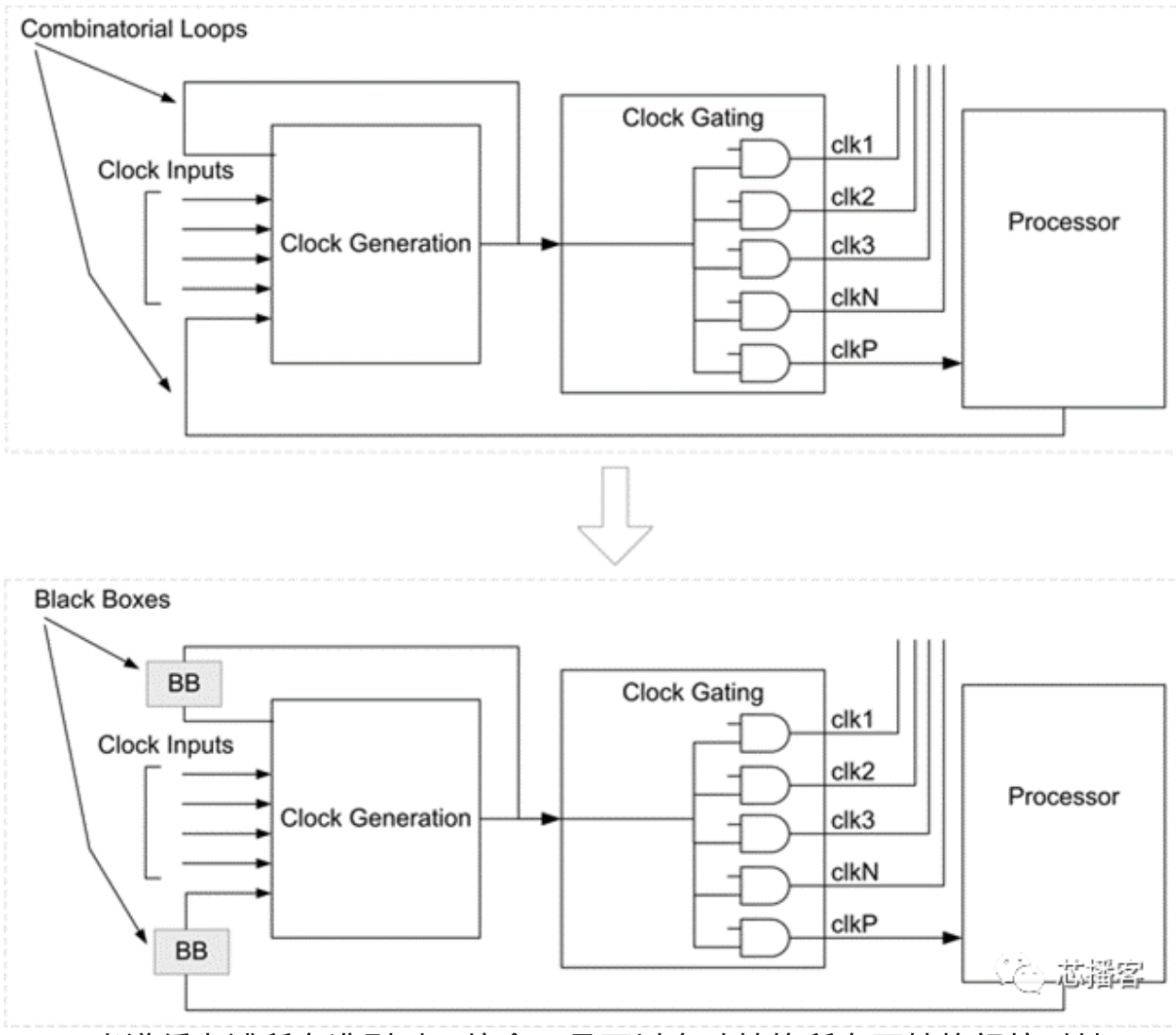

DCT实现的Flow:

DCT实现的Flow

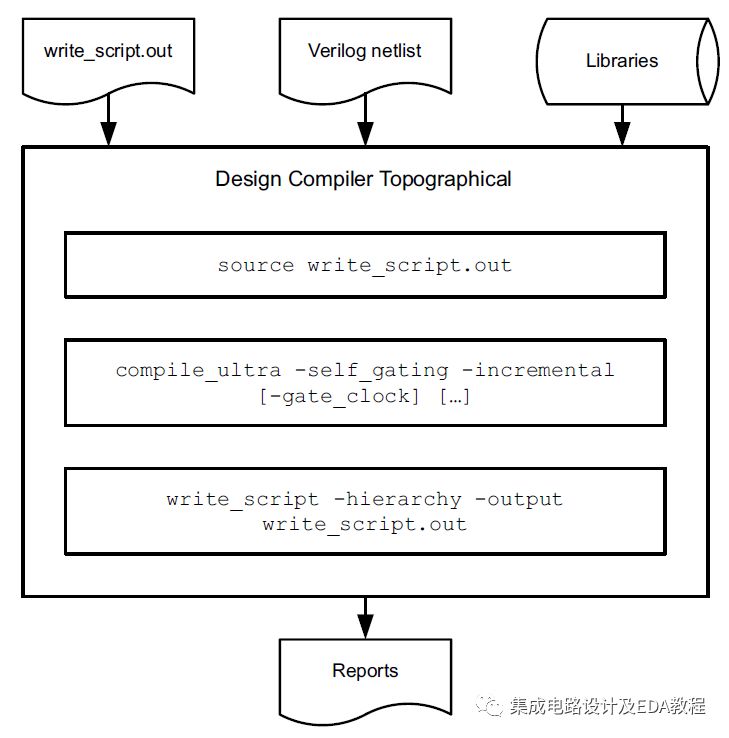

注意:当具有XOR自门控单元的ASCII网表被读回到Power Compiler工具中时,所有属性信息都将丢失,并且工具无法识别自门控单元用于报告或优化。Power Compiler工具使用write_script命令支持XOR自门控ASCII流程。如下图所示,使用下面的命令保存设计的当前属性:

write_script -hierarchy -output file_name

XOR Self-Gating ASCII Flow

将需要将设计读回工具时,可以使用source命令来加载由write_script命令导出的脚本。这将设置设计中的所有必需属性,包括用于报告和优化目的的自门控单元。

DCT实现:

使用set_self_gating_objects命令可以指定XOR自门控的对象,运行compile_ultra -self_gating命令时会执行XOR自门控。

如果不想对MID子设计中的D_OUT寄存器组执行XOR自门控,可以用下面的命令:

dc_shell-topo> set_self_gating_objects -exclude MID/D_OUT_reg[*]

dc_shell-topo> compile_ultra -self_gating

对时钟门控寄存器执行XOR自门控:

默认情况下,Power Compiler工具不会在时钟门控寄存器上执行XOR自门控。如果要对时钟门控的寄存器执行XOR自门控,可以使用以下命令:

dc_shell-topo> set_self_gating_options

-interaction_with_clock_gating insert

指定XOR自门控选项:

要指定XOR自动门控的条件并定义与时钟门控的交互,使用set_self_gating_options命令。在用命令compile_ultra -self_gating进行编译,Power Compiler插入XOR门时,会采用这些设置。

应用举例:

使用set_self_gating_options命令,对2位到9位之间的寄存器插入XOR自门控:

dc_shell-topo> set_self_gating_options -min_bitwidth 2 -max_bitwidth 9

dc_shell-topo> compile_ultra -self_gating

审核编辑:汤梓红

-

寄存器

+关注

关注

31文章

5619浏览量

130398 -

时钟

+关注

关注

11文章

1999浏览量

135228 -

门控时钟

+关注

关注

0文章

27浏览量

9247 -

XOR

+关注

关注

0文章

12浏览量

162745

原文标题:数字IC低功耗设计之--XOR自门控与Design Compiler topo实现

文章出处:【微信号:集成电路设计及EDA教程,微信公众号:集成电路设计及EDA教程】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

fpga门控时钟问题

什么是时钟门控?如何去实线时钟门控的设计呢

基于门控时钟的低功耗电路设计方案

XOR自门控与时钟门控的不同之处

XOR自门控与时钟门控的不同之处

评论