和Si晶体拉晶工艺类似,PVT法制备SiC单晶和切片形成晶圆过程中也会引入多种缺陷。这些缺陷主要包括:表面缺陷;引入深能级的点缺陷;位错;堆垛层错;以及碳包裹体和六方空洞等。其中和和Si晶体拉晶工艺不同的是,SiC容易形成多型体,所以也存在一种多型共生缺陷。其中表面缺陷主要有:划伤,划痕,亚表面损伤,微型裂痕等,目前多用强光灯下目检来进行检测,碳包裹体和六方空洞也可以目检实现,这里不多做介绍。以下主要介绍多型共生缺陷;点缺陷;位错;堆垛层错。

多型共生缺陷

多型共生缺陷是PVT法生长碳化硅晶体特有的一类结晶缺陷,它形成的根本原因是碳化硅晶体的各类多型体有着良好的结晶学相容性和相近的形成自由能。它可以来自籽晶本身的多型共生缺陷,从而复制到拉晶制备的碳化硅晶体中。但是即使对于不存在多型共生缺陷的籽晶,如果拉晶工艺条件没有控制好,也会引入到碳化硅晶体中。比如温度场的异常波动,就可以改变<0001>晶向上Si-C双原子层的堆垛顺序,从而导致晶型的改变。晶型的转变不但会严重破坏碳化硅晶体的结晶完整性,改变材料的电学特性,也会诱发与衍生其他类型的缺陷,比如微管缺陷 。生产过程中,如何监测并消除多型共生缺陷,是PVT法碳化硅晶体生长研究的一个重要任务。目前多型共生缺陷最主要的检测手段是XRD,结晶质量用XRD摇摆曲线的半高宽(FWHM)表示,工业级4H-SiC的FWHM应满足<30arcsec。

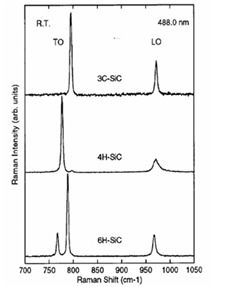

此外,拉曼散射光谱法也是测试多型共生缺陷的重要手段。我们以488nm激光作为激光源,收集到了不同晶型的拉曼散射光谱,以TO(横向光学模)为例参看图1 ,3C-SiC晶型的光谱位移峰在796cm^-1^位置,4H-SiC晶型的光谱位移峰在 776cm^-1^位置, 6H-SiC晶型的光谱位移峰在 767cm^-1^和789cm^-1^位置。通过对比位移峰的强度,也可以用来表征多型共生缺陷。

图1. 不同晶型SiC的拉曼散射位移峰

点缺陷

在所有的半导体材料中都存在点缺陷 ,它们一般都会在禁带中引入深能级,形成载流子的“陷阱”、“复合中心”,严重影响后续的半导体器件性能。

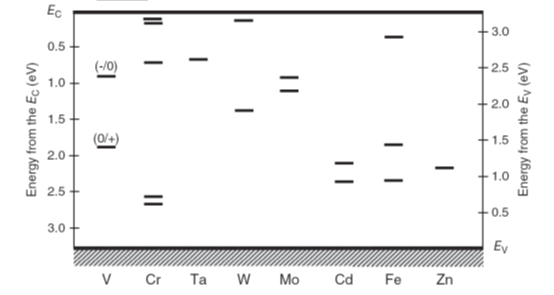

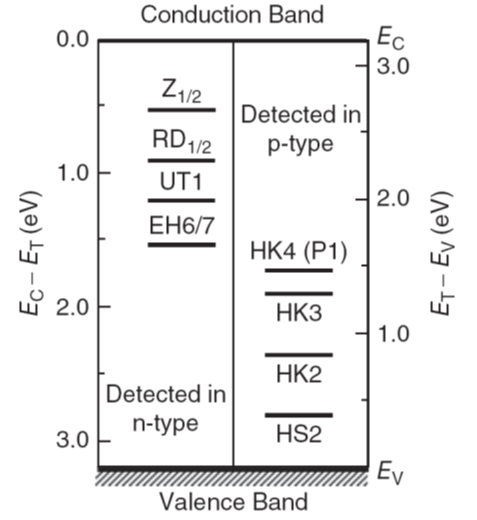

物理气相传输法制备SiC晶锭过程中,不可避免地会大量的引入杂质元素。比如来自于SiC粉末、坩埚设备,常见的元素有Ti, V, Cr, Fe, Co等。它们会在禁带中产生深能级,图2是在4H-SiC中这些元素的深能级位置 。除了这些杂质元素引起的点缺陷以外,和硅晶体类似SiC单晶中也存在空位、间隙原子等不完美的晶体缺陷。这些空位或者间隙原子也会在禁带中形成深能级,其中对器件性能影响最大的深能级有Z1/2, EH6/7。如图3所示Z1/2深能级在导带下0.6ev处,EH6/7深能级在导带下1.6ev处。目前的研究认为这两种深能级和碳空位的相关性更强。如何优化拉晶工艺来减少点缺陷的报道目前还较少。

图2. 4H-SiC中金属杂质深能级位置

图3. 4H-SiC中主要深能级的位置

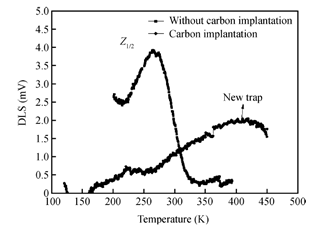

由于深能级会形成有效复合中心,特别是对双极性器件性能有着巨大影响,所以深能级的监控和表征也是十分必要。目前常用的表征防范是深能级瞬态谱(DLTS)技术。因为SiC的禁带宽度达到了3.2ev,必须在宽温度范围内(10-750K)下采集瞬态曲线来监控深能级。一般通过电加热和液氮制冷来达到此温度范围,目前常见的设备厂家如SEMILAB 。下图为SEMILAB的DLTS设备在客户端的测试曲线。

图4. SEMILAB DLTS 设备在客户端实际测试曲线

位错

SiC晶圆中位错缺陷主要包括:微管缺陷(Micropipes);螺型位错(TSD);刃型位错(TED);基矢面位错(BPD)。

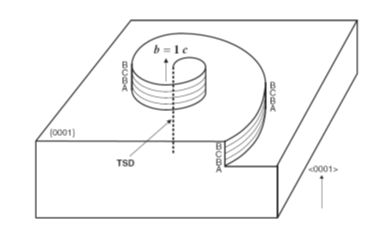

在PVT法制备工艺中,螺型位错(TSD)一般是沿着<0001>晶向传播,即晶体的垂直c轴方向,参考图5。它的来源主要来自于籽晶,如果能够得到零位错的籽晶,并在稳定条件下生长就可以极大地减少螺型位错。

微管缺陷(Micropipes)可以被看做特殊的螺型位错。当螺型位错Burgers矢量非常大时,位错核心周边的应变场也会很高,通过化学键的断裂形成微观针孔,直径为几微米左右。微管缺陷一般会沿着<0001>晶向贯穿整个晶圆,对器件性能损害极大,要在生长过程中消除。和螺型位错一样,可以使用零微管的籽晶,并在稳定条件下生长就可以极大的减少微管缺陷。

图5. 螺型位错(TSD)形成示意图

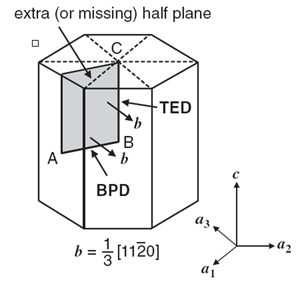

SiC晶体中,刃型位错(TED)和基矢面位错(BPD)具有相同的Burgers矢量,<11-20>/3。如图6所示,在晶体中引入一层半原子面,这种情况下一个有着Burgers矢量为<11-20>/3的位错将会出现。位于基矢面内的位错(AB线段)定义为一个“BPD”;沿着<0001>晶向的位错(BC线段)定义为一个“TED”。籽晶中的TED和BPD都会复制到晶圆中,所以利用零位错的籽晶进行拉晶生长是减少位错的关键工艺。

图6. 刃型位错(TED)和基矢面位错(BPD)形成示意图

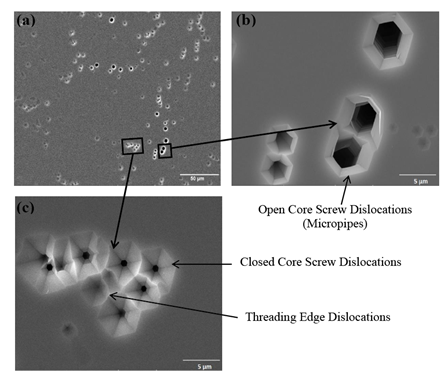

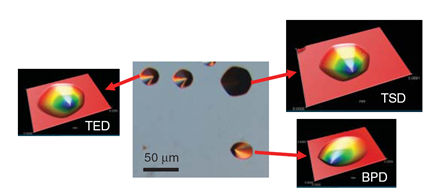

监控位错最传统和成熟的手段是化学腐蚀+光学显微镜/扫描电镜SEM。SiC是非常惰性的材料,但是可以在450-600℃下用熔融的KOH, NaOH, Na2O2进行刻蚀。SiC表面的氧化物会在刻蚀过程中被去除。因为位错处和没有位错处应力不同,所以刻蚀速率也不同,会产生诱生位错腐蚀坑。如图7所示,最大六边形坑而且中间为一个空洞的是微管缺陷;较小六边形坑中间有一个黑点的为TSD;边长不规则图像对比度差的为BPD。图8所示为化学腐蚀后的显微镜视野图,和SEM类似,其中最大六角形坑对应着TSD; 较小六角形坑对应着TED; 边长模糊的稻壳型对应着BPD。

图7. 化学腐蚀后SEM图

图8. 化学腐蚀后光学显微镜图

堆垛层错

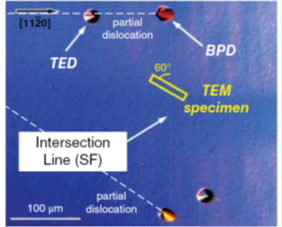

对于碳化硅晶体来说,堆垛层错(SF)是指沿着长晶的c轴方向,硅碳双原子层之间的堆接次序发生了错排。4H-SiC的堆垛层错能约为14mJ/m^2^,所以在PVT的高温工艺中很难避免。堆垛层错是碳化硅晶体在生长过程中对外长变化的一个响应,或者是释放晶体中形成其他类型结晶缺陷而在相邻区域产生的应变能的一个途径。也可以使用化学腐蚀+光学显微镜的办法监测堆垛层错缺陷。SF与表面相交时,通过刻蚀工艺后会形成凹槽,见图9中Intersection Line(SF)白色箭头位置。同时在凹槽一端会形成部分位错的椭圆形腐蚀坑。

图9. 化学腐蚀后SF与表面相交形成凹槽的光学显微镜图

来源:瑟米莱伯

审核编辑:汤梓红

-

半导体

+关注

关注

339文章

31279浏览量

266791 -

晶圆

+关注

关注

53文章

5451浏览量

132781 -

SiC

+关注

关注

32文章

3874浏览量

70203

原文标题:物理气相传输法(PVT)生长SiC晶圆中的缺陷以及测试

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

改善4H-SiC晶圆表面缺陷的高压碳化硅解决方案

【转帖】一文读懂晶体生长和晶圆制备

150mm晶圆是过去式了吗?

晶圆制造工艺的流程是什么样的?

天科合达谈八英寸SiC

碳化硅功率半导体工艺流程

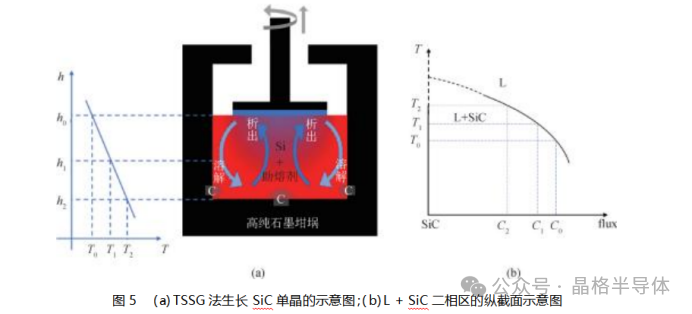

TSSG法生长SiC单晶的原理

物理气相传输法生长SiC晶圆中的缺陷和测试

物理气相传输法生长SiC晶圆中的缺陷和测试

评论