作者:Bill Schweber

时钟振荡器通过对系统组件进行起搏来提供现代电路的定时心跳。随着系统速度提高到数百兆赫兹 (MHz) 或更高,这些时钟必须更快并提供非常低的抖动(通常低于 100 飞秒 (fs))以保持系统性能。尽管温度和电压会发生变化,但它们还必须随着时间的推移保持其低抖动规格。

一些抖动是由信号路径噪声和失真引起的,使用时钟恢复和重定时技术可以在一定程度上减少抖动。然而,抖动也由时钟源产生,时钟源通常是一个振荡器。这是由于各种物理现象造成的,包括热噪声、工艺缺陷、电源噪声、进入时钟振荡器的其他外部噪声、材料应力和许多其他微妙因素。无论来源如何,设计人员都应尽一切可能将固有的时钟抖动降至最低,因为缺陷是不可逆的。

本文从不同角度讨论了抖动问题。然后介绍了[Abracon LLC]的不同时钟振荡器,并展示了如何通过将时钟振荡器性能与应用相匹配来最小化抖动。

抖动基础知识

时钟抖动是时钟边沿与其理想时间位置的偏差。这种抖动会影响时钟信号起搏的数据信号的定时精度和传输精度,导致接收器解码/解调电路或其他系统IC的信噪比(SNR)下降。这会导致更高的误码率 (BER)、增加重传并降低有效数据吞吐量。

鉴于其重要性,时钟抖动在通过电缆、连接器或电路板将信号从发射源传递到接收器的系统中被广泛分析。根据应用的不同,可以通过多种方式进行表征,包括周期间抖动、周期抖动和长期抖动(图 1)。

图 1:术语“抖动”包含许多时序变化,包括周期间抖动、周期抖动和长期抖动。(图片来源:VLSI Universe)

图 1:术语“抖动”包含许多时序变化,包括周期间抖动、周期抖动和长期抖动。(图片来源:VLSI Universe)

- 周期间抖动表示两个连续周期内时钟周期的变化,与频率随时间的变化无关。

- 周期抖动是任何时钟周期相对于其平均周期的偏差。它是理想时钟周期和实际时钟周期之间的差值,可以指定为均方根 (RMS) 周期抖动或峰峰值周期抖动。

- 长期抖动是指时钟边沿在较长时间内偏离其理想位置。这有点类似于漂移。

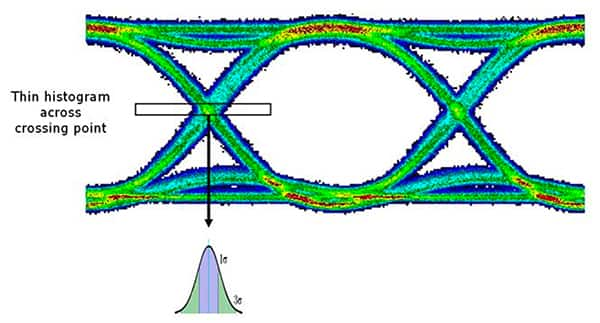

抖动会破坏其他子功能、组件或系统用于实现低 BER 数据恢复的时序,或同步系统中内存元件或处理器等组件的节奏。从图2的眼图中可以看出,这是位时序中交叉点的加宽。

图 2:在眼图中,抖动被视为数据流中关键时序交叉点的扩展。(图片来源:Kevin K. Gifford/科罗拉多大学)

图 2:在眼图中,抖动被视为数据流中关键时序交叉点的扩展。(图片来源:Kevin K. Gifford/科罗拉多大学)

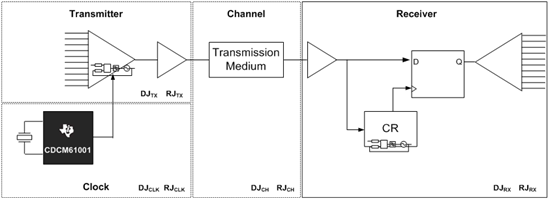

对于串行数据链路,接收端的电路必须尝试重新建立自己的时钟,以实现最佳的数据流解码。为此,它必须同步并锁定到源时钟上,通常使用锁相环 (PLL)。抖动会影响系统精确执行此操作的能力,从而影响其以低 BER 恢复数据的能力。

请注意,抖动可以在时域和频域中测量;两者都是对同一现象同样有效的观点。相位噪声是振荡器信号周围噪声频谱的频域视图,而抖动是振荡器周期定时精度的时域测量。

抖动测量可以用多种方式表示。它通常使用时间单位引用,例如“10 皮秒的抖动”(ps)。均方根 (RMS) 相位抖动是从相位噪声(频域)测量得出的时域参数。抖动有时也称为相位抖动,这可能会造成混淆,但它仍然是时域抖动参数。

随着链路工作频率及其时钟从几十MHz加速到数百MHz甚至更高,时钟源上的允许抖动降低到100 fs左右或更低。这些频率适用于光模块、云计算、网络和高速以太网,所有这些功能和应用都需要 100 至 212/215 MHz 的载波频率和高达 400 Gbps 的数据速率。

管理晶体

创建稳定、一致、准确频率时钟信号的最常见方法是使用石英晶体振荡器。相关的振荡器电路支持晶体。有许多这样的电路系列,每个系列都有不同的权衡。自 1930 年代以来,晶体一直用于中频(300 千赫兹 (kHz) 至 3 MHz)和高频(3 至 30 MHz)射频频段的无线电通信。

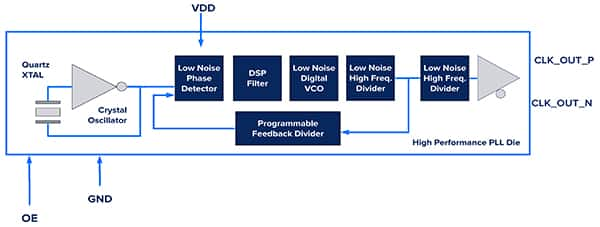

生成低抖动时钟的一种广泛使用的方法是使用基于PLL的架构的众多变体之一。例如,Abracon 的 AX5 和 AX7 ClearClock™ 系列器件分别采用 5 × 3.2 mm 和 5 × 7 mm 封装,采用先进的 PLL 技术,可实现卓越的低抖动性能(图 3)。

图 3:Abracon AX5 和 AX7 时钟振荡器采用多种基于 PLL 的设计之一,但进行了细微的增强,以最大限度地减少抖动。(图片来源:Abracon)

图 3:Abracon AX5 和 AX7 时钟振荡器采用多种基于 PLL 的设计之一,但进行了细微的增强,以最大限度地减少抖动。(图片来源:Abracon)

除了工作频率和振荡器设计外,抖动性能还受到振荡器核心石英晶体物理尺寸的影响。随着该晶体尺寸的减小,提供卓越的RMS抖动性能变得更具挑战性。

对于 100 至 200 MHz 频段的时钟解决方案,并且外形尺寸比基于 PLL 的 AX5 和 AX7 器件更小,需要一种新的振荡器架构。这些对较小尺寸的要求通常与最新一代的光收发器和模块有关。设计100至200 MHz范围内的时钟振荡器有四种既定方法:

- 使用带有倒台面石英坯的石英振荡器作为谐振器元件

- 使用带有三泛音石英坯的石英振荡器作为谐振器元件

- 使用基于低于50 MHz的第三泛音/基波模式石英空白的振荡器环路,或基于低于50 MHz的温度补偿晶体振荡器,与整数或小数模式PLL IC配合

- 使用基于低于 50 MHz 微机电系统 (MEMS) 谐振器的振荡器环路,与整数或小数模 PLL IC 配合

选项 1 不能提供最佳的 RMS 抖动性能,也不是最具成本效益的解决方案。选项 3 变得复杂且存在性能缺陷,而选项 4 的 MEMS 谐振器方法不符合 200 fs 最大 RMS 抖动的主要性能标准。相比之下,选项 2 使用优化设计的第三泛音石英坯料,并考虑了电极的几何形状和切割角度的优化。这种组合在成本、性能和尺寸方面是最佳的。

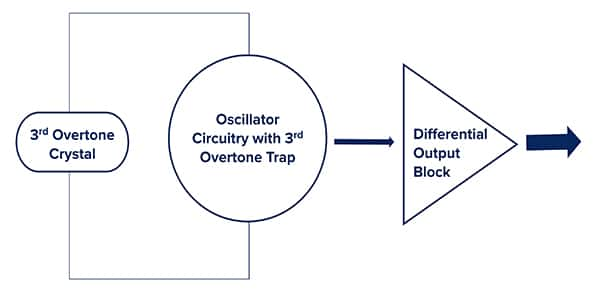

使用这种方法,Abracon 开发了“第三泛音”ClearClock 解决方案(图 4)。这些器件采用更安静的架构,在小至 2.5 × 2.0 x 1.0 mm 的微型封装中实现了卓越的超低 RMS 抖动性能和极高的能效。

图 4:Abracon 的“第三泛音”ClearClock 解决方案使用更安静的架构来提高整体性能和能效。(图片来源:Abracon)

图 4:Abracon 的“第三泛音”ClearClock 解决方案使用更安静的架构来提高整体性能和能效。(图片来源:Abracon)

在该方案中,精心设计第三泛音晶体空白,以及对所需载波信号进行适当的滤波和“捕获”,可确保在所需载波频率下具有出色的RMS抖动性能。

该架构不使用典型的PLL方法,因此没有上变频。因此,不需要标准的PLL小数或整数乘法,最终输出频率与第三泛音石英晶体的谐振频率具有一一对应的相关性。由于没有小数或整数乘法,因此简化了设计,并以尽可能小的尺寸实现了最小的抖动。

现实中的规格和性能

时钟振荡器不仅仅是一个晶体及其模拟电路。它们包括缓冲,以确保振荡器输出负载及其短期和长期变化不会影响设备的性能。它们还支持各种差分数字逻辑输出电平,以实现电路兼容性。这种兼容性消除了对外部逻辑电平转换IC的需求。这样的IC会增加成本、占用空间和抖动。

由于时钟振荡器用于许多具有不同轨电压的不同应用,因此它们必须提供各种电源电压,例如 +1.8 V、+2.5 V 或 +3.3 V,以及通常为 2.25 至 3.63 V 的自定义值。它们还必须具有不同的输出格式选项,例如低压正/伪发射极耦合逻辑 ( LVPECL ) 和低压差分信号 (LVDS) 以及其他格式。

[看看AK2A和AK3A]这两个晶体时钟振荡器系列,可以证明通过对材料、设计、架构和测试的深入理解和集成可以实现的目标。这两个系列是相似的,它们的突出区别在于尺寸和最大频率。

[AK2A]系列:该系列晶体振荡器的标称频率为 100 至 200 MHz,工作电压为 2.5 V、3.3 V 和 2.25 至 3.63 V,具有 LVPECL、LVDS 和 HCSL 差分输出逻辑。

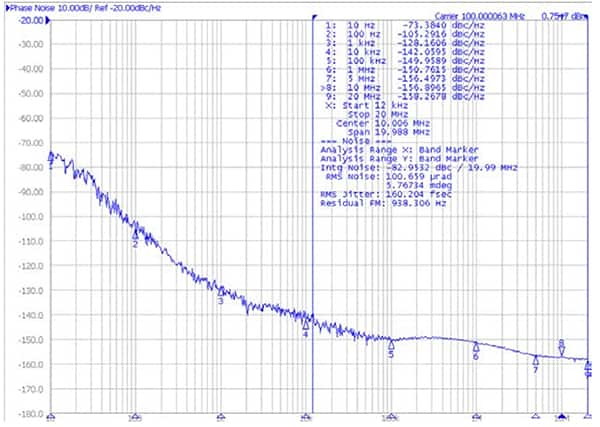

所有系列成员都具有相似的性能,包括低 RMS 抖动。例如,[AK2ADDF1-100.000T] 是一款 100.00 MHz、3.3 V 器件,具有 LVDS 输出和 160.2 fs 的 RMS 抖动(图 5)。其频率稳定性非常出色,在整个温度范围内优于百万分之 ±15 (ppm),采用尺寸为 2.5 × 2.0 × 1.0 mm 的 6 引脚表面贴装器件 (SMD) 封装。

图 5:AK2ADDF1-100.000T 是一款具有 LVDS 输出的 3.3 V、100 MHz 器件,抖动为 160 fs。(图片来源:Abracon)

图 5:AK2ADDF1-100.000T 是一款具有 LVDS 输出的 3.3 V、100 MHz 器件,抖动为 160 fs。(图片来源:Abracon)

但是,随着时钟频率的增加,抖动必须降低才能保持系统级性能。对于156.25 MHz LVDS振荡器[AK2ADDF1-156.2500T],典型RMS抖动降至83 fs。

[AK3A]系列:AK3A 系列器件比 AK2A 系列器件略大,尺寸为 3.2 × 2.5 × 1.0 mm(图 6)。提供版本,额定频率为 212.5 MHz,略高于 AK2A 系列的 200 MHz 限制。

图 6:AK3A(右)晶体振荡器比 AK2A 系列(左)略长、更宽;版本的频率最高可达 212.5 MHz,而 AK2A 的频率为 200 MHz。(图片来源:Abracon)

图 6:AK3A(右)晶体振荡器比 AK2A 系列(左)略长、更宽;版本的频率最高可达 212.5 MHz,而 AK2A 的频率为 200 MHz。(图片来源:Abracon)

此 AK3A 器件的整体规格与相应的 AK2A 系列产品相似。[例如,AK3ADDF1-156.2500T3] 是一款 156.25 MHz LVDS 振荡器,其典型 RMS 抖动为 81 fs,略好于 AK2A 系列的相应产品。

两个系列的抖动因工作频率、工作电压、封装尺寸和输出选择而异。

其他实际注意事项

仅仅拥有一个仅在出厂当天就达到规格的时钟振荡器是不够的。与所有元件(尤其是模拟和无源元件)一样,由于组成材料的老化和内应力,这些振荡器会随着时间的推移而漂移。

对于高性能时钟振荡器来说,这一现实尤其具有挑战性,因为没有方便或简单的方法可以通过添加软件或智能电路来纠正或补偿这种漂移。但是,有一些方法可以减轻漂移的影响。其中包括最终用户长时间老化以加速振荡器老化,或在烘箱控制的外壳中使用温度稳定的振荡器。前者耗时且对供应链构成挑战,而后者则体积庞大、成本高昂且耗电。

认识到老化是一个关键参数,Abracon 的 ClearClock 系列在 10 到 20 年的整个最终产品寿命范围内提供严格的、全面的频率精度。在此期间,Abracon 确保符合优于 ±50 ppm 的频率稳定性。这是通过精心选择和制造第三泛音晶体并对其进行调节来实现的,使其在-20°C至+70°C范围内达到±15 ppm的稳定性,在-40°C至+85°C范围内达到±25 ppm的稳定性。

与往常一样,工程是关于权衡的。与前代系列(分别为第一代 AK2 和 AX3)相比,Abracon AK2A 和 AK3A 系列通过使用下一代(第二代)振荡器 ASIC 提供了改进的抖动噪声性能,从而确保了超低 RMS 抖动性能。

这种改进是以功耗略有增加为代价的。最大电流消耗从第一代的 50 毫安 (mA) 增加到第二代的 60 毫安,尽管低压设备运行的电流约为该值的一半。因此,第二代 ClearClock 振荡器提供超低 RMS 抖动,同时仍保持低功耗。

结论

定时振荡器是数据链路或时钟功能的核心,其精度、抖动和稳定性是实现所需系统级性能(包括高信噪比和低误码率)的关键参数。通过创新的材料选择和架构,可以实现更高的时钟频率,这些材料和架构符合行业及其各种标准所要求的严格性能规范。Abracon AK2A 和 AK3A 系列在 100 至 200 MHz 范围内具有低于 100 fs 的抖动,采用 SMD 封装,每侧仅几毫米。

-

振荡器

+关注

关注

28文章

4155浏览量

142324 -

抖动

+关注

关注

1文章

70浏览量

19332 -

晶体振荡器

+关注

关注

9文章

733浏览量

32842 -

数据链路

+关注

关注

0文章

28浏览量

9136 -

时钟振荡器

+关注

关注

3文章

46浏览量

56759

发布评论请先 登录

怎样将相位噪声和抖动降至最低及其估算方法

基于TLK10081的千兆以太网多速率链路聚合器参考设计包括原理图和BOM表

超低抖动时钟发生器与串行链路系统性能的优化

时钟抖动对高速链路性能的影响

时间抖动的概念及其分析方法介绍

时钟抖动对高速链路性能的影响

DVI接口的TMDS链路通讯中抖动问题研究

高速ADC时钟抖动的影响的了解

了解并尽量减少抖动对高速链路的影响

了解抖动对高速链路的影响并将其降至最低

了解抖动对高速链路的影响并将其降至最低

评论