在调试FPGA电路时要遵循必须的原则和技巧,才能降低调试时间,防止误操作损坏电路。通常情况下,参考以下步骤执行 FPGA硬件系统的调试。

1、在焊接硬件电路前,首先要测试电路板的各个电源之间,各电源与地是否短路;最好是每一块板子都进行测试,这样板子焊好后如果出现电源和地短路的情况也可以首先排除是板子本身的问题。

2、在焊接硬件时,首先先焊接电源部分,然后测试,排除电源短路等情况后,上电测量电压是否正确;对于电源要求比较高的某些电路要测试电源芯片的输出电压是否处于正常工作要求的范围之内。

3、然后焊接FPGA及相关的下载电路。再次测量电源地之间有没有短路现象,上电测试各电压是否正确;将手排除静电后触摸FPGA有无发烫的现象。

a.如果出现短路,通常是去耦电容短路造成的,所以在焊接时通常先不焊去耦电容。FPGA的管脚粘连也可能造成短路,这时需要比较电路图和焊接仔细查找有无管脚粘连。

b.如果出现电压值错误,通常是电源芯片的外围调压电阻焊错,或者电源的承载力不够造成的。若是后者,则需要选用负载能力更强的电源模块替换。假如FPGA的I/O管脚与电源管脚粘连,也可能出现电压值错误的现象。

c.如果出现FPGA发烫,通常是出现总线冲突的现象。这种情况下需要自行检验外围总线是否可能出现竞争疑问。特别是多片存储器共用总线时刻。比如SRAM和FLASH芯片复用一套总线,如果片选信号同时有效就出现总线冲突。

4、以上完成后,将电路板上电运行。将下载线接到JTAG口上,看是否能正确检测到FPGA。

5、分别将测试程序写入到SRAM和PROM,确定FPGA的配置电路是否正确。

精彩推荐 至芯科技FPGA就业培训班——助你步入成功之路、12月30号西安中心开课、欢迎试听! 浮点LMS算法的FPGA实现 详解从均值滤波到非局部均值滤波算法的原理及实现方式扫码加微信邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA硬件电路的调试必备原则和技巧

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1655文章

22282浏览量

630055

原文标题:FPGA硬件电路的调试必备原则和技巧

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

单片机系统硬件的调试方法

CW32嵌入式软件开发的必备知识

【开源FPGA硬件】硬件黑客集结:开源FPGA开发板测评活动全网火热招募中......

为了减少电磁干扰,装置在硬件设计时应该遵循哪些原则?

AMD Vivado ChipScope助力硬件调试

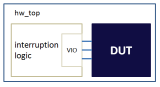

FPGA调试方式之VIO/ILA的使用

FPGA远程烧写bit文件和调试ILA指南

跟着华为学硬件电路设计,华为全套硬件电路设计学习资料都在这里了!

FPGA设计调试流程

FPGA硬件电路的调试必备原则和技巧

FPGA硬件电路的调试必备原则和技巧

评论