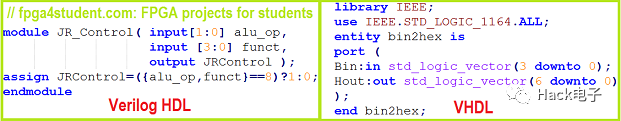

Verilog和VHDL之间的区别将在本文中通过示例进行详细说明。对优点和缺点的Verilog和VHDL进行了讨论。

HDL 建模能力:Verilog与VHDL

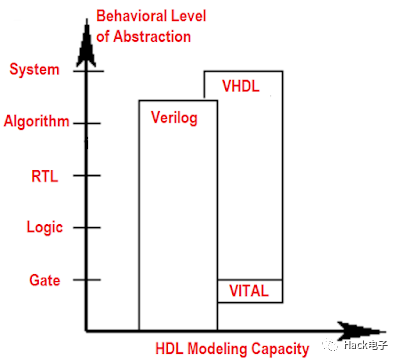

首先,让我们讨论一下 Verilog 和 VHDL 的硬件建模能力,因为它们都是用于建模硬件的硬件描述语言。

下图显示了 Verilog 和 VHDL 在硬件抽象行为级别方面的 HDL 建模能力。

图形来源:Douglas J. Smith,“VHDL 和 Verilog 比较和对比加上用 VHDL、Verilog 和 C 编写的建模示例”

低级建模

如上图所示,Verilog 和 VHDL 都能够对硬件进行建模。但是,在底层硬件建模方面,Verilog优于VHDL。这是合理的,因为 Verilog 最初是为建模和模拟逻辑门而创建的。事实上,Verilog 具有内置原语或低级逻辑门,因此设计人员可以在 Verilog 代码中实例化原语,而 VHDL 则没有。

Verilog 的门基元:and、nand、or、nor、xor、xnor、buf、not、bufif0、notif0、bufif1、notif1、pullup、pulldown。

Verilog 的开关原语:pmos、nmos、rpmos、rnmos、cmos、rcmos、tran、rtran、tranif0、rtranif0、tranif1、rtranif1。

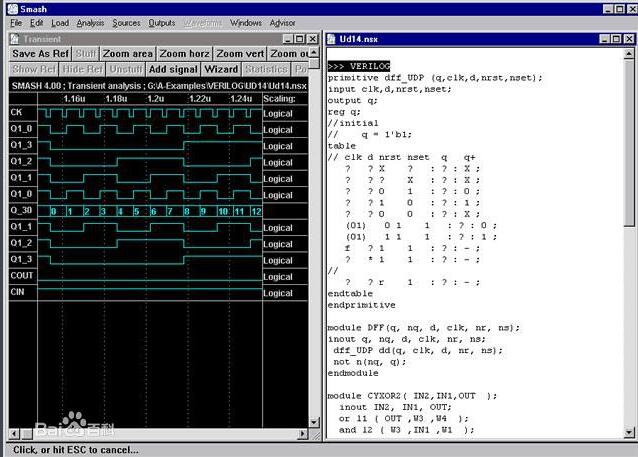

更重要的是,Verilog 支持用户定义基元 (UDP),因此设计人员可以定义自己的单元基元。此功能对于 ASIC 设计人员来说尤其必要。

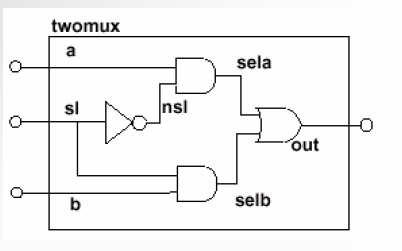

以下是有关如何在 Verilog 代码中实例化门基元的 Verilog 示例:

or #5 u1(x,y,z); and #10 u2(i1,i2,i3); ADC_CIRCUIT u3(in1,out1,out2,clock); // ADC_CIRCUIT is an User-Defined Primitive for // Analog to Digital Converter for example.

Verilog 中一些低级内置门基元的 VHDL 等效项可以通过使用逻辑运算符如 NOT、AND、NAND、OR、NOR、XOR、XNOR 来实现。

下面是 Verilog 门基元的 VHDL 等效代码示例:

or u1(x,y,z); in Verilog <=> x <=< span=""> y OR z; in VHDLand u2(i1,i2,i3); (Verilog) <=> i3 <=< span=""> i2 AND i3; in VHDL

为了支持 Verilog 中的 UDP 功能,VITAL(VHDL Initiative Towards ASIC Libraries-VHDL 面向 ASIC 库的倡议)问世,使 ASIC 设计人员能够在符合 VITAL 的 VHDL 中创建自己的单元基元或 ASIC 库,如上图所示。尽管如此,VHDL 仍然可能无法实现 Verilog 对低级硬件建模的支持。因此,如果我是 ASIC 设计师,我会更喜欢 Verilog 而不是 VHDL。

高级建模

另一方面,如上述图表所示,VHDL 在高级硬件建模方面优于 Verilog。与 Verilog 相比,VHDL 为高级硬件建模提供了更多功能和构造。以下是在比较 VHDL 和 Verilog 时支持高级硬件建模的主要不同功能:

VHDL 中的用户定义数据类型

Verilog 的数据类型非常简单,都是用 Verilog 语言定义的(用户不能在 Verilog 中定义自己的数据类型)。Verilog 有两种主要的数据类型,包括 net 数据类型(用于将组件连接在一起,例如wire(最流行)、wor、wand、tri、trior 等)和变量数据类型(用于临时存储,例如reg(最流行),整数、时间、实数和实时)。

VHDL支持许多不同的数据类型,包括预定义的 VHDL 数据类型和用户定义的数据类型。预定义的 VHDL 数据类型包括位、位向量、字符串、时间、布尔值、字符和数字(实数或整数)。VHDL 允许设计人员根据预定义的 VHDL 数据类型定义不同的类型;对于可能使用许多不同数据类型的复杂和高级系统来说,这是一个很好的功能。以下是用于定义新数据类型的示例 VHDL 代码:

type int_8bit is range 0 to 255 -- define 8-bit unsigned numbers signal i : int_8bit; type state_FSM is (Idle, start, calculate , finish, delay) -- define symbolic states to represent FSM states. signal current_state, next_state: state_FSM;

VHDL 中的设计重用包

VHDL 中的包通常用于数据类型和子程序的声明。VHDL 包中声明的子程序或数据类型可用于许多不同的实体或体系结构。例如:

package fsm_type is type FSM_states is (IDLE, TRANSMIT, RECEIVE, STOP); end package -- to use the FSM_states type in an entity or architecture -- use the following statement on top of the entity use work.fsm_type.all entity example is

Verilog 中没有包定义。与 VHDL 包最接近的 Verilog 等效项是`includeVerilog 编译器指令。函数或定义可以单独保存在另一个文件中,然后通过使用`include指令在模块中使用它。下面是一个 Verilog 示例代码:

// Below is the content of "VerilogVsVHDL.h" file `define INPUT_VERILOG "./test_VerilogvsVHDL.hex" // Input file name `define OUTPUT_VHDL "VHDL.bmp" // Output file name `define VERILOG_VHDL_DIFFERENCE // Then call it in every single module that you want to use the definition above `include "VerilogVsVHDL.h"

VHDL 中的配置语句

一个 VHDL 设计可以为一个实体获得许多具有不同体系结构的设计实体。配置语句将确切的设计实体与设计中的组件实例相关联。当实体中有多个架构时,配置语句会继续指定所需的设计架构分配给实体以进行综合或仿真。当 VHDL 设计人员需要管理大型高级设计时,此功能非常有用。

以下是配置语句的 VHDL 示例代码:

entity BUF is generic (DELAY : TIME := 10 ns); port ( BUF_IN : in BIT; BUF_OUT : out BIT); end BUF; -- The first design architecture for BUF architecture STRUCT_BUF1 of BUF is signal temp: bit; begin BUF_OUT <=< span=""> not temp after DELAY; temp <=< span=""> not BUF_IN after DELAY; end STRUCT_BUF1; -- The second design architecture for BUF architecture STRUCT_BUF2 of BUF is begin BUF_OUT <=< span=""> BUF_IN after 2*DELAY;; end STRUCT_BUF2; -- Testbench to simulate BUF entity entity BUF_TESTBENCH is end BUF_TESTBENCH; architecture STRUCT_BUF_TEST of BUF_TESTBENCH is signal TEST1, TEST2 : BIT := '1'; -- BUF_COMP component declaration: component BUF_COMP is generic (TIME_DELAY : TIME); port ( IN1 : in BIT; OUT1 : out BIT ); end component; begin -- instantiation of BUF_COMP component: DUT:BUF_COMP generic map (10 ns) port map (TEST1,TEST2); end STRUCT_BUF_TEST; -- Configuration specify the design entity and architecture -- for the DUT component instance in the testbench above configuration CONFIG_BUF of TEST_BUF is -- Associate BUF_COMP component instance to BUF design entity -- and STRUCT_BUF1 design architecture for simulation for STRUCT_BUF_TEST for DUT : BUF_COMP use entity WORK.BUF (STRUCT_BUF1) generic map (DELAY => TIME_DELAY) port map (BUF_IN => IN1, BUF_OUT => OUT1); end for; end for ; end CONFIG_BUF;

Verilog-2001 中还添加了配置块。

VHDL 中的库管理

同时查看 Verilog 和 VHDL 代码时,最明显的区别是 Verilog 没有库管理,而 VHDL 在代码顶部包含设计库。VHDL 库包含已编译的架构、实体、包和配置。此功能在管理大型设计结构时非常有用。上面已经给出了 VHDL 中的包和配置示例。以下是 VHDL 中库管理的 VHDL 示例代码:

-- library management in VHDL library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.numeric_std.all; use work.clock_div.all;

简而言之,VHDL 在高级硬件建模方面比 Verilog 更好。由于 FPGA 设计流程不需要低级硬件建模,如果我是 FPGA 设计师,我更喜欢 VHDL 而不是 Verilog。

值得一提的是,SystemVerilog 的创建是为了通过将 VHDL 中的高级功能和结构添加到 Verilog 中进行验证来增强 Verilog 语言在高级建模中的弱点。SystemVerilog 现在广泛用于 IC 验证。

冗长(Verboseness:):Verilog 与 VHDL

VHDL 是强类型的vs Verilog 是松散类型的

VHDL 是一种非常强类型的硬件描述语言,因此必须使用匹配和定义的数据类型正确编写 VHDL 代码。这意味着如果在 VHDL 中分配时混合数据类型或不匹配信号,将会出现编译错误。另一方面,Verilog 是一种松散类型的语言。在 Verilog 中,您可以在分配时混合数据类型或不匹配信号。下面是不匹配信号的 VHDL 示例代码:

signal test_reg1: std_logic_vector(3 downto 0); signal test_reg2: std_logic_vector(7 downto 0); test_reg2 <=< span=""> test_reg1; -- You cannot assign a 4-bit signal to an 8-bit signal -- in VHDL, it will introduce a syntax error below: -- Width mismatch. Expected width 8, Actual width is 4 -- for dimension 1 of test_reg1.

编译上面的VHDL代码时,会出现语法错误“Width mismatch. Expected width 8, Actual width is 4”。如果将VHDL代码改为“test_reg2 <= "0000"&test_reg1; "匹配位宽,则不会出现语法错误。

如果在 Verilog 中将 4 位信号分配给 8 位信号会怎样?

wire [3:0] test1; wire [7:0] test2; // In Verilog, you can assign 4-bit signal to 8-bit signal. assign test2 = test1; // there will be no syntax error during synthesis

当您将 4 位信号分配给 8 位信号时,Verilog 编译器不会引入语法错误。在 Verilog 中,不同位宽的信号可以相互分配。Verilog 编译器将使源信号的宽度适应目标信号的宽度。未使用的位将在综合期间进行优化。

下面是在分配信号时混合数据类型的另一个 VHDL 示例:

signal test1: std_logic_vector(7 downto 0); signal test2: integer; test2 <=< span=""> test1; -- Syntax Error: type of test2 is incompatile with type of test1

上面的 VHDL 代码会引入一个语法错误“(type of test2 is incompatible with type of test1)test2 的类型与 test1 的类型不兼容”。你必须转换test1的分配之前整数数据类型TEST1到TEST2如下:

library IEEE; USE ieee.numeric_std.ALL; signal test1: std_logic_vector(3 downto 0); signal test2: integer; -- Use IEEE.NUMBERIC_STD.ALL Library for this conversion test2 <=< span=""> to_integer(unsigned(test1)); -- No syntax errors this time

另一方面,Verilog 在分配时混合数据类型时没有问题。以下是一个 Verilog 示例:

reg [3:0] test1;

integer test2;

always @(test1) begin

test2 = test1;

end

// NO syntax errors when compiling

当您将具有reg数据类型的信号分配给具有不同数据类型(如integer )的另一个信号时,Verilog 编译器不会像在 VHDL 中那样引入语法错误。

VHDL 复杂数据类型与 Verilog 简单数据类型

如上所述,VHDL 有许多不同的复杂数据类型,用户还可以定义许多其他复杂数据类型。这也使得 VHDL 比 Verilog 更冗长,因为 Verilog 只有 2 种主要数据类型,并且 Verilog 中不允许用户定义的数据类型。

换句话说,为了对同一电路建模,VHDL 代码通常比 Verilog 代码更冗长、更长,因为 VHDL 的强类型,我们需要在不同的复杂数据类型之间执行转换。它可以是优点也可以是缺点。事实上,当您在 VHDL 代码中分配错误的内容时,VHDL 编译器更有可能引入语法错误。当您成功编译 VHDL 代码时,与 Verilog 相比,您的 VHDL 代码更有可能正常工作。另一方面,Verilog 是松散类型的,更简洁,更简单。但是编译成功后,很有可能你的Verilog代码中仍然存在错误。

下面是另一个使 VHDL 比 Verilog 更冗长的示例代码:

-- VHDL code for ALU process(SEL,ABUS,BBUS,tmp1,tmp2) begin case(SEL) is when "0000" => ALUOUT <=< span=""> tmp1; -- ADD when "0001" => ALUOUT <=< span=""> tmp2;-- SUB when "0010" => ALUOUT <=< span=""> BBUS; -- AND when others => ALUOUT <=< span=""> ABUS; end case; end process; // Verilog equivalent to VHDL ALU assign ALUOUT=(SEL==0)?tmp1:((SEL==1)?tmp2:((SEL==2)?BBUS:ABUS));

VHDL 中的 if else、when/else、with/select 语句可以在 Verilog 中使用条件运算符 (?) 表达得更简洁,如上例所示。

Verilog 和 VHDL 之间的其他区别:

Verilog 类似于C 编程语言,而 VHDL 类似于Ada或 Pascal 编程语言

Verilog 区分大小写,而 VHDL 不区分大小写。这意味着DAta1和Data1在Verilog中是两个不同的信号,但在VHDL中是相同的信号。

在 Verilog 中,要在模块中使用组件实例,您只需在模块中使用正确的端口映射对其进行实例化。在VHDL中,在实例化实例之前,如果您使用旧的实例化语句作为以下示例,则通常需要将组件声明为架构或包中。在 VHDL-93 中,您可以像这样直接实例化实体:“Label_name: entity work.component_name port map (port list);”。

例如,要在 VHDL 中实例化实体 clk_div,将在体系结构代码中添加一个组件声明,如下所示:

architecture Behavioral of digital_clock is -- component declaration before instantiation below component clk_div port ( clk_50: in std_logic; clk_1s : out std_logic ); end component; signal clk, clk_1s: std_logic; begin -- component instantiation create_1s_clock: clk_div port map (clk_50 => clk, clk_1s => clk_1s); end

或者在包中声明组件以供重用:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

package clock_div_pack is

component clk_div is

port (

clk_50: in std_logic;

clk_1s : out std_logic

);

end component clk_div;

end package;

-- Declare the component in a separate package and

-- reuse by using the following statement:

use work.clock_div_pack.all;

entity clock is

end clock;

architecture Behavioral of clock is

signal clk, clk_1s: std_logic;

begin

create_1s_clock: clk_div port map (clk_50 => clk, clk_1s => clk_1s);

end

在 VHDL-93 中直接实例化实体的示例代码:

create_1s_clock: entity work.clk_div port map (clk_50 => clk, clk_1s => clk_1s);

Verilog 具有编译器指令,例如`timescale(声明时间单位和延迟精度)、`define(将文本字符串声明为宏名称)、`ifdef、ifndef `else `elseif `endif(条件编译)、`include(包括一个可以包含函数或其他声明的文件)等。VHDL 没有编译器指令。

VHDL 支持枚举和记录数据类型,允许用户为一种数据类型定义多个信号。Verilog 不支持枚举和记录类型。下面是枚举和记录类型的 VHDL 代码:

type FSM is (IDLE, TEST, VERILOGvsVHDL, STOP, FPGA4student); -- enumerated type type int_4 is range 0 to 15; -- record tye in VHDL type record_example is record data1: integer; data2: int_4; data3: FSM; end record;

等等。

尽管 Verilog 和 VHDL 之间存在差异,但它们是两种最流行的硬件描述语言。如果可以,最好同时学习它们。重要的是要记住,在编码时始终考虑逻辑门或硬件以开发硬件编码思维,而在使用 Verilog 和 VHDL 编码时忘记软件编程思维,这一点非常重要。

审核编辑:刘清

-

NAND

+关注

关注

16文章

1766浏览量

141316 -

asic

+关注

关注

34文章

1278浏览量

124987 -

VHDL语言

+关注

关注

1文章

113浏览量

19467 -

编译器

+关注

关注

1文章

1673浏览量

51965 -

Verilog HDL

+关注

关注

17文章

126浏览量

51486

原文标题:例说Verilog HDL和VHDL区别,助你选择适合自己的硬件描述语言

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何用VHDL、Verilog HDL实现设计输入?

X-HDL v3.2.55 VHDL/Verilog语言翻译器

Verilog HDL与VHDL及FPGA的比较分析

vhdl和verilog的区别_vhdl和verilog哪个好?

Verilog HDL的基础知识详细说明

例说Verilog HDL和VHDL区别

例说Verilog HDL和VHDL区别

评论