1 简介

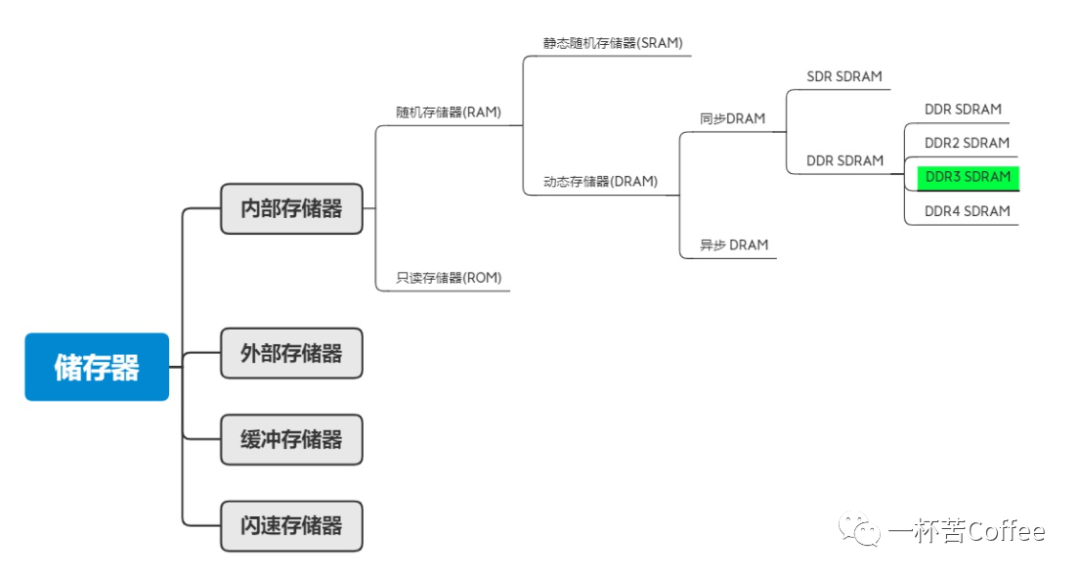

SPI(Serial Peripheral Interface) 是串行外设接口的简称,是微控制器(MCU)与外围设备通信最常见的接口,常见的外围设备包含ADC/DAC、传感器以及存储器等。

2 SPI的特点

- SPI有哪些引脚?

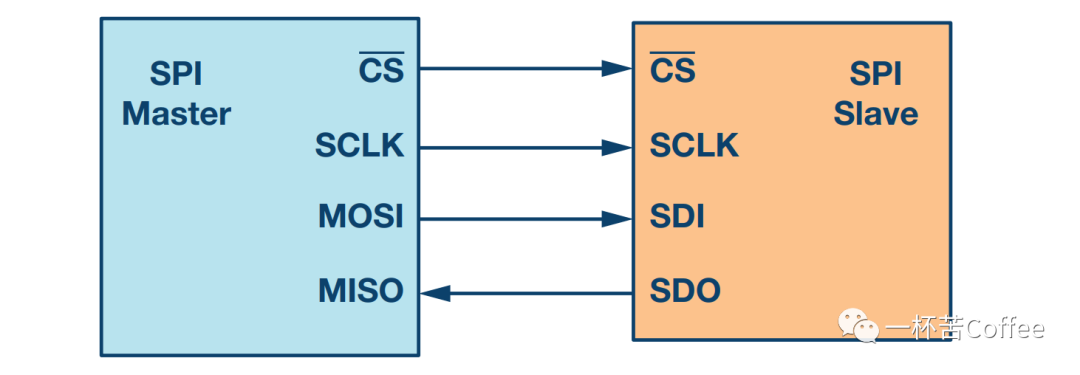

SPI是一种同步全双工通信方式,我们一般采用四线SPI接口,具体包含以下这些信号:

- 时钟信号(SPI Clock,SCLK)

- 片选信号(Chip Select,SC)

- 主机输出,从机输入(Master Output Slave Inpit,MOSI或DO)

- 主机输入,从机输出(Master Inpit Slave Output,MISO或DI)

其中每个PIN脚都有其特定的功能,具体见下:

| 信号名称 | 功能描述 |

|---|---|

| 时钟信号CLK | 主机用于产生时钟信号,主机和从机之间的数据同步。 |

| 片选信号CS | 用于选择从机,常低电平有效。 |

| 数据信号(MISO) | 从机将数据发送给主机。 |

| 数据信号(MOSI) | 主机将数据发送给从机。 |

- SPI信号与I2C信号有哪些差异?

SPI接口与I2C接口有很明显的不同,具体体现在以下几个方面:

- SPI时钟的频率比I2C时钟频率更高。

- SPI采用四线制,I2C采用二线制。

- SPI只能有一个主机,I2C可以有多个主机(总线仲裁机制)。

- SPI信号数据传输过程?

SPI通信需要的时钟由主机(Master)产生,且主机通过片选信号来选择通信的设备(低电平有效,由主机主动拉低)。SPI能同时进行数据的发送(MOSI)与接收(MISO),且SPI允许用户灵活选择时钟的上升沿/下降沿进行数据的采样和移位。

3 时钟极性和时钟相位

- 什么是时钟极性(CPOL)和时钟相位(CPHA)?

在SPI通信中。时钟极性和时钟相位是可以由用户进行设定的。

时钟极性(CPOL) :决定了时钟信号在空闲时的状态(高电平或者低电平)。

时钟相位(CPHA) :决定了是在上升沿或者下降沿进行采样和移位。

| SPI | CPOL | COHA | 时钟极性(空闲) | 时间(采样/移位) |

|---|---|---|---|---|

| 0 | 0 | 0 | 低电平 | 上升沿采样、下降沿移出 |

| 1 | 0 | 1 | 低电平 | 下升沿采样、上降沿移出 |

| 2 | 1 | 1 | 高电平 | 下升沿采样、上降沿移出 |

| 3 | 1 | 0 | 高电平 | 上升沿采样、下降沿移出 |

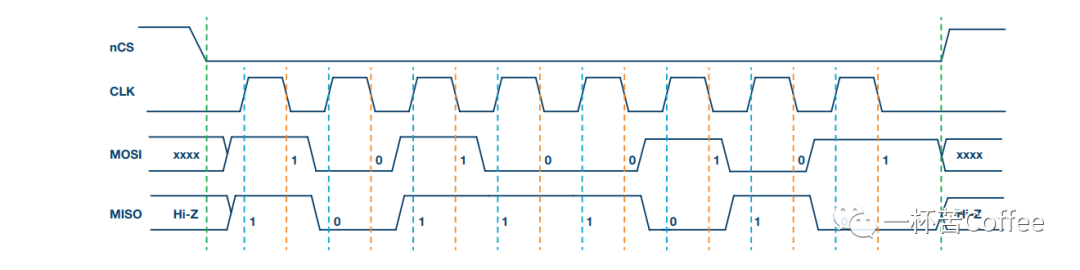

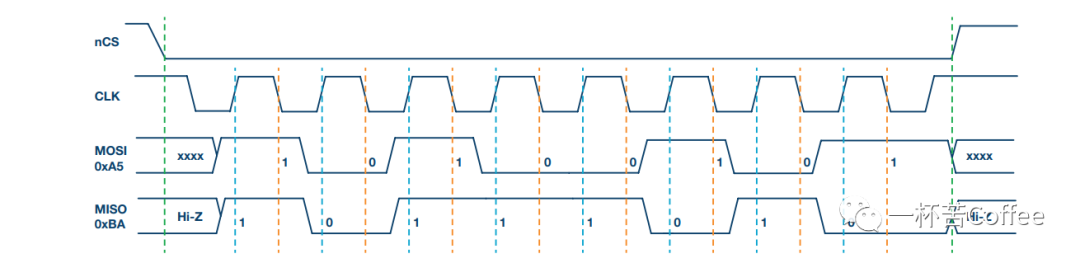

- 时钟极性(CPOL)和时钟相位(CPHA)的图解

说明:

- 绿色:表示数据传输的开始和结束。

- 橙色:表示数据的采样。

- 蓝色:表示数据的移位。

- SPI模式0,CPOL = 0,CPHA = 0:CLK空闲状态 = 低电平,数据在上升沿采样,并在下降沿移出。

- SPI模式1,CPOL = 0,CPHA = 1:CLK空闲状态 = 低电平,数据在下降沿采样,并在上升沿移出。

- SPI模式2,CPOL = 1,CPHA = 0:CLK空闲状态 = 高电平,数据在下降沿采样,并在上升沿移出。

- SPI模式3,CPOL = 1,CPHA = 1:CLK空闲状态 = 高电平,数据在上升沿采样,并在下降沿移出。

4 SPI的级联

多个从机可与单个SPI主机一起使用。从机可以采用常规模式连接,或采用菊花链模式连接。

- 常规模式

在常规模式下,主机需要为每个从机提供单独的片选信号。一旦主机使能(拉低)片选信号,MOSI/MISO线上的时钟和数据便可用 于所选的从机。如果使能多个片选信号,则MISO线上的数据会被破坏,因为主机无法识别哪个从机正在传输数据。从下图可以看出,随着从机数量的增加,来自主机的片选线的数量 也增加。这会快速增加主机需要提供的输入和输出数量,并限制可以使用的从机数量。可以使用其他技术来增加常规模式下的从机数量,例如使用多路复用器产生片选信号。

- 菊花链模式

在菊花链模式下,所有从机的片选信号连接在一起,数据从一个从机传播到下一个从机。在此配置中,所有从机同时接收同一SPI时钟。来自主机的数据直接送到第一个从机,该从机将数据提供给下一个从机,依此类推。

使用该方法时,由于数据是从一个从机传播到下一个从机,所以传输数据所需的时钟周期数与菊花链中的从机位置成比例。例如在下图所示的8位系统中,为使第3个从机能够获得数据,需要24个时钟脉冲,而常规SPI模式下只需8个时钟脉冲。图8显示了时钟周期和通过菊花链的数据传播。并非所有SPI器件都支持菊花链模 式。请参阅产品数据手册以确认菊花链是否可用。

-

微控制器

+关注

关注

49文章

8890浏览量

165888 -

电路设计

+关注

关注

6746文章

2800浏览量

220401 -

接口

+关注

关注

33文章

9603浏览量

157677 -

SPI

+关注

关注

17文章

1900浏览量

102213 -

串行外设接口

+关注

关注

0文章

25浏览量

4204

发布评论请先 登录

怎么成为硬件电路设计高手?

硬件电路设计的思路分享

硬件电路设计之“磁珠”的应用资料下载

硬件电路设计之SPI电路设计

硬件电路设计之SPI电路设计

评论