什么是JKE触发器?

FF_JKE是一个具有异步设置(SET)和重置(RST)输入的边缘触发的JK触发器(JK Flip-Flop), 仅SET=1时,输出Q=1;只要RST=1,输出Q=0。RST=SET=0时,在CLK上升沿到来时,则:

- 当J=K=0 ,输出Q保持不变;

- 当J=1 且 K=0 ,输出Q=1;

- 当J=0 且 K=1 ,输出Q=0;

- 当J= K=1 ,输出Q取反;

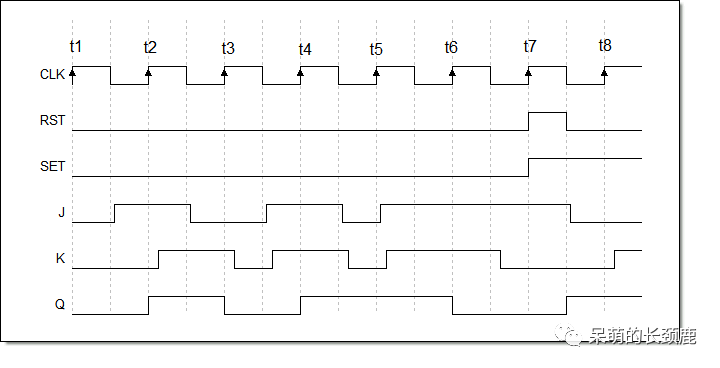

时间图如下:

特征表如下:

其中: CLK:时钟, RST:重置, SET: 设置 , J、K:输入 , Q:输出

- 假设最初 输入都为0,输出 Q = 0;

- 在t1处,J=K=0 ,输出Q保持不变;

- 在t2处,J=1 且 K=0 ,输出Q=1;

- 在t3处,J=0 且 K=1 ,输出Q=0;

- 在t4处,J= K=1,输出Q取反,输出Q=1;

- 在t5处,J=K=0 ,输出Q保持不变,输出Q=1;

- 在t6处,J= K=1,输出Q取反,输出Q=0;

- 在t7处,RST=1,输出Q=0;

- 在t8处,SET=1且RST=0,输出Q=1;

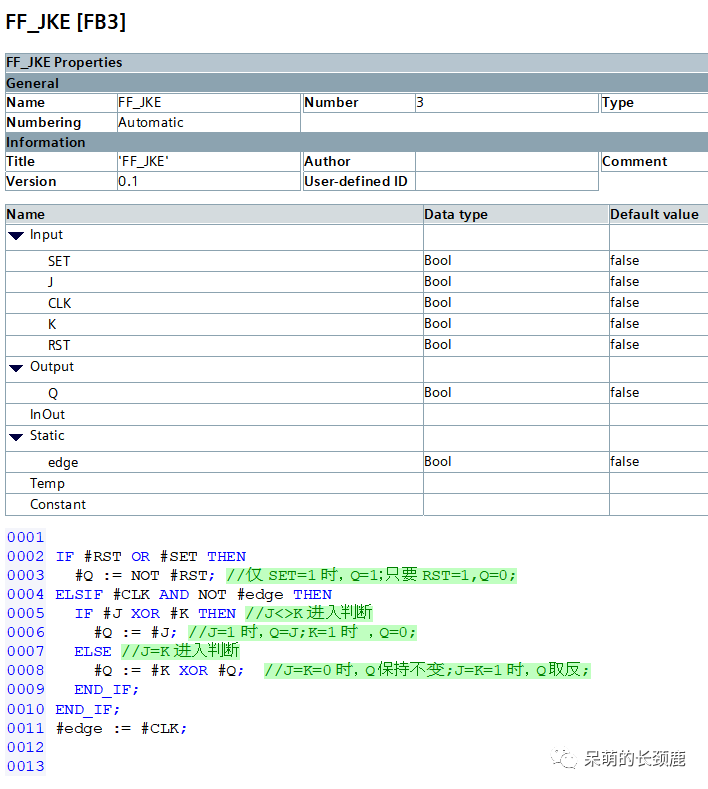

源代码如下:

FUNCTION_BLOCK "FF_JKE"

TITLE = 'FF_JKE'

{ S7_Optimized_Access := 'TRUE' }

VERSION : 0.1

VAR_INPUT

SET : Bool;

J : Bool;

CLK : Bool;

K : Bool;

RST : Bool;

END_VAR

VAR_OUTPUT

Q : Bool;

END_VAR

VAR

edge : Bool;

END_VAR

BEGIN

IF #RST OR #SET THEN

#Q := NOT #RST; //仅SET=1时,Q=1;只要RST=1,Q=0;

ELSIF #CLK AND NOT #edge THEN

IF #J XOR #K THEN //J< >K进入判断

#Q := #J; //J=1时,Q=J;K=1时 ,Q=0;

ELSE //J=K进入判断

#Q := #K XOR #Q; //J=K=0时,Q保持不变;J=K=1时,Q取反;

END_IF;

END_IF;

#edge := #CLK;

END_FUNCTION_BLOCK

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

JK触发器

+关注

关注

1文章

44浏览量

16753 -

触发器

+关注

关注

14文章

2065浏览量

63545 -

RST

+关注

关注

0文章

31浏览量

7857 -

CLK

+关注

关注

0文章

132浏览量

18095

发布评论请先 登录

相关推荐

热点推荐

JK触发器,JK触发器是什么意思

JK触发器,JK触发器是什么意思

1.主从JK触发器主从结构触发器也可以彻底解决直接控制,防止空翻。这里以性能优良、广泛使用的主从JK触发器

发表于 03-08 13:36

•7619次阅读

施密特触发器,施密特触发器是什么意思

施密特触发器,施密特触发器是什么意思

施密特触发器也有两个稳定状态,但与一般触发器不同的是,施密特触发器采用电位

发表于 03-08 14:14

•2383次阅读

什么是边沿触发器_边沿D触发器介绍

边沿触发器,指的是接收时钟脉冲CP 的某一约定跳变(正跳变或负跳变)来到时的输入数据。在CP=l 及CP=0 期间以及CP非约定跳变到来时,触发器不接收数据的触发器。具有下列特点的触发器

发表于 01-31 09:02

•7.3w次阅读

t触发器和jk触发器的区别和联系

触发器是数字电路中常用的组合逻辑电路,在现代电子系统中有着广泛的应用。其中,最常用的两种触发器是T触发器和JK触发器。本文将详细介绍T触发器

如何用jk触发器构成t触发器?t触发器逻辑功能有哪些

如何用JK触发器构成T触发器 JK触发器是一种基本的触发器电路,由两个输入端J和K控制,以及两个输出端Q和Q'组成。JK触发器的输出可以持续

t触发器与d触发器的区别和联系

在数字电路设计中,触发器是一种非常重要的存储元件,用于存储一位二进制信息。触发器的种类很多,其中最为常见的是T触发器(Toggle Flip-Flop)和D触发器(Data Flip-

t触发器变为d触发器的条件

在数字电路设计中,触发器是一种非常重要的存储元件,用于存储一位二进制信息。触发器的种类很多,其中最为常见的有JK触发器、D触发器和T触发器等

d触发器和jk触发器的区别是什么

引言 数字电路是现代电子技术的基础,广泛应用于计算机、通信、控制等领域。触发器是数字电路中的一种基本逻辑元件,具有存储和传递信息的功能。 触发器的基本概念 触发器是一种具有记忆功能的数字电路元件

怎么用jk触发器变成t触发器

将JK触发器变成T触发器,主要涉及到对JK触发器的输入端口进行适当的连接和配置,以实现T触发器的逻辑功能。以下是将JK触发器转换为T

什么是JKE触发器?

什么是JKE触发器?

评论