传输线在阻抗匹配时串联端接电阻为什么要靠近发送端?

传输线在阻抗匹配时,串联端接电阻靠近发送端的原因有多个方面。

首先,了解传输线的基本原理是必要的。传输线是用于传输电信号的导体,如电缆或微带线。它有一个特定的阻抗,通常以欧姆表示,表示为电阻和电抗的复数组合。传输线的负载阻抗与传输线的特性阻抗之间的不匹配会导致反射,并且会产生信号衰减和系统性能下降。

在阻抗匹配时,串联端接电阻靠近发送端,可以减少传输线末端的反射。当信号从发送端传输到传输线末端时,如果负载阻抗与传输线的特性阻抗不匹配,就会由于反射而导致信号的部分反射回到发送端。这种反射会导致信号干扰和失真,并且会降低传输线的效率。

然而,如果串联端接电阻靠近传输线末端,反射会更加明显。这是因为信号在传输线上传播的速度是有限的,而信号的反射需要一定的时间才能回到发送端。如果串联端接电阻在传输线的末端附近,反射会在传输线上往返多次,从而产生更大的干扰。因此,为了减少反射引起的信号失真,串联端接电阻应该靠近发送端。

另一个原因是,串联端接电阻靠近发送端可以降低传输线的负载容量。传输线具有一定的电容性质,当信号传输到末端时,负载阻抗会与传输线的电容串联形成低通滤波器。这将导致高频信号的衰减,并且会限制系统的频率响应。如果串联端接电阻靠近发送端,传输线的负载容量将减少,高频信号的衰减将降低,从而提高传输线的频率响应。

此外,将串联端接电阻靠近发送端还可以减少信号的串扰。当多个传输线并行布置时,信号在相邻的传输线之间可能会引起串扰。如果串联端接电阻靠近发送端,信号的引导路径将更短,并且信号的电磁场干扰范围将减小,从而减少串扰的可能性。

在实际应用中,将串联端接电阻靠近发送端,也可以使系统的调试和维护更加方便。如果串联端接电阻靠近传输线末端,需要在发送端和传输线末端之间添加插入点或切换开关,以便在调试或维护时屏蔽电阻的影响。而将串联端接电阻靠近发送端,可以在不影响传输线的情况下更容易地接入或调整电阻。

总的来说,传输线在阻抗匹配时,串联端接电阻靠近发送端是为了减少反射引起的信号失真、降低传输线的负载容量、减少信号的串扰,并且便于系统的调试和维护。因此,在实际应用中,我们应该合理地设计和布局传输线,以确保串联端接电阻靠近发送端。

-

阻抗匹配

+关注

关注

14文章

379浏览量

32158 -

传输线

+关注

关注

0文章

384浏览量

25583

发布评论请先 登录

音频变压器功能解析:噪声隔离、阻抗匹配与信号平衡转换

音频变压器功能解析:噪声隔离、阻抗匹配与信号平衡转换

线路板阻抗匹配:实操中要避开的 3 个设计误区

线路板阻抗匹配实操:过孔与拐角的处理技巧

技术资讯 I 信号完整性与阻抗匹配的关系

基于史密斯圆图实现天线阻抗匹配

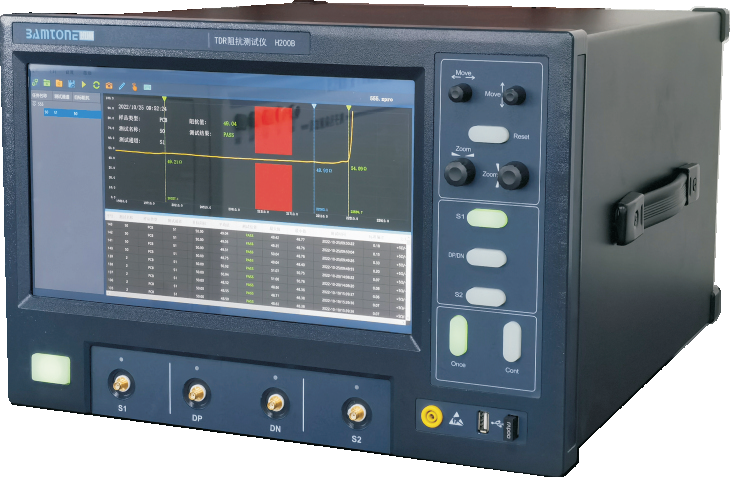

如何用TDR阻抗测量仪快速定位PCB传输线故障?

村田贴片电容的阻抗匹配问题如何解决?

村田贴片电容的高频特性与阻抗匹配

传输线在阻抗匹配时串联端接电阻为什么要靠近发送端?

传输线在阻抗匹配时串联端接电阻为什么要靠近发送端?

评论