针对SerDes的电感线圈怎么设计?ESD有什么特殊要求?

设计SerDes的电感线圈和防静电保护(ESD)有着重要的意义。SerDes(串行器/解串器)是用于数据传输的一种技术,它将并行数据转换为串行数据,允许高速数据在远距离传输。电感线圈在SerDes电路中的作用是为了增强信号的强度和稳定性,而ESD防护则是为了保护电路免受静电放电的干扰。

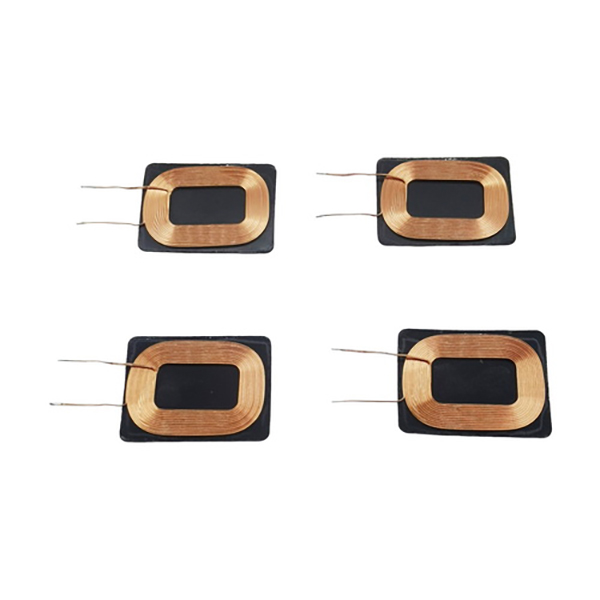

首先,我们来讨论电感线圈的设计。电感线圈在SerDes电路中起到滤波和阻抗匹配的作用。设计电感线圈时,首先要确定所需的电感值和电流能力。电感值的选择应根据系统的需求来确定,通常在几纳亨到几微亨之间。对于高频应用,线圈的自谐频点应大于最高的工作频率,以避免各种损耗。电感线圈的电流能力应与应用的最大电流需求相匹配。

其次,线圈的材料选择也很重要。常见的电感线圈材料包括铜线和铁磁材料。铜线具有良好的导电性和低电阻,适用于高频应用。铁磁材料可以增加线圈的感应电感,并减小尺寸。此外,线圈的尺寸也需要根据系统的要求来确定,通常使用层状线圈以减小尺寸。

ESD防护对于SerDes电路的稳定性和可靠性至关重要。ESD是指由于两个或多个物体之间的静电放电而引起的短暂放电现象。在SerDes电路中,ESD可以对设备和线路产生损坏或干扰,因此需要进行充分的防护。

ESD防护的设计涉及到多种方法和组件。首先,为了防止ESD放电通过线路传递到SerDes芯片,可以在芯片输入和输出接口处添加ESD保护二极管。这些二极管可以提供额外的电流路径,将ESD放电引离芯片。其次,还可以在板级设计中添加ESD防护电路,如ESD TVS二极管和陶瓷电容等。这些组件可以在ESD事件发生时提供快速消散电流的能力,从而保护电路不受损害。

此外,在SerDes电路的PCB设计中,还需要注意布线和地线的规划。合理的布线可以降低ESD干扰的机会,而良好的地线规划可以提供低阻抗路径,帮助消除ESD放电引起的噪声。

总结起来,设计SerDes的电感线圈需要考虑电感值、电流能力、材料选择和尺寸等因素。而ESD防护则需要考虑在芯片和板级设计中添加适当的保护组件和合理的布线规划。这些都是确保SerDes电路稳定和可靠性的重要方面。通过仔细设计和实施这些措施,可以提高SerDes电路的性能和可靠性,从而实现高速数据传输和可靠通信。

所以,设计SerDes的电感线圈和ESD防护对于设备的正常运行和性能至关重要。只有通过详尽、详实、细致地考虑和实施这些设计要求,才能确保SerDes电路的稳定性和可靠性,最终提供高质量的数据传输和通信。

-

ESD

+关注

关注

50文章

2422浏览量

180395 -

SerDes

+关注

关注

8文章

236浏览量

36981

发布评论请先 登录

给医疗设备CT/ICU配UPS,有哪些不容忽视的特殊要求?

磁环电感线圈的奥秘

从匝数到电感量:磁悬浮线圈的电磁设计要点

谷景带您探秘磁环电感线圈作用与绕线工艺

无线充电系统的心脏:TWS耳机对耳充电感线圈技术剖析

高功率系统关键组件:大电流电感线圈的设计与应用原理

激光焊接机在焊接电感线圈的工艺流程

苏州谷景磁环电感线圈的稳定效能与选择考量

变压器电感线圈:电子能量转换系统中的关键基础元件

电网关键节点的电能质量监测装置的现场校准环境有哪些特殊要求?

三星电容在汽车电子领域的应用有哪些特殊要求?

超高频谐波的监测对电能质量监测装置有哪些特殊要求?

激光焊接技术在焊接电感线圈工艺中的应用

针对SerDes的电感线圈怎么设计?ESD有什么特殊要求?

针对SerDes的电感线圈怎么设计?ESD有什么特殊要求?

评论