一站式PCBA智造厂家今天为大家讲讲在高速PCB设计中为什么信号线不能多次换孔。为什么在高速PCB设计中,信号线不能多次换孔?大家在进行PCB设计时肯定都接触过过孔,所以大家都知道过孔对PCB信号质量的影响很大,先给大家介绍一下我们在PCB设计时过孔应该如何选取。

通常有三种类型的过孔可供选择:(单位是mil)

8/16±2mil 10/20±2mil 12/24±2mil

通常,当板子比较密的情况下,我们会使用8/16±2mil(8/14,8/16,8/18)大小的过孔,当板材相对空旷时,可选择12/24±2mil(12/22,12/24,12/26都可以)大小的过孔,10/20之间可以使用10/20±2mil(10/18,10/20,10/22)大小的过孔。

就经济效益而言,我们过孔越大,成本越低,所以我们要控制板材的成本,在满足我们的设计的同时,尽量把过孔设置大一点。

当然在HDI板子当中,我们通常需要盲埋孔。通常,我们的盲孔的大小范围为4/10±2这样,它通常可以击中焊盘,但需要注意的是,它不应该击中焊盘的中心。它通常可以击中焊盘的边缘,这样在工艺处理方面会更好。

所以我们的过孔越大越好还是越小越好,显然不是这样的。

从工艺的角度来看,我们的过孔内径不能小于板厚的1/7,为什么?

因为当我们的过孔小于1/7时,由于工艺技术的影响,我们不能在过孔孔壁上均匀镀铜,当我们不能均匀镀铜时,我们板的电气性能就会受到影响。因此,当板厚较大时,我们也应该增加过孔。

我们上面的结论是,最好是穿过更大的洞。此时,我们需要向您介绍两个公式。一个是过孔寄生电容的计算公式:C=1.41εTD2/(D1-D另一个是寄生电感的计算公式:L=5.08h[ln(4h/d)+1]。

先来看看过孔寄生电容计算公式:

ε:板材的介电常数,通常不同板材的介电常数也不同,T:指板的厚度。

假设过孔是在GND在这种情况下,D1值为过孔边缘与铜皮之间的避让距离(反焊盘),D2:指过孔的外径。

我们可以从上面的公式得出结论:

1. 在板和板厚度不变的情况下D寄生电容越大,寄生电容越小,C与D1成反比关系。

2. 在板材和厚度不变的情况下D寄生电容越大,寄生电容越大,C与D2成正比关系。

3. 在板厚和D2,D在不变的情况下,板材的介电常数越大,寄生电容越大,C与ε成正比关系。

4. 介电常数及D2,D板厚T越大,寄生电容越大。

在普通PCB设计中,过孔寄生电容和寄生电感对PCB设计影响不大,可以进行常规选择。但是在高速下。PCB通过对上述过孔寄生特性的分析,我们可以看到中间过孔设计在高速下PCB在设计中,看似简单的过孔往往会给电路设计带来巨大的负面影响。

为了减少过孔寄生效应的不利影响,在设计中可以尽可能做到:

1) 选择合理的过孔尺寸。对于多层一般密度PCB在设计上,选择10/20/36POWER隔离区)过孔较好;对于电源或地线的过孔,可考虑使用较大的尺寸,以降低阻抗;

2)POWER隔离区越大越好;

3)PCB信号走线尽量不要换层,即尽量减少过孔;

4)使用较薄的PCB两种寄生参数有利于减少过孔;

当然,设计中需要分析具体问题。综合考虑成本和信号质量,在高速下PCB在设计时,设计师总是希望孔越小越好,这样板上的布线空间就越大。此外,孔越小,其自身的寄生电容越小,更适合高速电路。

在高密度PCB在设计中,非过孔(盲埋孔)和过孔尺寸的减小带来了成本的增加,过孔尺寸不能无限减小,受到影响PCB制造商在高速下限制钻孔和电镀等工艺技术PCB在过孔设计中应考虑平衡。

然后,在了解了以上信息后,我们就会知道为什么在高速PCB设计中,我们不能不能打过多的过孔了。过孔本身会带来寄生电容和寄生电感。过孔越多,寄生电容和寄生电感的值就越大。所以这就是为什么很多数据手册上面会写我们布线时过孔的数量不能超过多少个,一般我们的高速信号线采取不能超过三个过孔的原则,能不打孔就不打孔。

关于在高速PCB设计中为什么信号线不能多次换孔的知识点,想要了解更多的,可关注领卓PCBA,如有需要了解更多PCB打样、SMT贴片、PCBA加工的相关技术知识,欢迎留言获取!

审核编辑 黄宇

-

高速PCB设计

+关注

关注

2文章

51浏览量

15629 -

信号线

+关注

关注

2文章

185浏览量

22158

发布评论请先 登录

Altium Designer中信号线束的使用

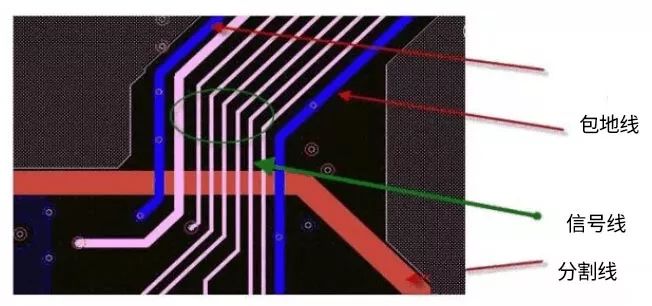

高速PCB设计中走线屏蔽的各项规则解析

PCB设计EMI的高速信号走线规则

高速PCB设计中信号完整性研究综述

为什么在高速PCB设计当中信号线不能多次换孔

在高速电路设计中,如何应对PCB设计中信号线的跨分割

为什么高速PCB设计中信号线不能多次换孔

为什么高速PCB设计中信号线不能多次换孔

评论