一前言

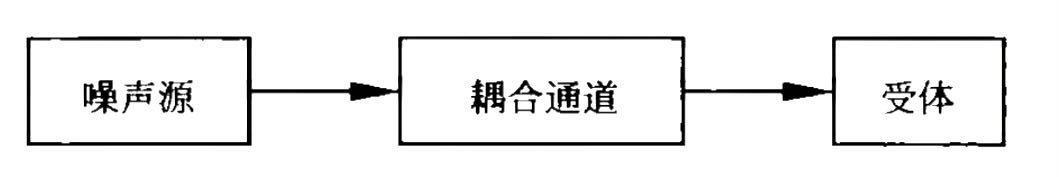

噪声的抑制是电磁兼容领域一直围绕的一个重要问题之一,而在噪声的抑制过程中“噪声的耦合”则让噪声的抑制变得更加的复杂多变,使得噪声抑制的难度再次提升,所以想要做好噪声的抑制了解噪声的耦合是必不可少的课题。

二噪声的耦合方式

噪声的耦合方式大致可以分为以下几种:

直接耦合:

1.传导耦合--传导耦合是指俩个功能系统的电路存在着直接接触的部分,那么只要其中一个电路存在噪声源,噪声就有可能会从产生噪声的系统电路通过传导耦合到受干扰的系统电路;

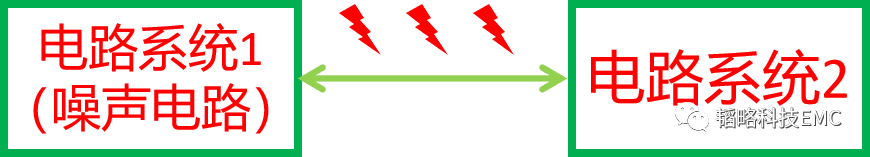

下图为传导耦合的简单电路模型:

传导耦合电路模型图(1)

间接耦合(空间耦合):

2.电场耦合--电场耦合是指由于噪声电场的存在,而系统电路中存在电解质,使得噪声电流在电路中产生了感应位移电流,相应的模型可以指定为寄生电容的耦合;

3.磁场耦合--磁场的耦合指的是变化的磁场可以通过法拉第定律在导体中诱发电流,而不需要噪声源和受干扰电路之间有直接接触。

对于一个电路系统中,往往电场耦合和磁场耦合是同时存在的。

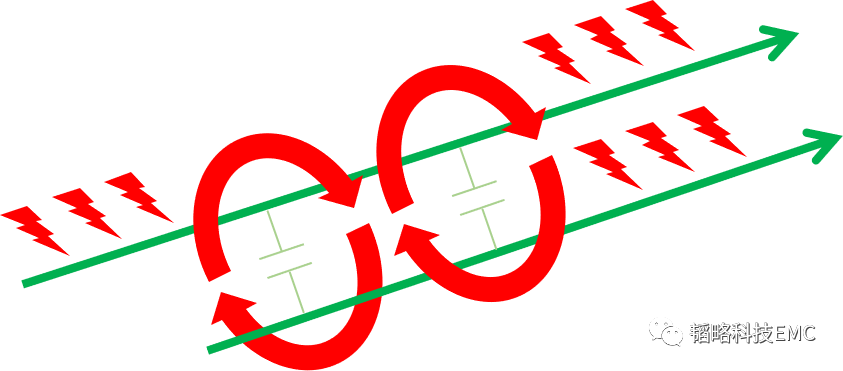

下图为空间耦合的简单电路模型:

空间耦合电路模型图(2)

三噪声耦合的预防

噪声的耦合的预防措施:

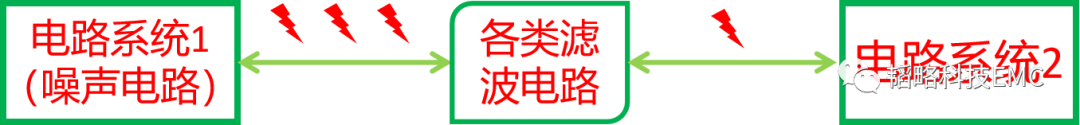

1.传导耦合:对于传导耦合噪声引起的问题,可以通过在两个电路系统的传输线上加滤波电路来抑制噪声电路产生的噪声传导到另外一个电路系统中去,而引起而更加复杂的EMC问题。具体的措施如:电容滤波,磁珠噪声抑制,共模电感,RC吸收、滤波电路等。这些可根据具体的电路来选择相应的措施。

电路系统之间增加滤波电路图(3)

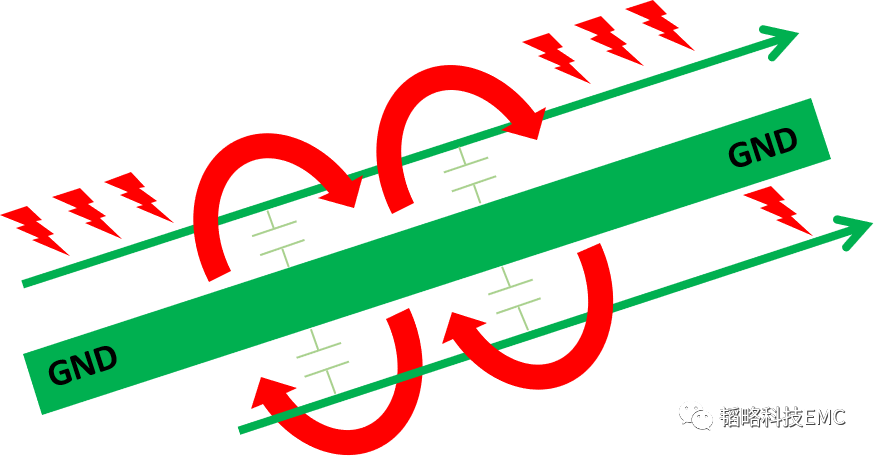

2.电场耦合和磁场耦合:对于空间耦合来说,可以通过屏蔽的方式来抑制耦合的强度,如PCB板的layout时把强干扰线进行包地屏蔽处理、强干扰线的前端增加滤波措施,减低对后端耦合强度。

耦合线之间增加GND屏蔽层图(4)

四案例分析

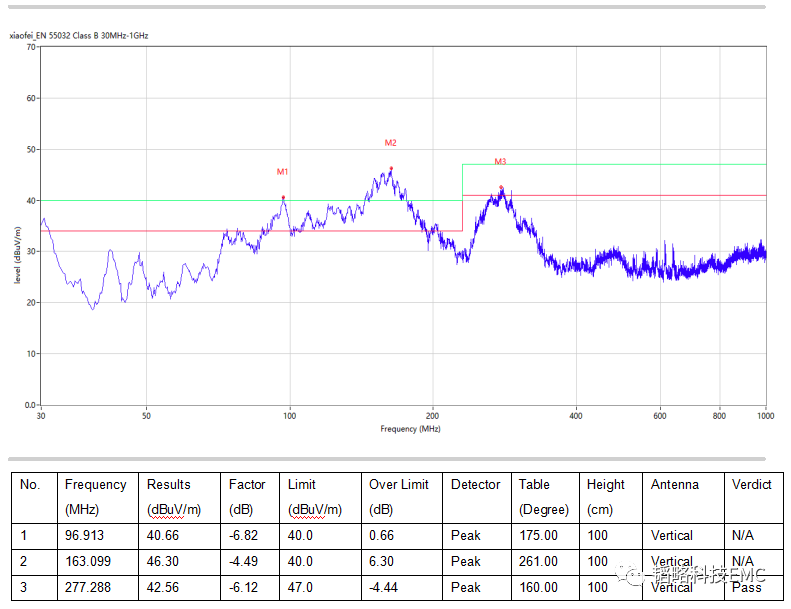

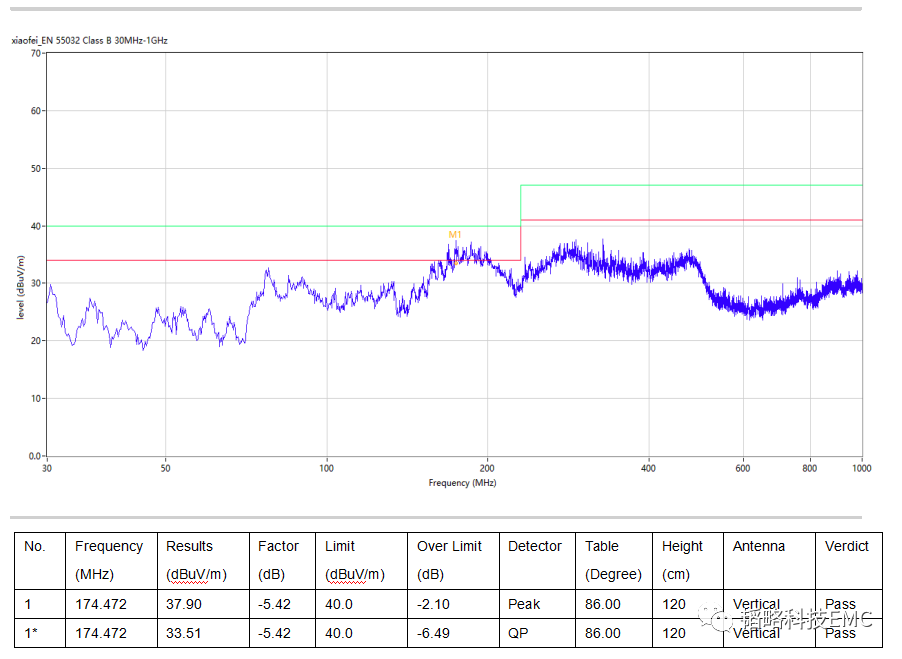

接下来给大家分享一个噪声耦合的经典案例,该案例是一款无线充产品,先看一下前期的摸底数据:

摸底测试图(5)

分析:通过对产品的分析,可以得知该款产品的强噪声源就是无线充芯片的输出时SW脚带来的辐射问题。

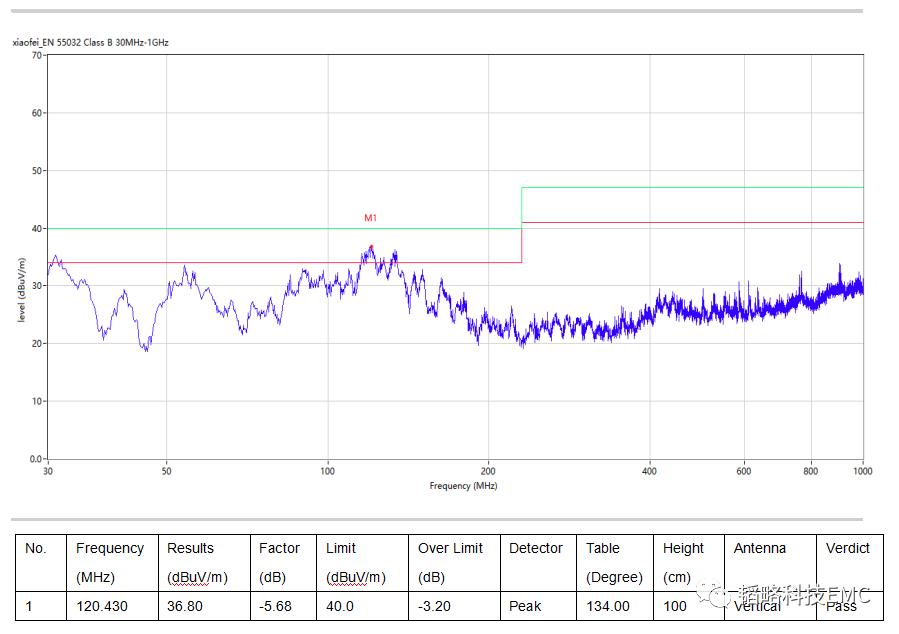

输入端绕磁环测试图(6)

分析:通过对电源适配器到产品的输入端套磁环可知,该产品的辐射是通过外接的适配器线缆辐射出来的。外部线缆由适配器的电源线和数据线组合而成。

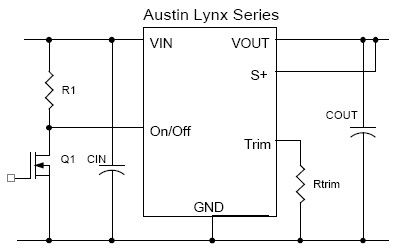

措施:在电源端入共模电感来抑制电源端辐射出来的噪声强度,但这个措施做完后发现对噪声的抑制一点效果都没有体现出来。

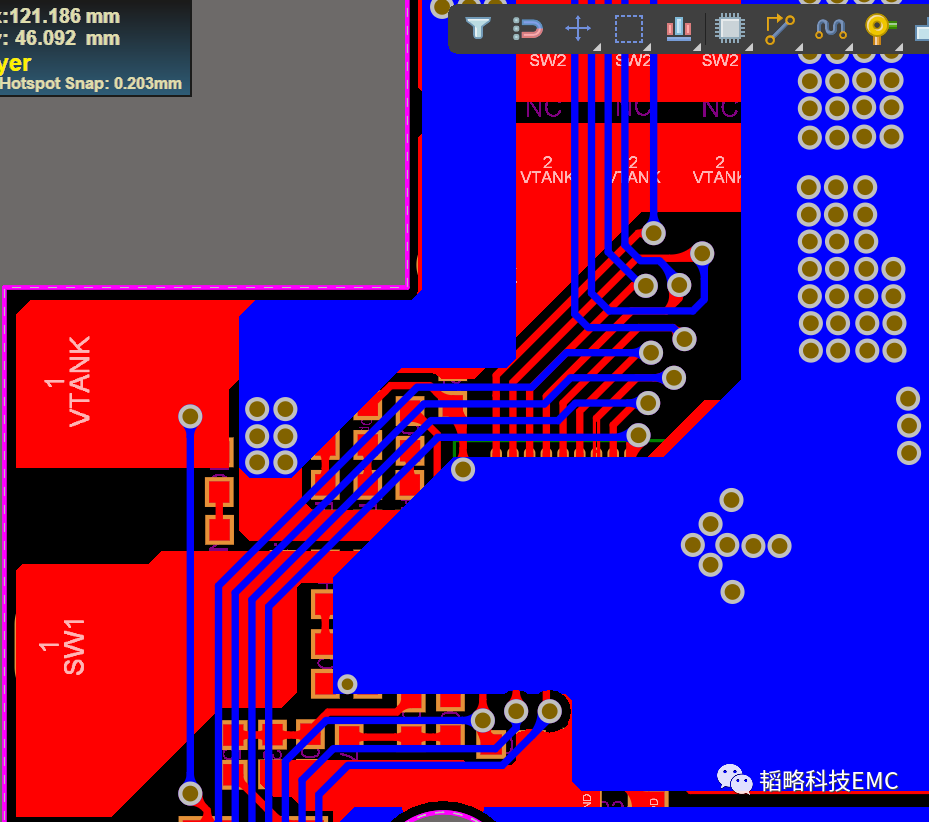

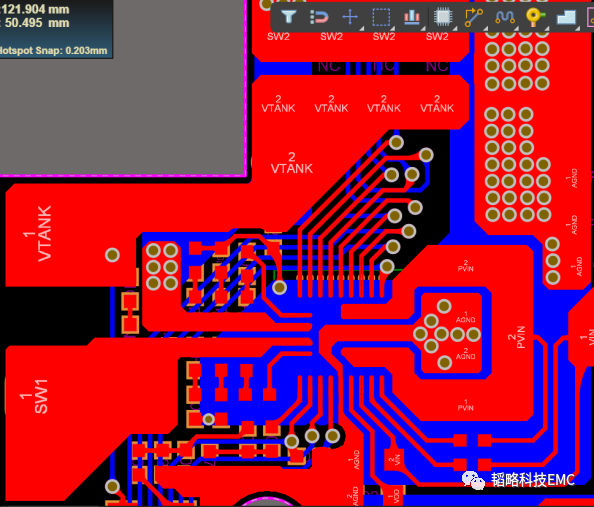

分析:电源端措施处理无效后,基本可以把重点转移到数据线上的问题,但正常来说适配器数据线上的噪声应该远低于供电端的才对,通过对PCB的排查,最后发现,芯片的SW输出脚布板时把数据线布在了SW脚的下方,这使得强噪声源通过对数据线的空间耦合,噪声从数据线辐射了出来,布板如下图:

芯片SW脚PCB图(7)

芯片SW脚PCB图(8)

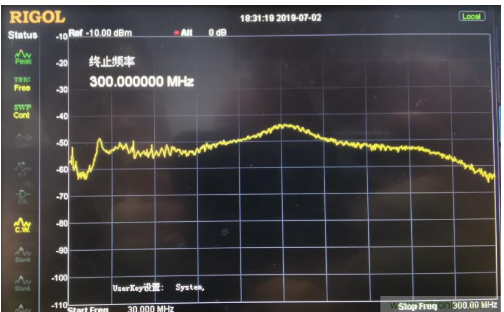

措施:在输入接口处数据线上加滤波电容。

加滤波电容后测试图(9)

分析:辐射的强度有明显下降,可以通过测试标准,证明数据线通过空间耦合到了SW脚的强噪声,使得在供电端加共模电感无效。空间耦合的问题往往是在PCB设计过程中容易给忽略的,这往往会引起一些难以判断的EMC问题。

五总结

“噪声的耦合”是电磁兼容一直围绕的一个重点问题之一,通过这次的分享,希望能给大家能从中得到收益,在产品的前期的设计过程中尽量去规避掉可能存在的“噪声耦合”问题,产品的EMC问题自然会有极大的减少。

审核编辑:刘清

-

emc

+关注

关注

177文章

4452浏览量

192271 -

寄生电容

+关注

关注

1文章

303浏览量

20372 -

电容滤波

+关注

关注

6文章

61浏览量

58793 -

噪声抑制

+关注

关注

0文章

35浏览量

12541 -

磁场耦合

+关注

关注

0文章

8浏览量

5309

原文标题:噪声的耦合与预防

文章出处:【微信号:TLTECH,微信公众号:韬略科技EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

EMC之噪声耦合整改案例分享

问一个耦合噪声的问题

串扰之耦合的方式

电源噪声是怎么对VCO造成影响的?是由于电容的耦合吗?

如何通过噪声源和耦合途径来抑制输出电压噪声

VL53L1X远距离测距传感器如何减轻噪声耦合?

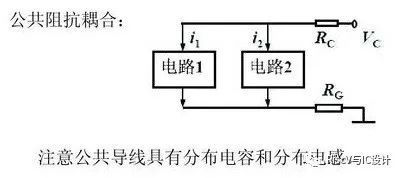

公共阻抗耦合噪声的抑制方法

可减少负载点转换器模块的噪声耦合的PCB布局

电路中产生公共阻抗耦合噪声的具体原因分析

技术资讯 I 面向电路的噪声耦合抑制技术

集成运放电路采用直接耦合方式是因为什么

技术资讯 I 容性耦合噪声抑制方法如何减少串扰

噪声的耦合方式 噪声耦合的预防

噪声的耦合方式 噪声耦合的预防

评论