随着信号速率-AMI模型在信号完整性仿真中应用越来越多,本文主要介绍了IBIS-AMI模型的基础知识和建模方案。IBIS-AMI模型建模一般采用SystemVue或者ADS这两个工具都能分别完成。

IBIS 模型

IBIS模型出现之前,系统仿真使用的模型主要是Spice模型,SPICE (Simulation Program with IntegratedCircuit Emphasis)是一种通用的电路模拟语言,其对应的网表文件可以作为用于描述器件内部实际电气连接的器件模型。SPICE模型包含详细的晶体管结构和具体的工艺技术,因此模型精度很高,但与此同时,由于其包含有过多有价值的信息,多数芯片厂商往往不会提供SPICE模型给客户。另外,SPICE模型是电路级仿真,其仿真时间与电路复杂度直接相关,在芯片集成度越来越高、电路越来越复杂的今天,SPICE模型仿真往往计算量巨大、需要耗费大量时间,只适用于电路级的设计者使用。

为了解决这些问题, IBIS模型应运而生了

IBIS (I/O Buffer Information Specification) 是一个公开的且已经成为行业标准的数字电路输入输出建模规范。它是基于I/V、V/T曲线的用于描述芯片I/OBuffer行为级特性的模型,能够反映芯片驱动和接收的电气特性。芯片厂商很容易便可以在不透露知识产权的同时提供给客户IBIS模型,以便在IBIS兼容仿真器(如ADS)中使用。并且与等效电路SPICE模型相比,IBIS的仿真速度要快的多。

为了建立统一的IBIS 模型,EDA厂商、IC供应商和最终用户成立了一个IBIS格式制定委员会,以推出并不断修订IBIS模型规范。

IBIS 模型虽然强大,但是也不能解决数字电路仿真中出现的所有问题。高速串行总线在使用过程中经常会出现一类问题:由于链路较长或者由于频率较高,而造成信号衰减过大,从而导致在接收端无法正确判别信号,所以这类SerDes架构的串行总线芯片都会有集成均衡或加重电路,尤其是接收端通常包含较复杂的均衡电路。而普通的IBIS模型无法对这样复杂的均衡算法电路进行描述,

为了解决高速串行仿真在速率较高时带来的问题,从IBIS 规范5.0开始,定义了新的IBIS AMI (Algorithmic Modeling Interface)模型,来实现IBIS模型无法描述的均衡算法功能。

AMI模型

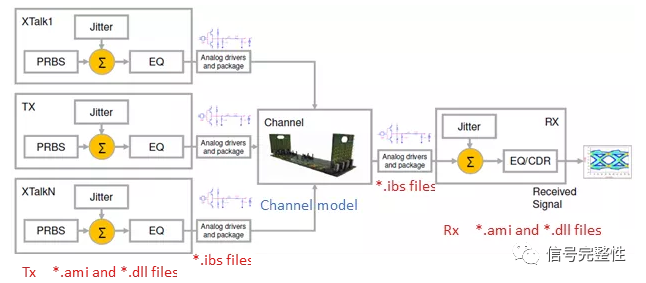

AMI(Algorithimic Model Interface)模型是IBIS协会制定的一种模型分析方法。在这一个分析方法当中,芯片厂商可以利用C++代码建立模型,描述芯片内部功能电路的行为,然后将代码编译为动态链接库(.dll),从而保护芯片内部设计的知识产权。对系统集成商而言,一旦从芯片厂商取得AMI模型,其开发工程师便可以结合自己设计的通道模型搭建成高速数字传输系统,通过软件仿真来估算系统的眼图(Eye Pattern)或者是误码率(BER),仿真时间只需数分钟到数个小时便可完成。实践证明使用IBIS AMI进行仿真的结果与实际测量通常具有相当高的吻合度,因而使用AMI模型进行系统仿真俨然已经变成整个产业的标准分析流程。

IBIS AMI 模型特点

与传统模型相比,IBIS AMI模型具有以下优点,更符合芯片厂商和硬件设计者的需求:

·兼容性:不同半导体芯片厂商生成的模型可以在同一电路中仿真。

·可移植性:相同的模型可以用不同的仿真软件来仿真分析。

· 高效率:10000000 bit的仿真可以在10 min或者更短的时间内完成。

·灵活性:模型支持统计和时域(bit-by-bit)分析模式。

·可优化:模型提供仿真控制参数(如抽头系数等),用户可以通过电路仿真器对各个参数进行扫描,优化,改善系统性能。

·知识产权保护: 芯片厂家只提供模型算法部分的加密动态链接库文件,以避免逆向设计。

IBIS AMI 建模挑战

IBIS AMI 模型由描述电气特性的传统的IBIS模型文件(*.ibs)、包含编译后算法的动态链接库文件(*.dll/*.so)以及参数描述文档(*.ami)三个文件共同构成。

*.ibs 文件:

○声明对应的AMI 参数文件和算法可执行文件*.dll,关键字为:

[Algorithmic Model]

[End Algorithmic Model]

○包含除均衡外的发射机特性:输出电压摆幅、输出阻抗、转换速度、输出寄生参数等。

○包含除均衡外的接收机特性:输入负载阻抗、寄生参数等。

*.ami 参数定义文件:

○[Reserved_Parameters]关键字中定义模型的处理流程,如:

Init_Returns_Impluse:是否有算法模型等效LTI冲激响应(若为TRUE,可用于统计模式)。

GetWave_Exists:若为TRUE,算法模型为 NLTV, 可通过AMI_GetWave 函数生成输出信号。

使用Tx_Jitter、Rx_Clock_PDF加入抖动参数等。

○[Model_Specific] 关键字中把仿真器的参数传递给相应的可执行模块。

*.dll/*.so 算法可执行文件:编译后的算法文件(不可读),是真正用于信号处理的文件。Windows系统中使用*.dll文件,Linux系统中使用*.so文件。

IBIS AMI模型的建模对芯片设计人员来说具有一定的挑战:需要同时具备电路知识、高速信号传输知识及仿真能力,以及编程能力。产品往往覆盖多种协议,如PCIe, USB, SAS, SATA, HDMI等等。并且随着产品的更新换代,设计人员需要不断地更新设计,同时保证每个模型的准确度,这也需要花费大量的时间和资源。

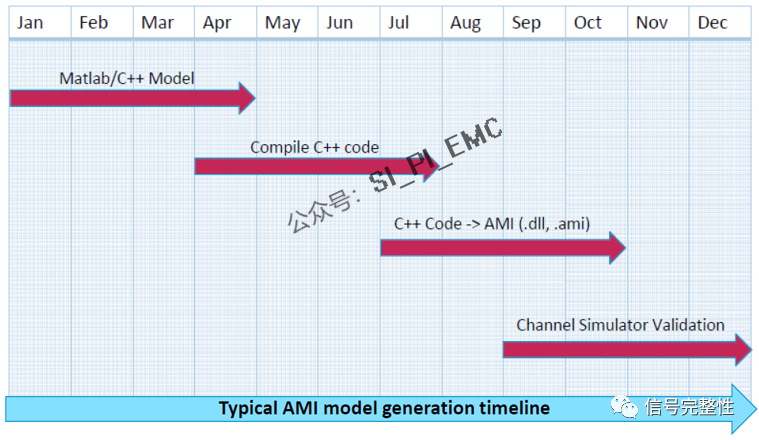

特别是对于没有建模经验的供应商而言,第一个IBIS AMI模型的建立往往需要花费半年到一年的时间才能得到第一代模型。而模型发布前还需要进行反复的验证和测试,以确保模型精度。传统的IBIS AMI建模周期如下图所示:

传统的IBIS AMI建模周期

对于系统工程师,及芯片厂商的客户而言,相比于芯片的获取,则可能需要等待较长的时间才能获取到对应的精确的AMI模型。

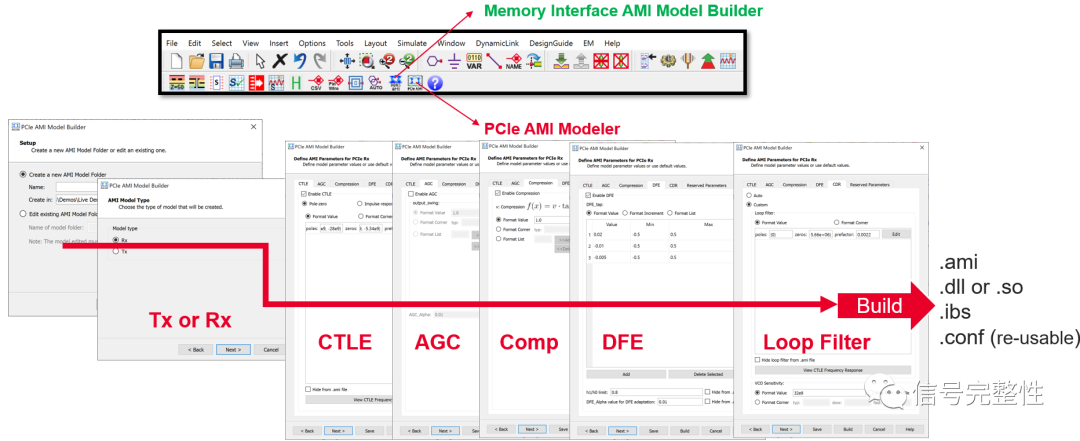

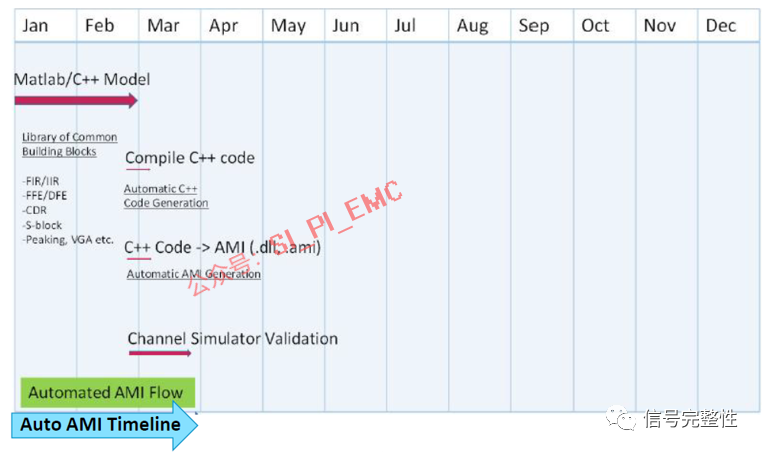

目前市场上能提供AMI模型建立以及测试工具的厂商很少,是德科技的 SystemVue以及 ADS是目前市场上被广泛采用的工具。SytemVue提供了图形化的界面以及丰富的模型库,芯片厂商可以在模型库里面挑选适当的元件搭建自己的发射/接收电路架构,随后即可以自动编译出AMI模型。ADS是业界高度认可的高速数字电路系统仿真平台,同时也是支持AMI模型非常完整的工具。最新的ADS也能支持IBIS-AMI模型的建模。

芯片厂商可以通过SystemVue以及ADS来加速AMI模型算法的开发以及验证测试工作。系统集成商也可以方便的使用这两种工具进行仿真以及测试,从而使得建模周期大大缩短:

使用PathWave SystemVue和PathWave ADS 缩短IBIS AMI建模周期

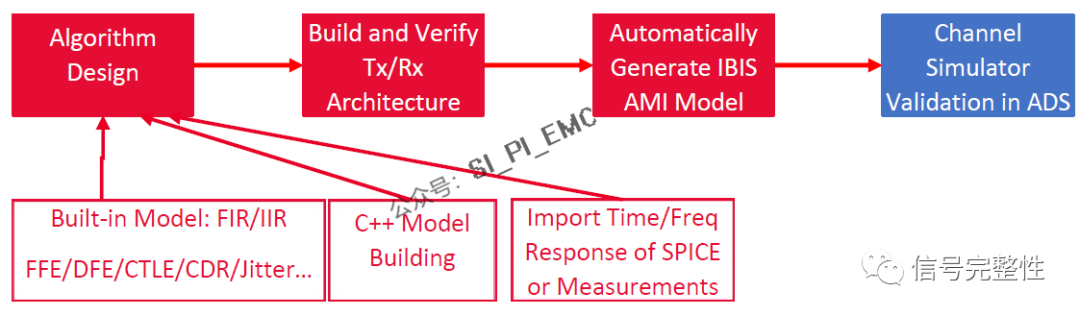

基于PathWave SystemVue的IBIS AMI 建模流程

PathWave System Design, 即原SystemVue软件,是专业的电子系统级仿真软件,能够为SerDes/DDR集成电路(IC)提供常用均衡算法及其他数字信号处理模块,一旦算法设计并优化完成,PathWave System Design即可自动生成通用的IBIS AMI模型。用户可将其导入通道仿真工具(如PathWave ADS)进行进一步的验证,或提供给客户,帮助他们设计包含有芯片特性的系统。

PathWave SystemVue提供一套自动化IBIS AMI建模流程,基于图形界面设计。用户可以使用软件内建的常用算法模型,来快速对Tx/Rx中所需的Pre-shoot/De-emphasis(预加重/去加重)、CTLE(ContinuousTime Linear Equalizer,连续时间线性均衡)、Adaptive DFE(Adaptive Decision Feedback Equalizer,自适应判决反馈均衡)以及CDR(Clock Data Recovery时钟数据恢复)等进行建模。同时,用户也可以导入自定义的C/C++代码或SPICE仿真或实际测量得到的电路时域/频域响应等,来更精确地对芯片实际算法结构进行建模。经过仿真验证后,用户即可使用软件提供的建模工具自动编译生成所需的AMI文件,以便提供给通道仿真工具(如ADS)进行进一步的验证。

IBIS AMI建模实例——SerDes模型库及AMI 建模工具

AMI模型设计工具用于高速数字IC常用的信号处理算法设计,可以在不使用AMI模型的情况下对SerDes链路进行架构优化,同时也是用于建立IBIS AMI模型的必要模型库。是高性能SerDes设计所必需的评估手段,帮助高速数字电路设计工程师利用物理层的信号处理手段以达到最大的互联性能。其中也包括光纤通信中的 SerDes模型。

主要特性

·快速优化信号处理过程。同时支持算法设计、验证及建模。

·在实施时无需经历麻烦和耗时的迭代过程。将经过优化的算法模型作为一个可执行的规范,一次就成功地实施经过优化的体系结构。

· AMI 是基于产品和架构的模型。基于此工具能支持快速、精确、自动化地建立模型,避免了将敏感 IP 透露出去的危险。IBIS AMI 封装程序可以确保标准一致性。

·无所有权加密。无需验证和保有多个版本。AMI 模型设计工具提供了“一次编程,随处可用”的功能。

·生成您需要发给客户的所有格式的文件:*.ibs、*.ami、*.dll(Windows 可执行)、*.so(Linux的交叉编译共享对象)。

·除了传统的Tx/Rx模型外,还可对中间通道中继器(Retimer/Redriver)和光纤通信链路进行建模。

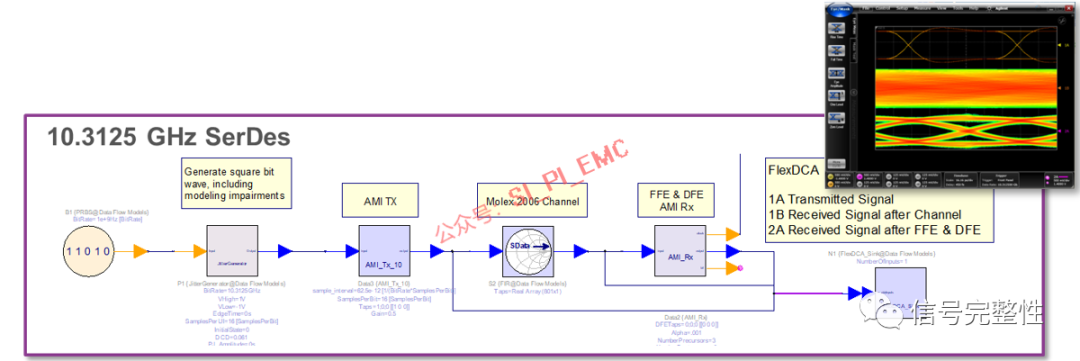

·可与常用示波器眼图分析软件(FlexDCA)进行互操作,以便在同样的眼图分析算法下比对软件仿真与硬件测试的结果。

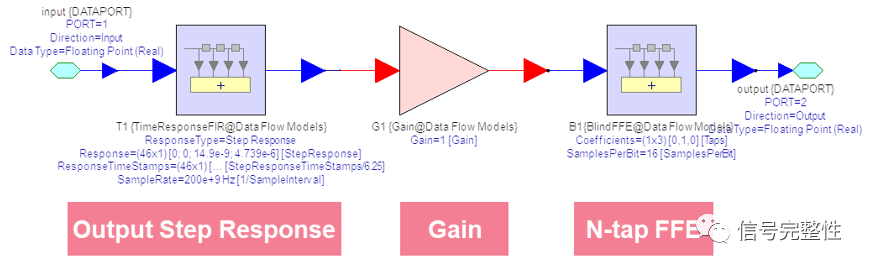

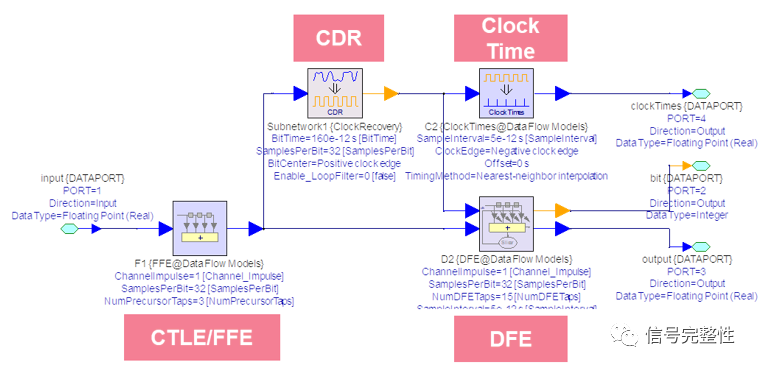

·提供丰富的均衡算法,可取代大量编程工作。包括Blind/Adaptive FFE(预加重/去加重), CTLE线性时间均衡, CDR时钟数据恢复 (可调整其中PLL, VCO各项参数),Blind/Adaptive DFE判决反馈均衡等复杂算法,也支持导入时域/频域响应、自定义C++算法。可基于算法模型灵活设计所需功能,如非线性放大器等。

·支持添加抖动参数或抖动模型。

·支持灵活的画图方式,可对任意节点处的结果进行时域/频域画图,也可对数据进行后处理。

·支持导入通道S参数,通道冲激响应/阶跃响应等以用于链路仿真验证。

·对于DDR5,提供独家的方式支持DQ和DQS输入。

10.3125GHz SerDes 链路及模型示例:

发射机模型架构示例:

接收机模型架构示例:

DDR5 IBIS-AMI建模

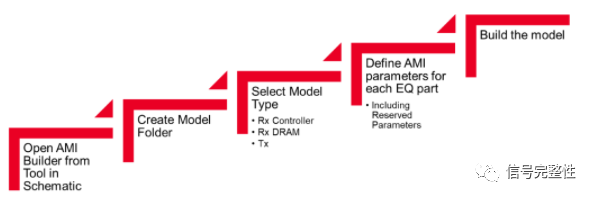

相较于串行总线,传输链路较短且损耗较低的DDR技术以往似乎一直没有用到均衡,但随着DDR5速率的提高(3200MTs ~ 8400MTs),愈发严重的码间干扰(ISI)等问题使得眼图难以张开,因此DFE等有效降低ISI的均衡算法也将应用于DDR5产品中。因此IBIS AMI 模型也将用于DDR5的仿真中。在ADS中能快速的建立DDR5的IBIS-AMI模型。其基本的建模流程如下:

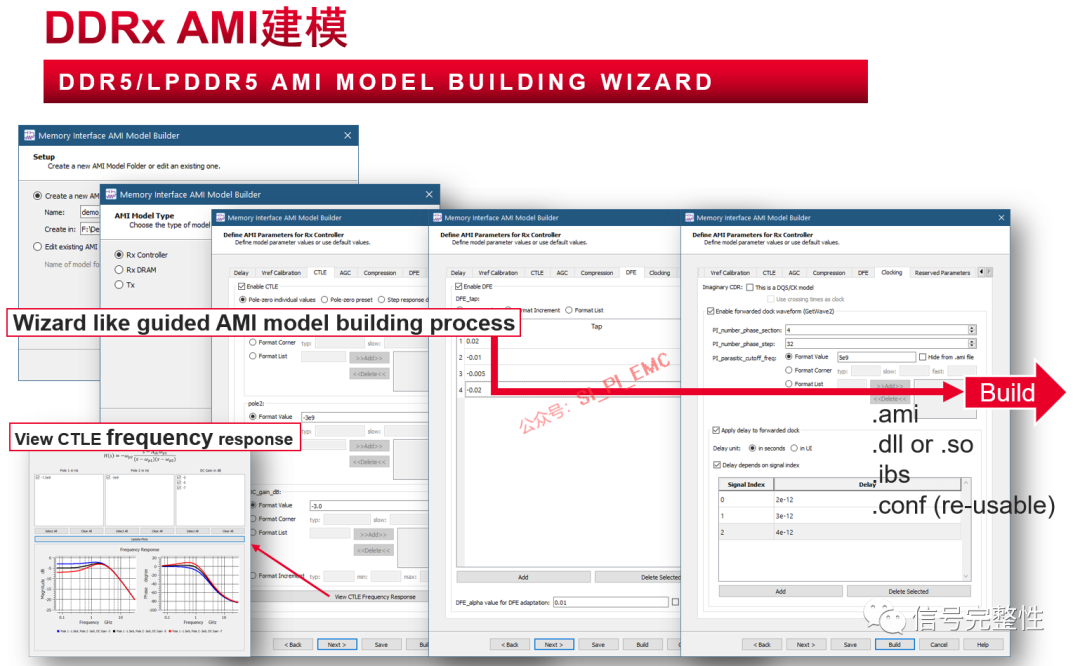

DDR5 AMI 建模向导如下图所示:

以Rx DRAM为例,包含如下功能选项(均参数可控),其中对时钟的处理与SystemVue所提供的方法一致,即可以DQS作为时钟触发,若不以DQS作为时钟,也可选择与SerDes类似的方法,使用内部CDR恢复时钟数据:

·Delay :(on signal index)为不同的信号线设置不同的delay参数。

·Vref Calibration:用于校准DC Offset,使之符合芯片中实际的DC Offset值。

·CTLE连续时间线性均衡

o Pole-zero 以零极点作为输入设置(也可设置多组参数供使用者选择)。

o Step/impulse response 输入仿真或测量得到的时域响应。

·AGC:output swing 实现信号可控增益。

·Compression:Non-linearity 模拟芯片中的电路非线性行为。

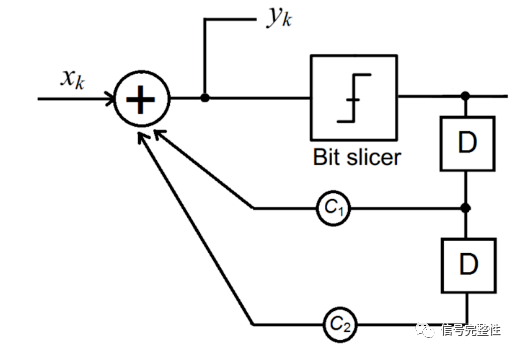

·DFE (adaptive)自适应判决反馈均衡

oInitial taps

oDFE_alphafor adaptation

·Clocking

oUse CDR if DQS/CK

o If not DQS/CK, support DQS as forwarded clock (当进行Controller建模时,增加Phase Interpolation 相位插值功能,以找到最佳时钟相位。)

oSupport delay

·Reserved Parameters

审核编辑:刘清

-

仿真器

+关注

关注

14文章

1053浏览量

88210 -

信号完整性

+关注

关注

68文章

1500浏览量

98264 -

SPICE

+关注

关注

6文章

199浏览量

44706 -

IBIS

+关注

关注

1文章

55浏览量

20662 -

AMI

+关注

关注

0文章

51浏览量

22734

原文标题:高速串行总线的IBIS-AMI建模详解

文章出处:【微信号:SI_PI_EMC,微信公众号:信号完整性】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于HyperLynx VX.2.4的IBIS-AMI仿真测试台构建方案

视频: Artix-7 FPGA:如何在大批量应用中使用高速SerDes

申请TI Keystone DSP PCIe SerDes IBIS-AMI Models。

高速互连IBIS仿真模型概述

WEBENCH接口设计工具助力IBIS-AMI通道仿真

如何对系统进行最佳建模

IBIS建模对电路板原型设计的重要性

Agilent推出ADS 2010支持IBIS-AMI 模型

有关IBIS 6.1的知识信息简介

TI Keystone DSP Hyperlink SerDes IBIS-AMI型号

高速串行总线-IBIS-AMI模型建模详解

高速串行总线-IBIS-AMI模型建模详解

评论