Interrupt Claim Process

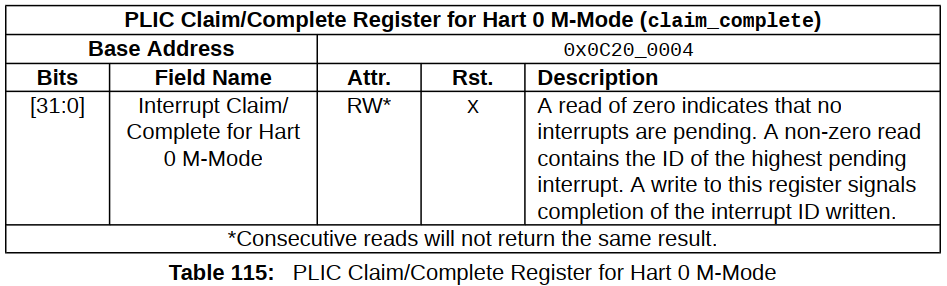

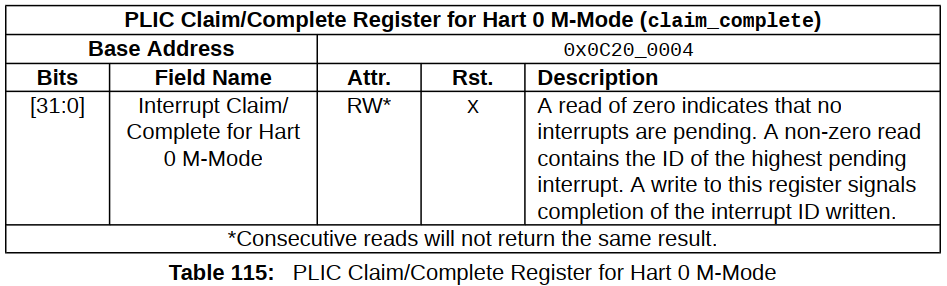

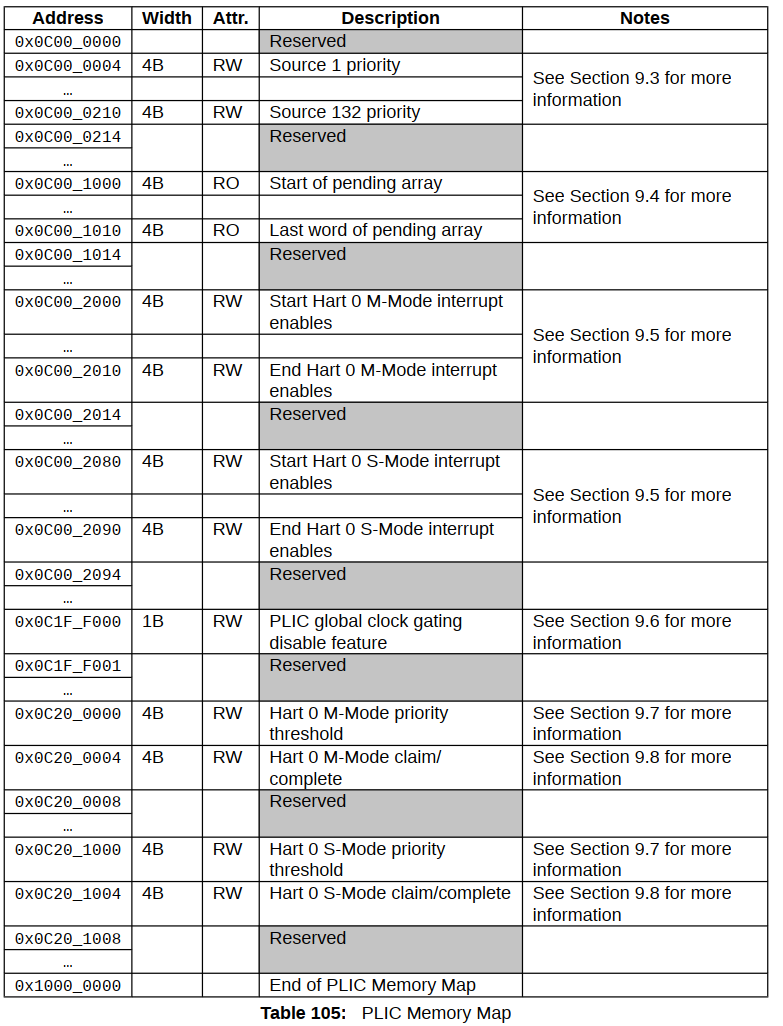

U54 内核 hart 可以通过读取 claim_complete 寄存器(表 115)执行中断请求,该寄存器返回最高优先级挂起中断的 ID,如果没有挂起中断则返回零。成功的声明还会自动清除中断源上相应的挂起位。

U54 内核 hart 可以随时执行声明,即使其 mip寄存器中的 MEIP 位未设置。

声明操作不受优先级阈值寄存器设置的影响。

中断完成

U54 内核 hart 通过将其从声明中收到的中断 ID 写入 claim_complete 寄存器(表 115)来表示它已完成执行中断处理程序。PLIC 不检查完成 ID 是否与该目标的最后一个声明 ID 相同。如果完成 ID 与当前为目标启用的中断源不匹配,则完成将被静默忽略。

PLIC 无法将新中断转发给已声明中断但尚未完成中断处理程序的完整步骤的 hart。因此,PLIC 不支持抢占单个 hart 的全局中断 。

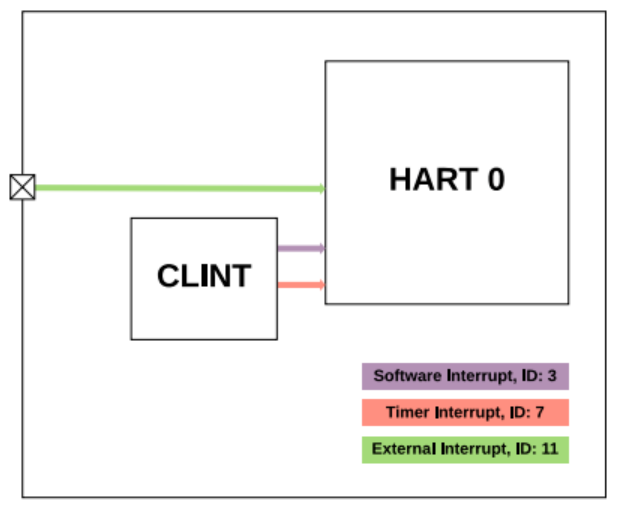

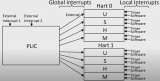

通过 PLIC 路由的全局中断的中断 ID 独立于本地中断的中断 ID。在退出处理程序之前,一旦初始声明/完成过程完成,PLIC 处理程序可能会检查其他未决的全局中断。此方法可以为全局中断保存额外的 PLIC 保存/恢复上下文。

PLIC中断处理例子

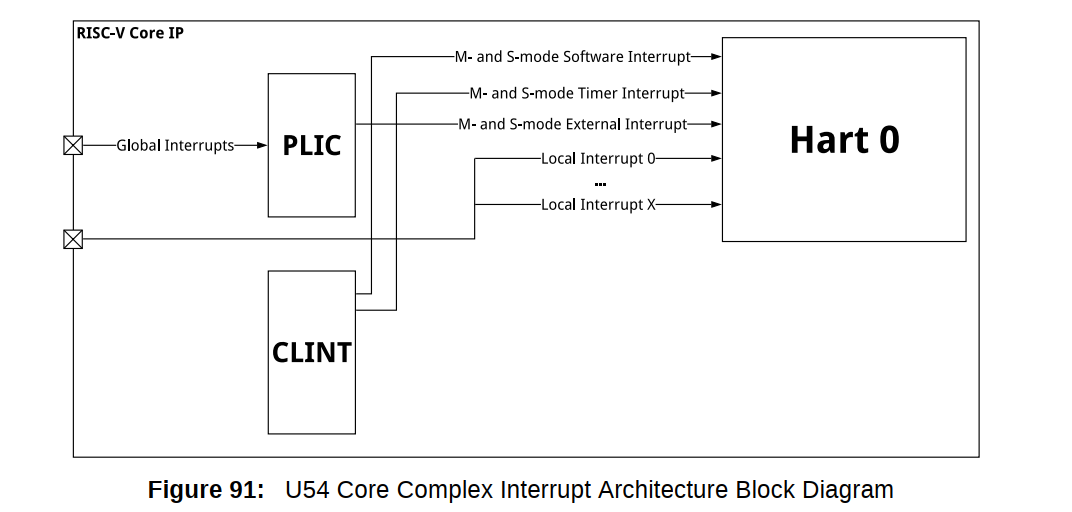

由于 PLIC 通过外部中断 #11 与 CPU 接口,因此外部处理程序必须包含一个额外的声明/完成步骤,用于与 PLIC 逻辑握手。

void external_handler() {

//get the highest priority pending PLIC interrupt

uint32_t int_num = plic.claim_complete;

//branch to handler

plic_handler[int_num]();

//complete interrupt by writing interrupt number back to PLIC

plic.claim_complete = int_num;

// Add additional checks for PLIC pending here, if desired

}

如果 CPU 读取 claim_complete 并返回 0,则中断不需要处理,因此不需要回写 claim/complete。

上面显示的 plic_handler 例程演示了一种实现软件表的方法,其中驻留在表中的函数的偏移量由 PLIC 中断 ID 确定。PLIC 中断 ID 对于 PLIC 是唯一的,因为它完全独立于本地中断的中断 ID。

-

控制器

+关注

关注

114文章

17860浏览量

195016 -

寄存器

+关注

关注

31文章

5618浏览量

130386 -

内核

+关注

关注

4文章

1474浏览量

43088 -

RISC

+关注

关注

6文章

485浏览量

86824 -

sifive

+关注

关注

0文章

37浏览量

9813

发布评论请先 登录

蜂鸟E203内核中断管理模块sirv_plic_man代码分析

浅析riscv中的plic与eclic

e203添加中断源,中断源无法使能怎么解决?

U54内核上CLINT的内存映射

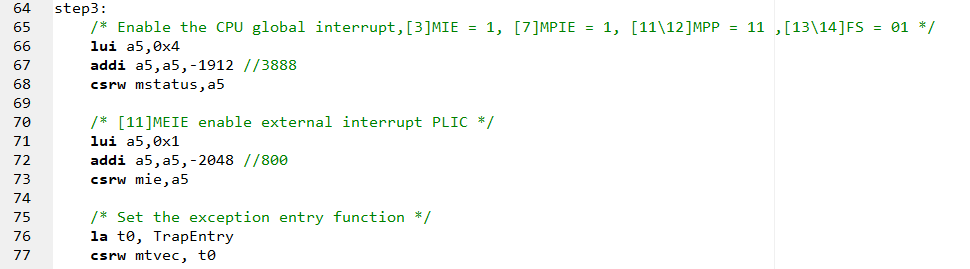

U54内核中断进入和退出

AS32X601驱动系列教程 PLIC_中断应用详解

U54内核PLIC中断处理例子

U54内核PLIC中断处理例子

评论