浅析riscv中的plic与eclic

1.PLIC中断处理

2.sifive中断的编程模型

3.关于eclic

4.关于jalmnxti

1.PLIC中断处理

在RISC V体系架构中,对中断有着一些定义,下面来分析一下这种定义的实现策略。

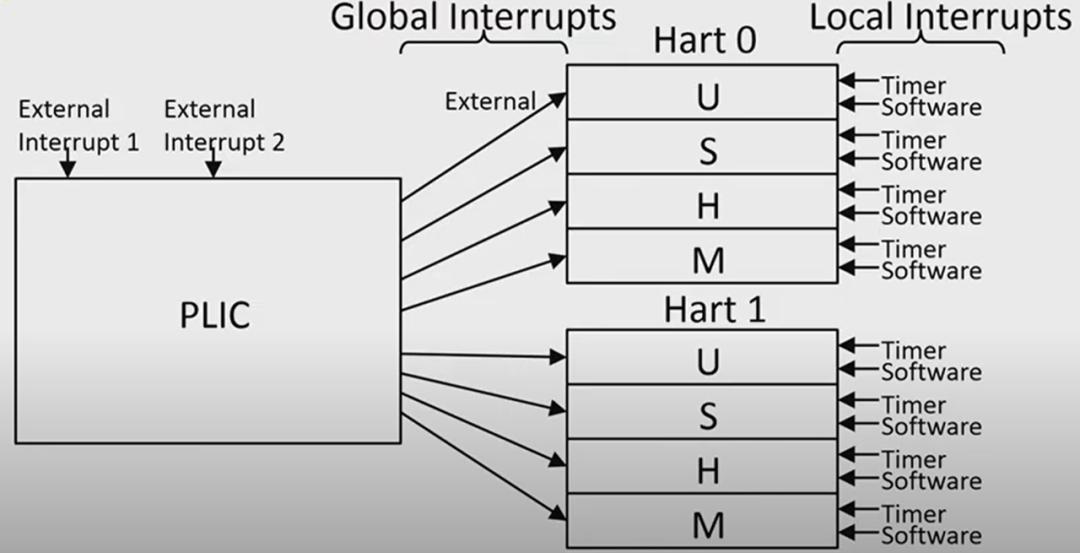

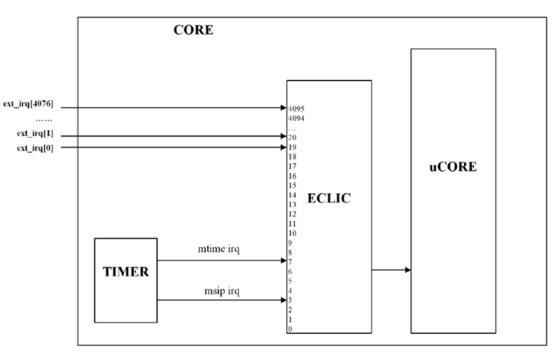

在riscv中一共定义了三种状态中断,对于hart层面,hart包含local中断源和global中断源。而local中断只有Timer和Software中断两种,而global中断则称为external interrupts。只有global中断源可以被PLIC core响应,通常为I/O device。

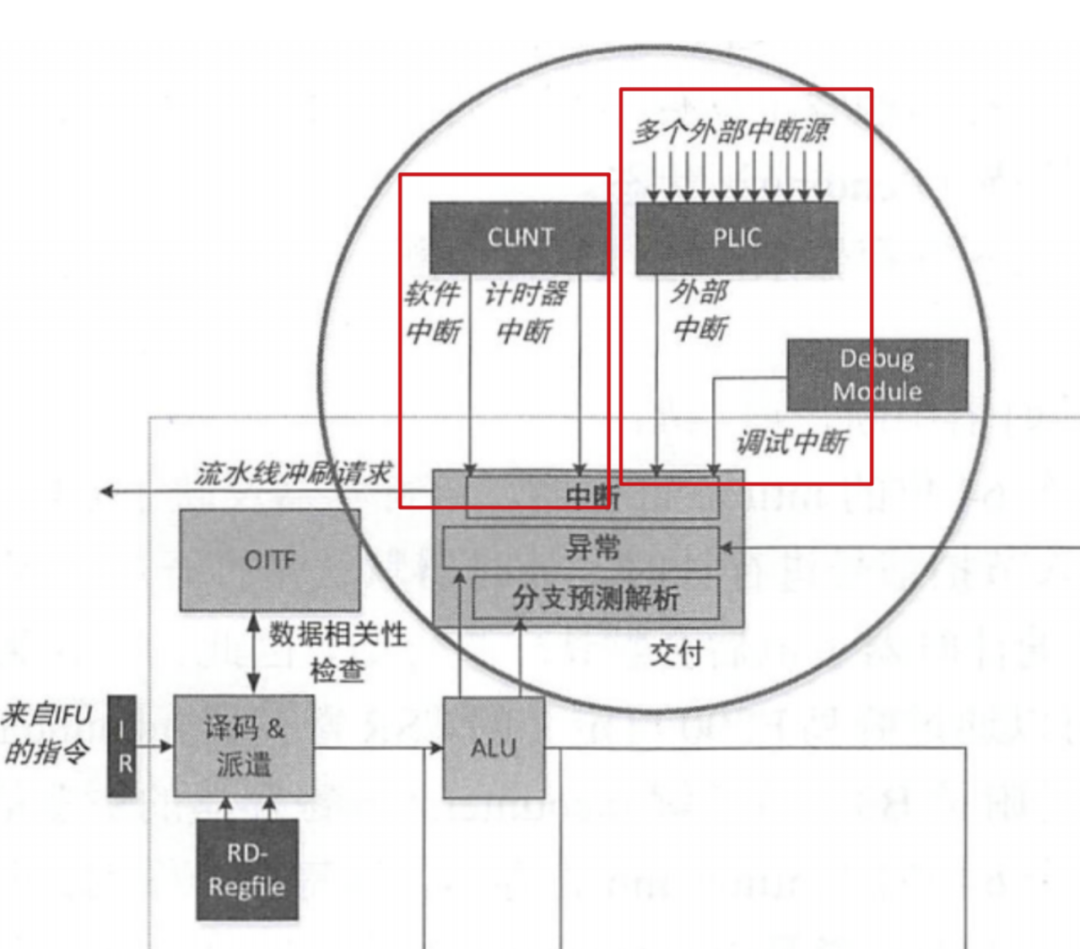

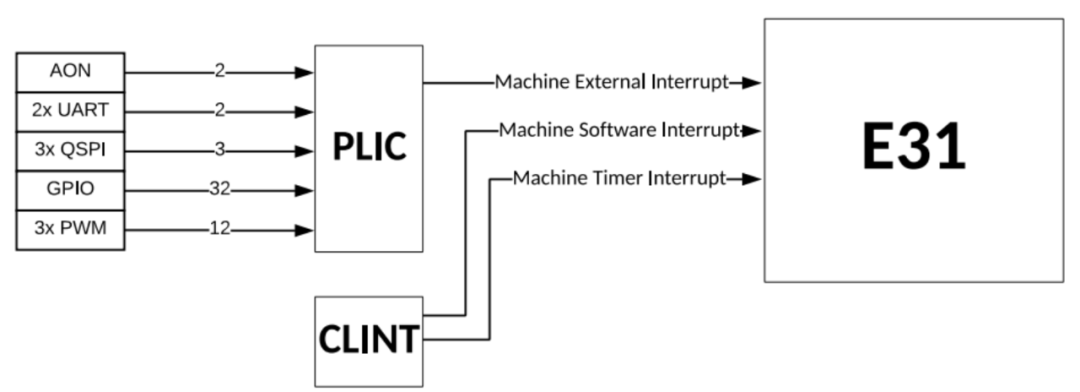

一般来说,timer和software是通过CLINT(CORE LOCAL INTERRUPT),而外部中断通过PLIC处理。

可以看一下蜂鸟处理器的处理流程,另外sifive的E31的中断也有如下的处理。

2.sifive中断的编程模型

中断处理过程有如下的流程

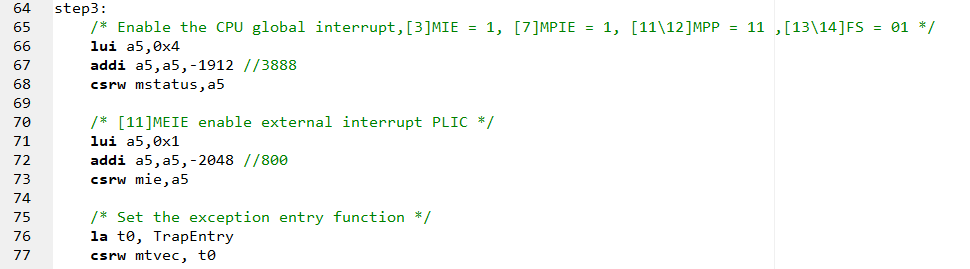

首先mstatus的MIE域被拷贝到mstatus的MPIE,然后mstatus的MIE域被清除。此时全局中断disable。

程序当前的pc值被拷贝到mepc寄存器中,然后pc值会根据mtvec的值设置其值。如果向量中断被使能,pc值会变成mtvec.BASE+4xexception处的代码。

从mstatus.MPP中取出特权模式的状态

接下来就是处理中断具体的函数实现

将特权模式的状态设置到mstatus.MPP

将mstatus.MPIE的数据拷贝到mstatus.MIE中

从mepc中取值放到pc中

最后执行eret恢复到程序正常运行的状态。

对于CLINT来说,有Software Interrupt和Timer Interrupt,可以直接在寄存器中控制。

而PLIC实际上可以理解为arm的中断控制器,存在其map地址。

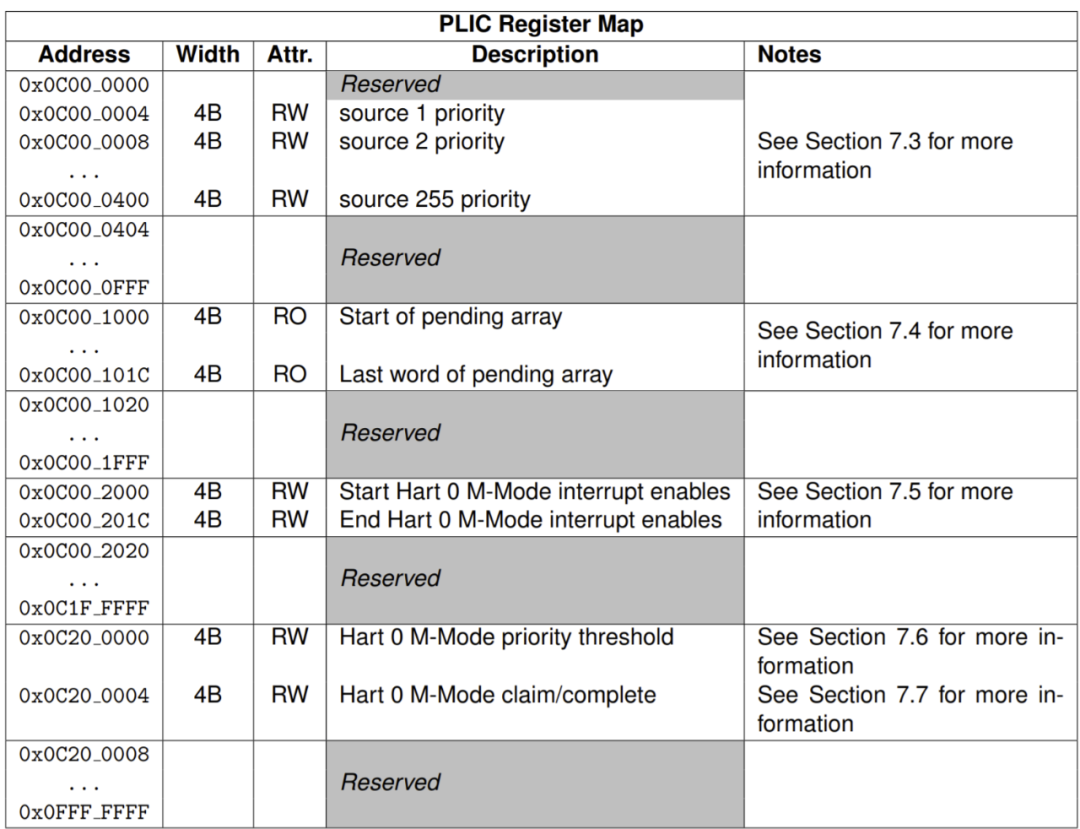

由于PLIC的使用是针对外部中断的,所以可以单独设置每个中断。可以设置如下的值:

中断的优先级priotity

中断挂起位pending

中断使能enables

中断阈值priority Thresholds

由于PLIC的实现是独立于hart的IP设计,所以其设计和布局也不一定完全一致。

3.关于eclic

eclic的设计是芯来科技设计的一种中断处理方式。

eclic目前也是众多芯来科技core采用的中断控制器,也包括gd32vf103系列的芯片。

3号中断是内核TIMER单元生成的软件中断。

7号中断是内核TIMER单元生成的计时器中断。

而从19~4095中断号都是外部中断,其中断的编号与中断的优先级其实没有关系。

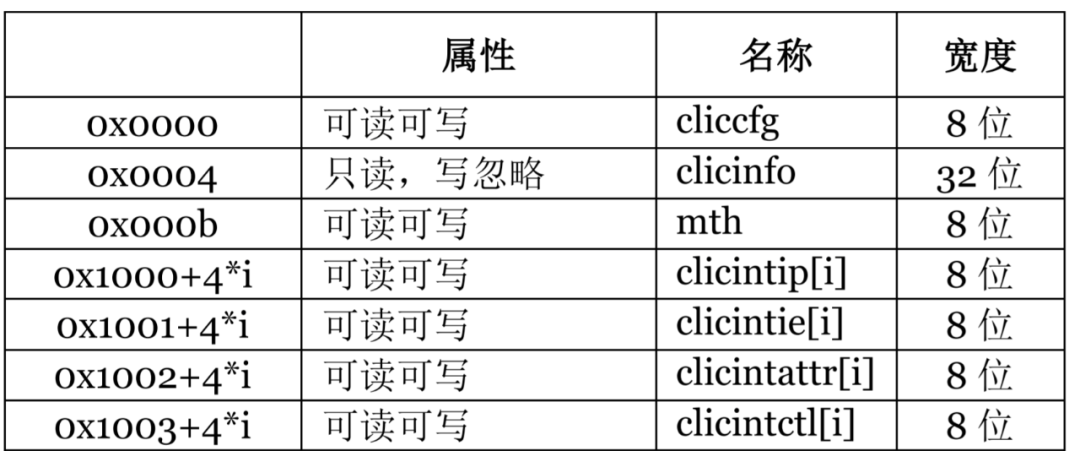

而对于ECLIC的寄存器布局,可见上图。

cliccfg是中断全局配置寄存器,可以结合clicintctl[i]配置

clicinfo也是全局寄存器中的数据,对于使用上来说,是只读的

mth中断的阈值级别寄存器

clicintip[i]是中断等待寄存器,也相当于pending寄存器

clicintie[i]为中断使能寄存器

clicintattr[i]为中断的属性,可以设置中断的上升沿触发或者下降沿触发,同时也可以设置中断从处理是向量中断还是非向量中断。

clicintctl[i] 设置中断优先级级别和优先级,需要配合cliccfg设置阈。

4.关于jalmnxti

这个也是eclic为了减少中断延时,加速中断咬尾的自定义指令。

该指令是配合eclic处理机制设计的,其指令功能比较多

开启中断使能,处理下一个中断

返回下一个中断入口地址

跳转至中断handler

中断处理后返回

由于csrrw ra, CSR_JALMNXTI, ra一条指令可以达到JAL(Jump and Link)的效果,同时硬件上更新Link寄存器作为该指令的PC作为函数调用的返回值,因此从中断服务程序返回后,又会重新回到csrrw ra, CSR_JALMNXTI, ra指令再次执行,可以重新判断是否有中断pending,如果有则跳转到中断处理函数,从而实现中断的咬尾处理,如果没有中断等待,则jalmnxti实际上并不会做任何事情。

原文标题:浅析riscv中的plic与eclic

文章出处:【微信公众号:嵌入式IoT】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

模型

+关注

关注

1文章

3648浏览量

51707

原文标题:浅析riscv中的plic与eclic

文章出处:【微信号:Embeded_IoT,微信公众号:嵌入式IoT】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

串口中断触发卡死怎么解决?

e203添加中断源,中断源无法使能怎么解决?

易灵思Sapphire SoC中RISC-V平台级中断控制器深度解析

从riscv底层原理分析gd32vf103的中断行为

RVMCU课堂「12」: 手把手教你玩转RVSTAR—外部中断篇

RVMCU课堂「10」: 手把手教你玩转RVSTAR—处理器内部中断篇

人脸识别和AES加密协同的SOC设计架构

利用蜂鸟E203搭建SoC【2】——外部中断扩展与验证

DDR200T运行plic中断例程LED无反应的解决办法

蜂鸟E203内核中断管理模块sirv_plic_man代码分析

中断机制在计算机系统中的作用,如何在e203处理器中利用外部中断来处理用户输入输出

AS32X601驱动系列教程 PLIC_中断应用详解

riscv中的plic中断处理与eclic详解

riscv中的plic中断处理与eclic详解

评论