特权模式中断

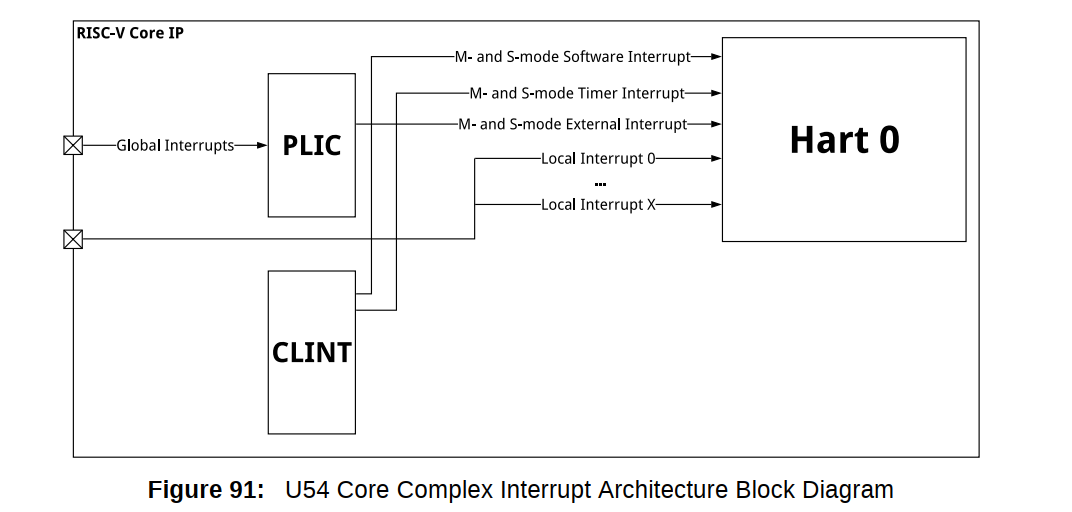

U54内核支持有选择地将中断和异常定向到S模式。

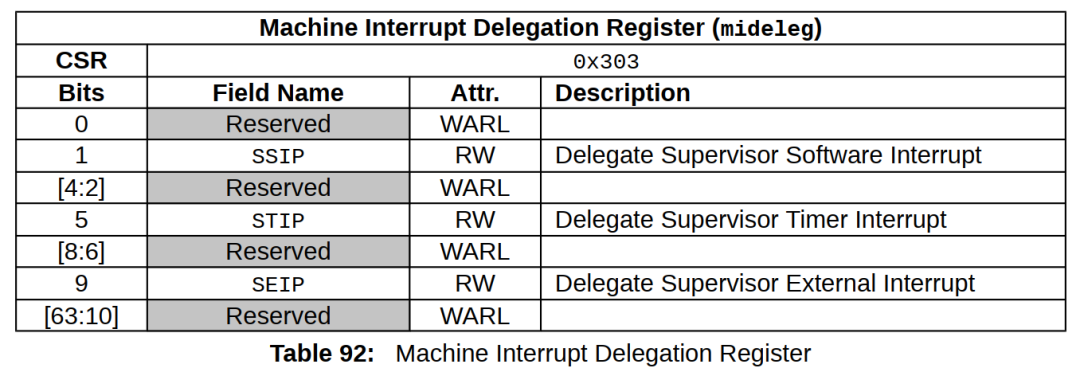

该功能由中断和异常委托CSR处理:mideleg和medeleg。S模式中断和异常可以通过stvec、sip、sie 和 scause 管理。

在M模式下,软件还可以直接写入SIP寄存器,从而有效地向S模式发送中断。这对于定时器和软件中断特别有用,因为可能需要在M模式和S模式下处理这些中断。

Delegation Registers (mideleg and medeleg)

默认情况下,所有的trap都在M模式下处理。M模式下软件可以通过CSR 有选择地将中断和异常委托给S模式。具体的映射如表 92 和表 93 。

注意,本地中断可以委托给M模式。

注意,本地中断可以委托给M模式。

Supervisor Status Register (sstatus)

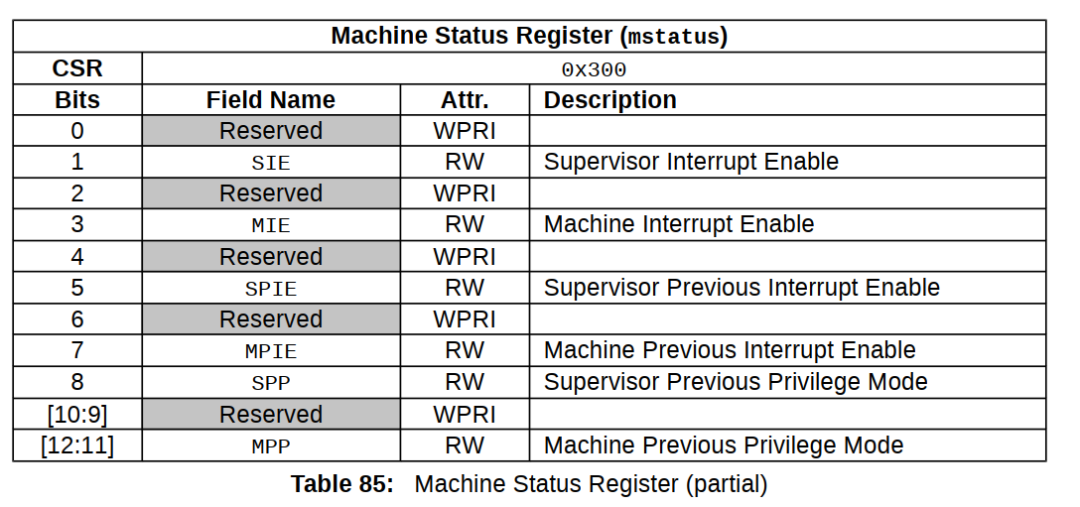

与M模式类似,S模式有一个寄存器,专门用于跟踪 hart 的当前状态,称为 sstatus。sstatus 实际上是 mstatus的受限视图,因为对 sstatus 所做的更改反映在 mstatus 中。

通过在 sstatus 中设置 SIE 位并在 sie 寄存器中启用所需的单个中断来启用中断。

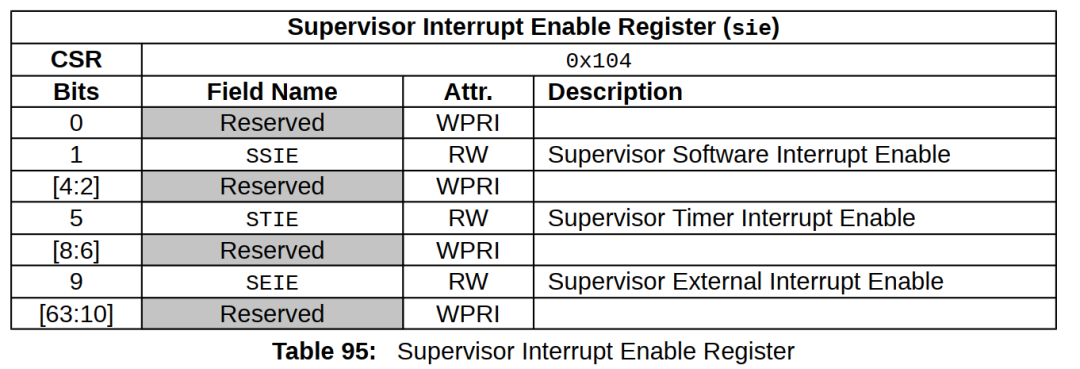

Supervisor Interrupt Enable Register (sie)

通过在 sie 寄存器中设置适当的位来启用管理员中断。

Supervisor Interrupt Pending (sip)

S模式中断挂起 (sip) 寄存器指示当前哪些中断挂起。

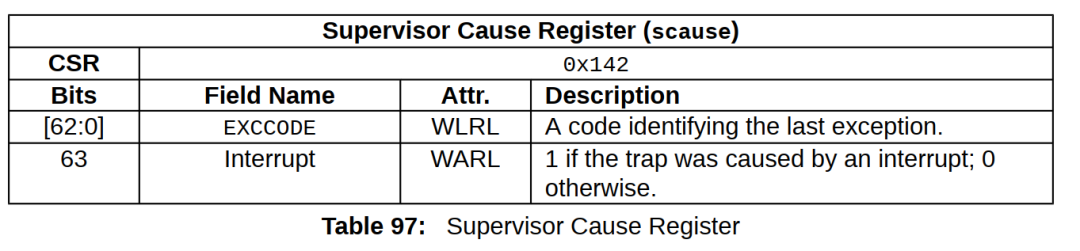

Supervisor Cause Register (scause)

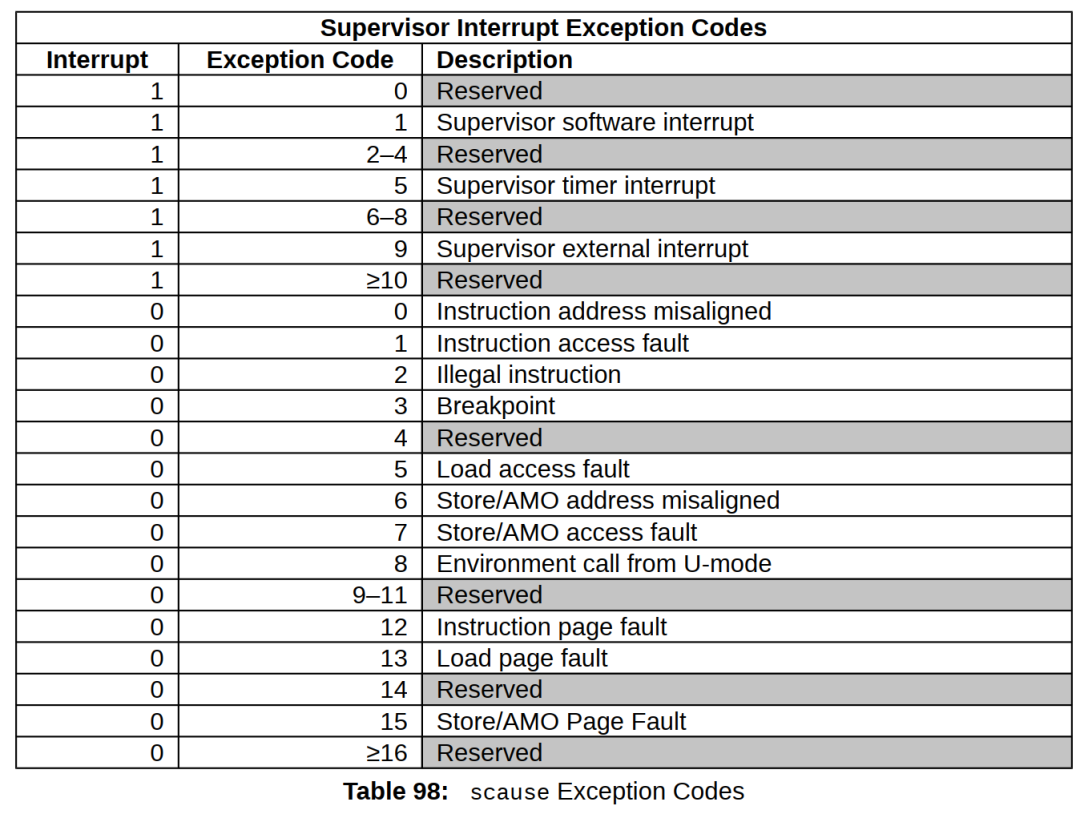

当S模式下捕获陷阱时,将导致陷阱的事件的代码写入 cause。当导致陷阱的事件是中断时,最高有效位 scause 设置为1,最低有效位表示中断号,使用与 sip 中的位置相同的编码。例如,S模式定时器中断导致 cause 被设置为0x8000_0000_0000_0005。

scause 也用于指示同步异常的原因,在这种情况下,scause 的最高有效位设置为 0。有关同步异常代码的列表,请参见表 98。

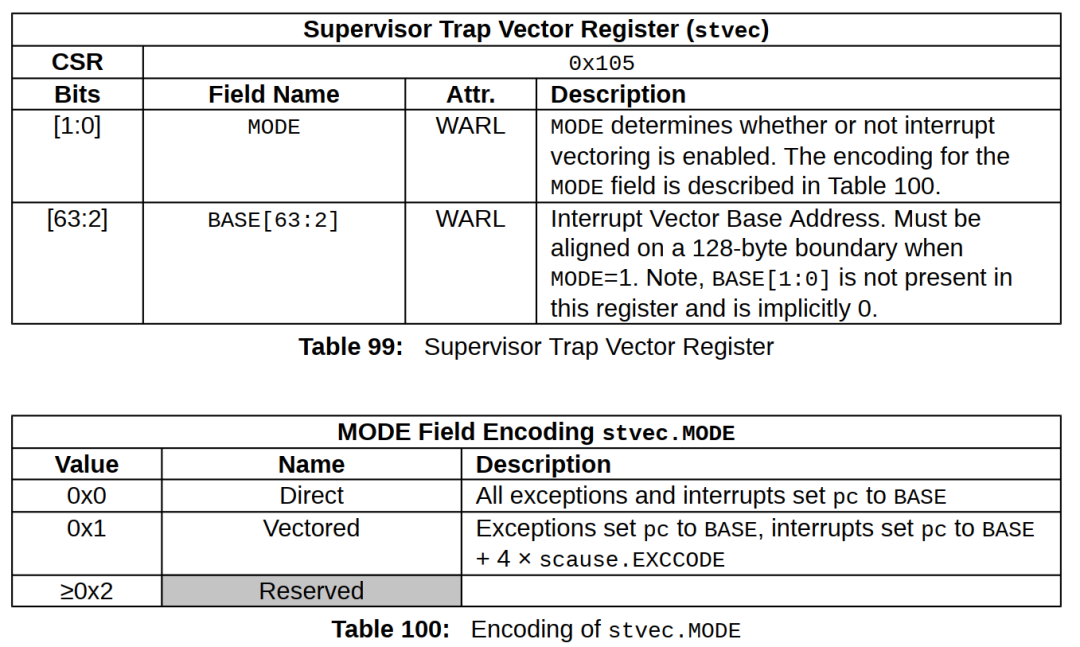

Supervisor Trap Vector (stvec)

默认情况下,所有中断都会捕获到 stvec 寄存器中定义的单个地址。由中断处理程序读取原因并做出相应的反应。RISC‑V 和 U54内核还支持选择性地启用中断向量的能力。当启用向量时,在 sie 中定义的每个中断都会陷入到它自己特定中断处理程序中。

当 stvec 寄存器的 MODE 字段设置为 1 时,向量中断被启用。

如果向量中断被禁用 (stvec.MODE=0),所有中断都会陷入 stvec.BASE 地址。如果启用矢量中断 (stvec.MODE=1),中断pc 设置为 stvec.BASE + 4 × 异常代码 (scause.EXCCODE)。例如,如果发生管理定时器中断,则 pc 设置为 stvec.BASE+ 0x14。通常,陷阱向量表中填充有跳转指令,以将控制转移到特定于中断的陷阱处理程序。

在向量中断模式下,BASE 必须是 128 字节对齐的。

所有主管外部中断(全局中断)都映射到异常代码 9。因此,当启用中断向量时,pc 被设置为任何全局中断的地址 stvec.BASE +0x24。

Delegated Interrupt Handling

接受委派陷阱后,会发生以下情况:

sstatus.SIE 的值被复制到 sstatus.SPIE,然后 sstatus.SIE 被清除,有效地禁用中断。

当前pc被复制到sepc寄存器中,然后pc被设置为stvec的值。在启用矢量中断的情况下,pc 设置为 stvec.BASE + 4 × 异常代码(scause.EXCCODE)。

中断前的特权模式编码在 sstatus.SPP 中

此时,控制权移交给中断处理程序中的软件,中断被禁用。可以通过显式设置 sstatus.SIE 或执行 SRET 指令退出处理程序来重新启用中断。执行SRET 指令时,会发生以下情况:

特权模式设置为 sstatus.SPP 中编码的值

status.SPIE 的值被复制到 status.SIE

pc 设置为 sepc 的值

此时,控制权交给了软件

-

寄存器

+关注

关注

31文章

5619浏览量

130421 -

内核

+关注

关注

4文章

1476浏览量

43090 -

RISC

+关注

关注

6文章

485浏览量

86846 -

模式

+关注

关注

0文章

65浏览量

13839 -

sifive

+关注

关注

0文章

37浏览量

9817

发布评论请先 登录

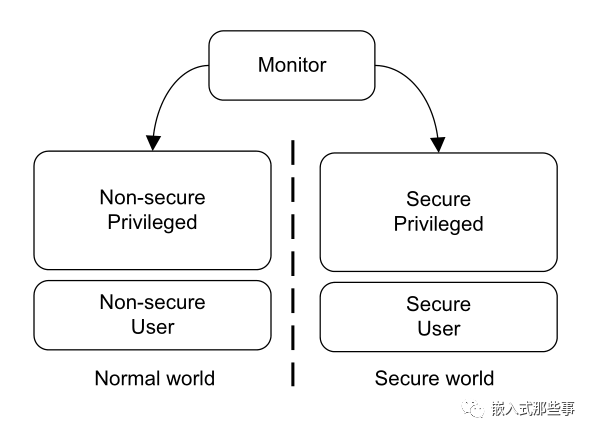

第9章 任务运行在特权级或非特权级模式

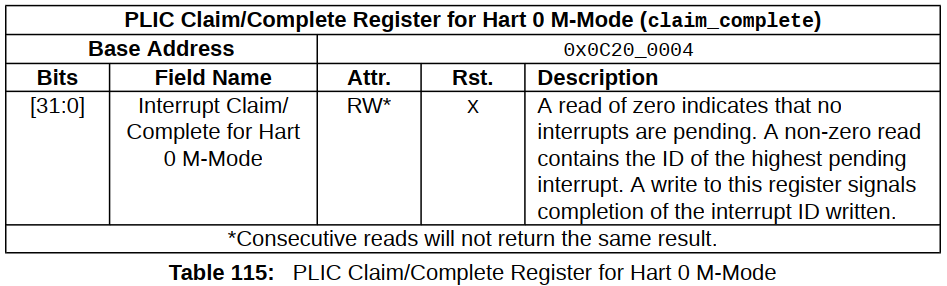

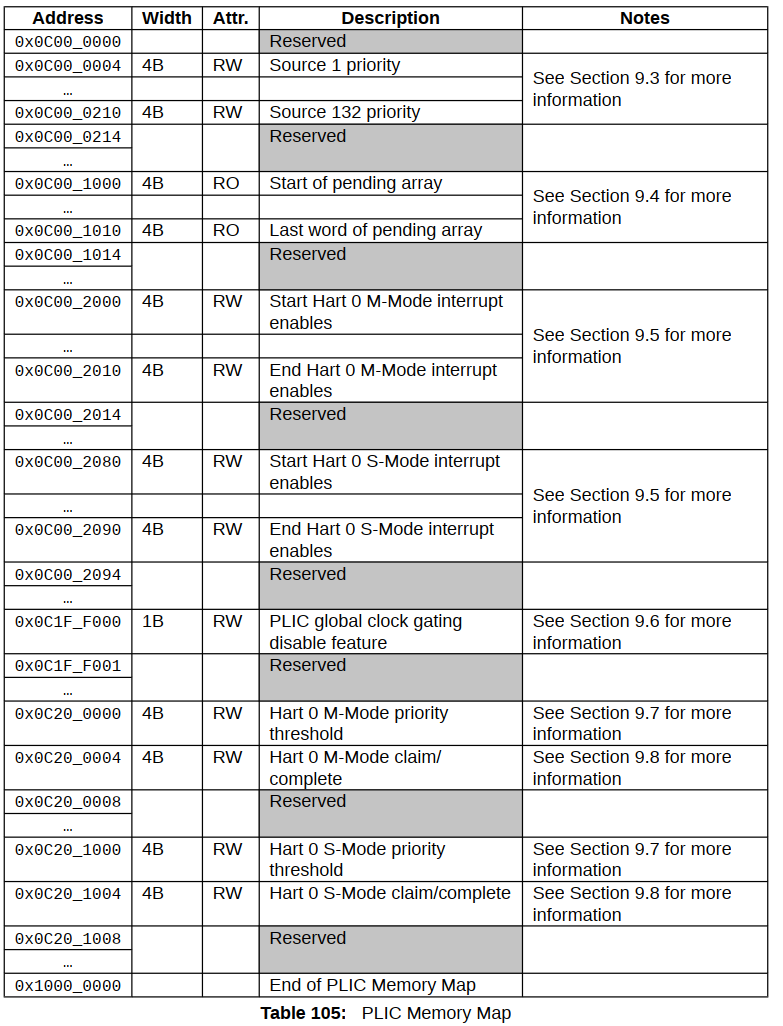

U54内核PLIC中断处理例子

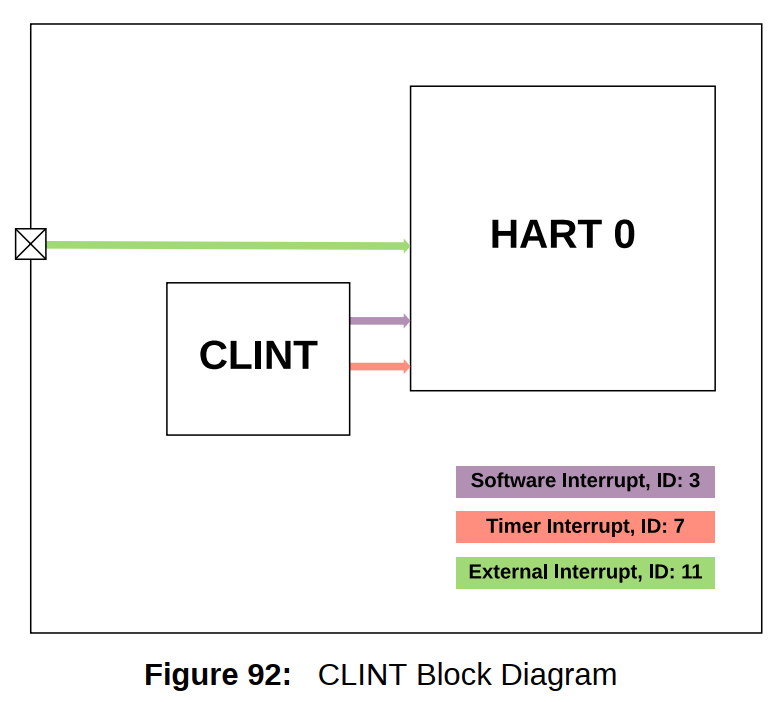

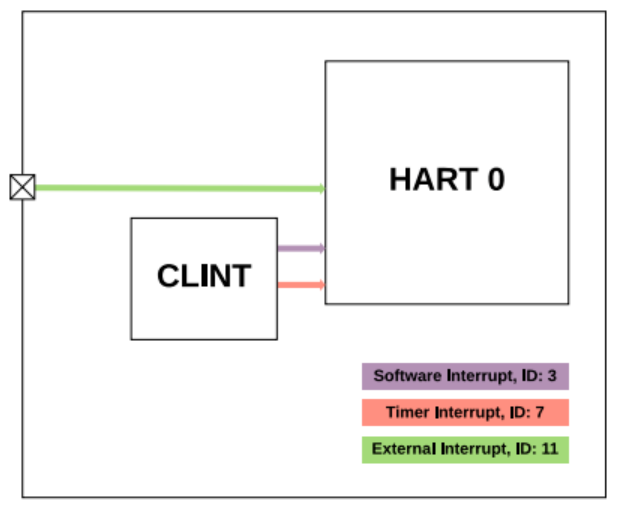

CLINT中断控制器优先级和抢占

U54内核上CLINT的内存映射

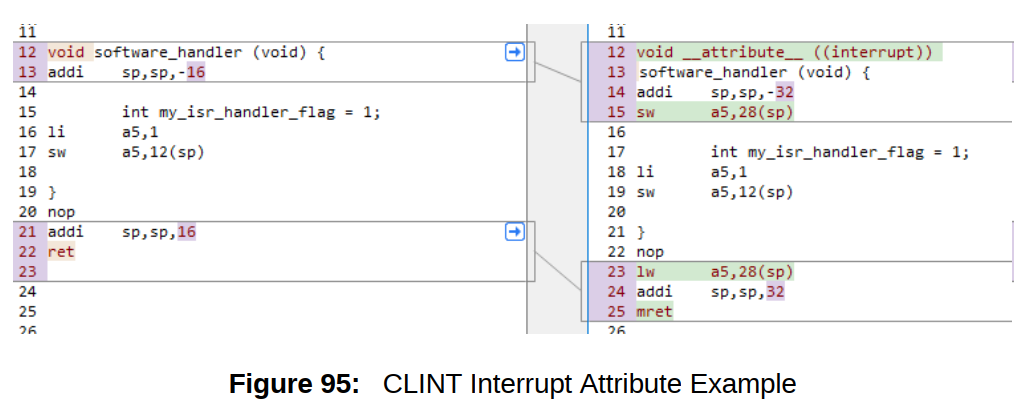

U54内核中断进入和退出

如何在特权模式下用arm汇编指令使能和禁止irq中断?

ARMv7-A处理器模式与特权等级

U54内核特权模式中断介绍

U54内核特权模式中断介绍

评论