电子发烧友网报道(文/周凯扬)要说跟上AI时代的进程,RISC-V相对其他架构来说也一点不慢。从各个初创公司的产品或者路线图也可以看出,AI计算是他们最为重视的一环,甚至重要性要超过通用计算。毕竟这是RISC-V可以后发制人的一大领域,甚至不会有太多架构设计上的历史桎梏。为此,不少厂商也都从AI出发,设计出了定位不一的RISC-V产品。

高性能AI计算

Esperanto作为为数不多的几家冲击高性能AI计算的公司,如今也开始察觉到了AI市场的风向变动,于是决定将重心从过去的推荐加速改为大语言模型和HPC。Esperanto走进大众视野的方式相当特别,他们的第一款产品就是千核RISC-V芯片ET-SOC-1。

ET-SOC-1基于台积电7nm工艺打造,集成了1088个64位ET-Minion RISC-V核心和4个ET-Maxion核心,提供了超高的单线程性能。虽说ET-SOC-1对ML进行了优化,是一个理想的推理芯片选择,但Esperanto为其打造的软件栈主要还是以推荐场景打造。直到他们近期推出了新的AI软件开发工具包,并专门针对LLM进行了优化,并展示了运行300亿参数的OPT模型。

据Esperanto表示,目前他们的生成式AI应用已经可以运行最新的LLM和图片生成模型,比如LLaMA2、Vicuma和Stable Diffusion等等。不过在千变万化的AI市场下,单个模型往往难以维持长时间的热度,所以Esperanto的计划是持续跟进最流行的开源模型。

IP厂商也不例外,除了SiFive、平头哥、Tenstorrent等已经推出高性能AI IP或对现有产品线进行AI升级的公司外,Semidynamics也发布了最新完全可定制的矢量单元,用于配合其Atrevido CPU核心。该矢量单元有多个矢量内核构成,每个内核都有算数单元,可以执行加减、乘加等数字与逻辑运算。

这个矢量单元的最大特色在于全定制性,与其他厂商只有部分配置选项不同,为了应对未来各种AI模型的精度要求,Semidynamics的矢量单元在定制化后,可以支持FP64、FP32、FP16、BF16、INT64、INT32、INT16或INT8的数据类型。

尽管ASIC、GPU和FPGA常被视为最合适进行AI计算的三大硬件,但在如今的市场环境下,无论是服务器还是消费终端,CPU也都需要一些可观的AI计算特性。所以开源社区推出了LLaMA.cpp这一模型,该模型是基于Meta的LLaMA模型打造而成,无需PyTorch等库的外部依赖,仅靠C/C++编译即可生成执行文件,且无需GPU,只靠CPU就可以运行。

旷视科技参考并借鉴了LLaMA.cpp项目,推出了InferLLM这一轻量级的LLM模型推理管家,且除了常见的Arm、x86和CUDA外,他们也针对RISCV-Vector做了专门的优化,目前已经可以部署在群芯闪耀科技发布的Milk-V Pioneer RISC-V主板上,而该主板用到的64位CPU正是算能科技的算丰SG2042。

算丰SG2042采用了单芯片64个RISC-V内核的设计,支持双路CPU互联、4通道DDR4和32通道PCIe 4.0,典型功耗为120W,可以说是典型的服务器芯片设计。但很明显,即便是高性能CPU,在一些非重型AI负载下,也能有可观的表现。

低功耗的边缘端

尽管云端的生成式AI已经变得越来越普及,企业在花了大成本购置硬件资源后也能在本地运行更多的AI计算负载降低效率提高安全性。但对于消费者而言,似乎真正部署在端侧的生成式AI才更加值得关注,在实用性上也刚强一些,而且不只是手机这种使用高端芯片的产品,不少IoT产品也在规划着如何接入生成式AI,因此大算力的边缘AI芯片就成了首选。

云天励飞作为国内首批闯入AI赛道的厂商,此前一直在主攻AI算法领域,但单靠算法的泛化能力相对较弱,于是云天励飞也就开始加入芯片设计赛道,比如2018年推出的DeepEye 1000等。

而在今年举办的第三届滴水湖中国RISC-V论坛上,云天励飞展示了去年成功流片,如今已经接近量产的边缘AP级SoC Deep Edge10V。从芯片结构上看,Edge10V采用了Chiplet设计,满足国产Chiplet UCIE标准。CPU部分采用了1.2GHz的双核C920,还集成了一个500MHz的NNP400T NPU,算力高达12TOPS@INT8。在视频处理能力上,Edge10V也配备了支持H265/H264视频编解码的多媒体子系统。

另外值得一提的是,Edge10V仅仅是Edge10系列中的一环,由于Chiplet设计支持多die扩展,所以也可以在Edge10Max这一产品上实现高达64Tops的算力。云天励飞芯片BD总监张福林表示,Edge10V主要应用于边缘计算,而Edge10Max则应用于边缘CV大模型,比如Pytorch、Caffe、Tensorflow等框架下的模型。从应用上来看,Edge10V的主要应用场景还是云天励飞擅长的机器视觉领域,比如机器人、智能安防之类的边缘端。

本届滴水湖论坛上,普林芯驰也展示了他们的智能离线语音交互MCU SPV20系列芯片。该系列的特色在于,除了基于SiFive E21RISC-V核心打造的CPU外,还有基于CEVA TL420核心的DSP与集成普林芯驰自有算法的NPU。该NPU支持CNN、DS-CNN等深度压缩语音识别模型,可用于家电的智能语音控制。

嘉楠科技的第二代AI推理芯片,勘智K510,同样是针对边缘侧AI开发的产品。这一芯片采用了双核RISC-V 64位CPU,主频最高达到800MHz。勘智K510支持INT8和BF16双数据类型,且具备2.5TFLOPS的算力,还支持Tensorflow、Pytorch和ONNX等多种框架的算子库。

用生成式AI设计RISC-V芯片

随着生成式AI在代码生成上日益精进的表现,如今利用生成式AI来设计芯片也成了可能。近日,开源硬件平台Efabless就举办了一届生成式开源芯片设计挑战赛,其中清华RIOS Lab团队的RISC-V芯片,CyberRio获得了亚军。

据其Github页面所示,该芯片的大部分Verilog代码都是使用GPT-4生成的,从而基于一个经典的5级流水线设计出了CyberRio。CyberRio也在Skywater提供的130nm的工艺平台上得到了流片验证,这也意味着全球第一个由LLM完成主要涉及的CPU被成功制造出来。

不过开放团队也表示,GPT-4对硬件语言的理解并不算完整,无论是对设计语言本身的理解,还是对握手或并行处理等设计概念。这很可能是GPT-4训练过程本身的缺陷,不过开发团队也提出了Langchain之类的替代方案或许可以解决GPT-4信息缺失造成的问题。

写在最后

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

机器人

+关注

关注

213文章

30579浏览量

219463 -

控制

+关注

关注

5文章

1031浏览量

125067 -

AI

+关注

关注

89文章

38085浏览量

296381

发布评论请先 登录

相关推荐

热点推荐

探索RISC-V在机器人领域的潜力

的硬件配置给人留下了深刻的第一印象:

• 核心处理器: 搭载了进迭时空的K1系列高性能RISC-V处理器,具备强大的通用计算能力和AI加速特性。

• 内存与存储: 板载LPDDR4内存和eMMC

发表于 12-03 14:40

进迭播客 | Vol.3对话孙彦邦:用胡子赌一个未来,RISC-V是AI时代的“终极答案”

进迭播客「RISC-V圆桌白话录」「RISC-V圆桌白话录」第三期播客上线!本期播客我们邀请到对话进迭时空联合创始人、总裁孙彦邦,一起深入探讨RISC-V如何成为

为什么RISC-V是嵌入式应用的最佳选择

最近RISC-V基金会在社交媒体上发文,文章说物联网和嵌入式系统正在迅速发展,需要更高的计算性能、更低的功耗和人工智能。RISC-V是为未来而建的,包括超高效的MCU到高性能应用处理器,RIS

深度数智亮相2025年RISC-V北美峰会,携手共创开放式AI计算未来

2025年RISC-V北美峰会堪称全球开放硬件社区发展的又一重要里程碑,RISC-V迈出国际标准化第一步——获ISO/IECJTC1授予PAS提交者资格。对深度数智而言,这次盛会正是我

大象机器人携手进迭时空推出 RISC-V 全栈开源六轴机械臂产品

、lightrack)等模型。仓库将持续更新支持最前沿的模型应用,满足各种复杂 AI任务。

AI智慧零售套件

通过CPU融合AI的创新设计,

发表于 04-25 17:59

FPGA与RISC-V浅谈

全球半导体产业竞争格局正在经历深刻变革,物联网、边缘计算等新兴技术的蓬勃发展,让RISC-V凭借其开源、精简以及模块化的灵活优势,日益成为业界焦点,也为全球半导体产业注入新的活力与挑战

发表于 04-11 13:53

•543次阅读

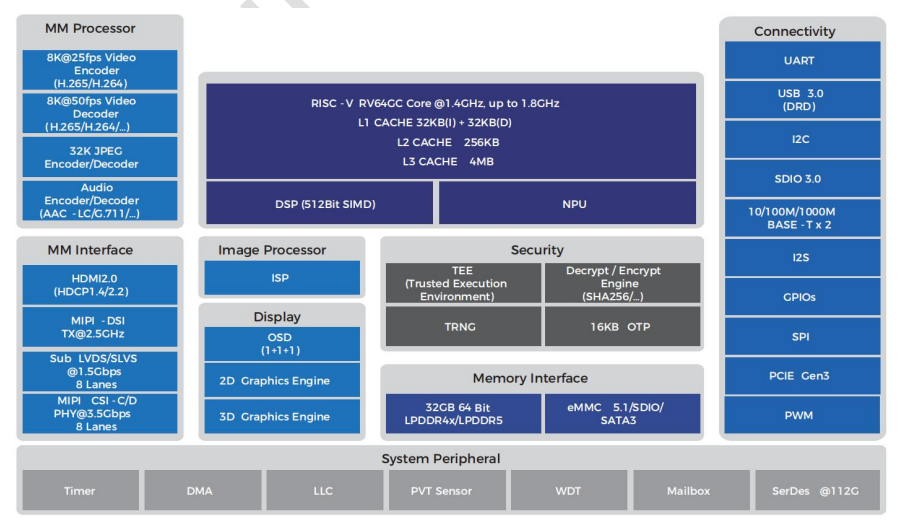

AI SoC# 奕斯伟EIC7700 全球首款基于RISC-V架构的边缘计算SoC芯片

EIC7700X是一款性能优异的边缘计算SoC芯片,搭载64位RISC-V处理器和自研神经网络计算单元,支持全栈浮点计算和生成式大语言模型。

首款RISC-V架构服务器,助力行业精准适配AI场景

RISC-V融合服务器RS-SRM120为2U双路异构服务器产品,搭载双RISC-V指令集64核处理器SG2042,通过高效的双芯互联架构,提供强大的智算能力。支持CV模型、LLM等多种深度学习

关于RISC-V芯片的应用学习总结

、智能网关等物联网设备。此外,RISC-V的模块化设计使得开发者可以根据具体需求灵活剪裁指令集,进一步优化功耗和性能。

在嵌入式系统方面,RISC-V芯片同样表现出色。嵌入

发表于 01-29 08:38

新的一年 RISC-V前景如何呢?

1 月 7 日消息,RISC-V 领军企业 SiFive 成立中国分公司,中文名称定为“芯伍科技”。

1 月 14 日消息,专注传统与 AI 业务,Imagination 放弃 RISC-V CPU 开发。

新的

发表于 01-24 16:19

RISC-V MCU技术

的研究团队弄出来的,目的就是想搞个新的、开放的指令集架构,能跟上现代计算的需要。到了2015年,专门成立了个RISC-V基金会,让这个架构更标准,也更好地推广开了。这几年啊,这个RISC-V

发表于 01-19 11:50

进迭时空亮相RISC-V产业发展大会:新AI CPU引领大模型时代

12月28日,以“发挥标准优势,繁荣产业发展”为主题的RISC-V产业发展大会在北京亦庄经开区通明湖会展中心举行。作为基于新一代RISC-V架构的计算生态企业,进迭时空受邀出席此次大会。进迭时空

RISC-V架构及MRS开发环境回顾

MounRiver Studio(MRS)是一款针对RISC-V/ARM双核MCU的嵌入式集成开发环境,由MounRiver团队基于GNU Eclipse深度定制而成,提供了包括定制版GCC、宏

发表于 12-16 23:08

如何使用 RISC-V 进行嵌入式开发

RISC-V是一种开源的指令集架构(ISA),它允许任何人设计、制造和销售基于RISC-V的处理器,这为嵌入式开发提供了极大的灵活性和创新空间。以下是使用

大模型与生成式AI,RISC-V也想分一杯羹

大模型与生成式AI,RISC-V也想分一杯羹

评论