导读:天域半导体提出的碳化硅外延片去除外延再生衬底方案,能够加工更高效、精确更高的去除外延层,保留衬底厚度,并提高CMP的加工效率和质量,从而实现不合格外延片再生衬底的重利用。

碳化硅同质外延生长后,如果外延不合格则需要将外延去除,然后进行化学机械抛光(CMP),最后恢复至与原衬底相当的品质。

现有的去除不合格外延的方式是:先进行单面研磨,再进行单面初抛光,最后再进行CMP处理。单面研磨是将外延片固定在模具上,施加一定的加压,在金属盘上用磨料对外延片进行研磨切削,单面研磨的精度低,并且精度难以控制,表面质量较差,容易引入深划伤。

此外,研磨技术的缺点还有统一性不高,多片加工时对外延片的厚度的组合比较苛刻,并且加工效率较低。如果将研磨后的外延片再进行CMP处理,则需要较长的时间才能去除掉损伤层。并且由于衬底的厚度不同,外延的厚度也不同,因此每一片外延片的减薄要求也不同,整体加工效率较低。

因此,为了尽可能的降低损伤层厚度、保留衬底厚度,并提高CMP的加工效率和质量,进而实现不合格外延片再生衬底的重利用,天域半导体在2022年6月1日申请了一项名为“碳化硅外延片去除外延再生衬底的方法”的发明专利(申请号:202210617214.8),申请人为东莞市天域半导体科技有限公司。

根据该专利目前公开的相关资料,让我们一起来看看这项技术方案吧。

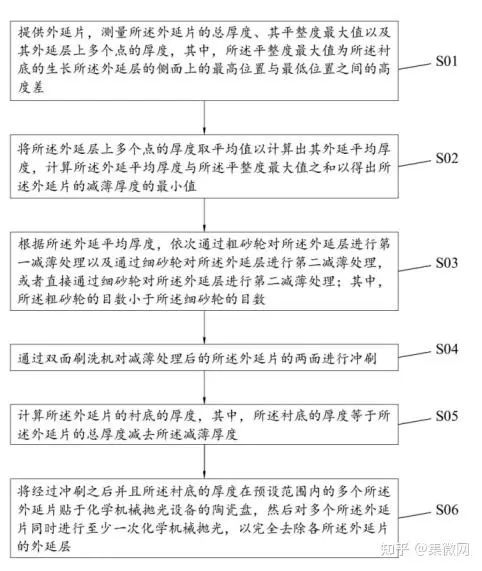

如上图,为该专利中提出的碳化硅外延片去除外延再生衬底的方法的流程图。首先,测量外延片的总厚度、其平整度最大值以及其外延层上多个点的厚度,平整度最大值为衬底的生长外延层的侧面上的最高位置与最低位置之间的高度差。

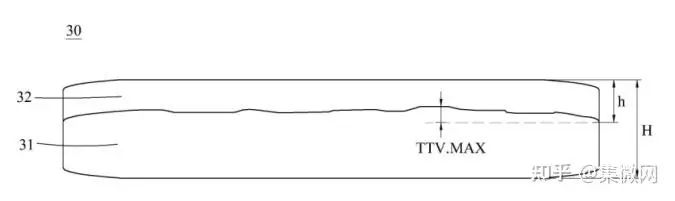

如上图所示,外延片30经过外延生长之后,在其衬底31的一侧面上形成一外延层32。该方案中使用表面厚度测量仪来对外延层上的多个点进行厚度测量,例如对外延层上的个点进行测量,得到厚度值hi(i=1,2,...n),n为大于等于1的正整数。然后,使用表面平整度测量仪来测量外延片的总厚度H以及其平整度最大值TTV.MAX,平整度最大值是指衬底的生长外延层的侧面上的最高位置与最低位置之间的高度差。

其次,将外延层上多个点的厚度取平均值以计算出其外延平均厚度,计算外延平均厚度与平整度最大值之和以得出外延片的减薄厚度。如上图所示,将测量得到的厚度值hi(i=1,2,...n)取平均值,从而计算出其外延片的外延平均厚度。由于去除外延层是需要将衬底上的所有外延层都去除干净,因此,该方案中的减薄厚度大于等于外延平均厚度与平整度最大值之和。

接着,根据外延平均厚度,依次通过粗砂轮对外延层进行第一减薄处理以及通过细砂轮对外延层进行第二减薄处理,或者通过细砂轮对外延层进行第二减薄处理,再通过双面刷洗机对减薄处理后的外延片的两面进行冲刷。

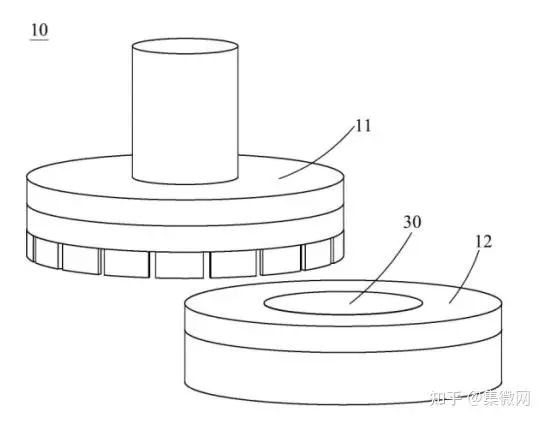

如上图所示,为该方案中所使用的双轴减薄机的局部结构示意图。减薄技术是现有的研磨技术的升级,减薄技术具体是使用双轴减薄机10,将外延片固定在双轴减薄机的多孔陶瓷吸附台12上,采用金刚石粉和树脂等加工而成的砂轮11在高速旋转下对外延片的表面进行快速切削,效率高并且精度高。

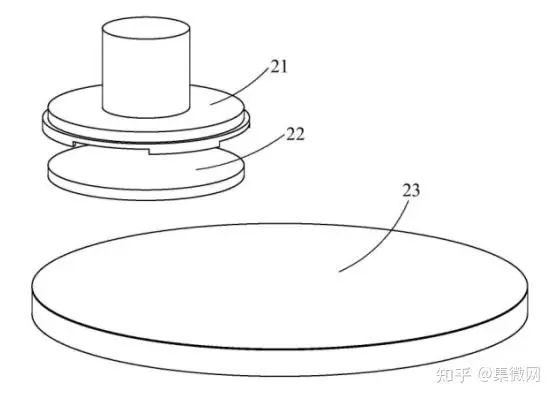

最后,计算外延片的衬底的厚度,衬底的厚度等于外延片的总厚度减去减薄厚度。并将经过冲刷之后并且衬底的厚度在预设范围内的多个外延片贴于化学机械抛光设备的陶瓷盘,然后对这些外延片同时进行至少一次化学机械抛光,以完全去除各外延片的外延层。

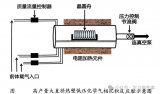

如上图,为该方案中使用的化学机械抛光设备的局部结构示意图。CMP技术是外延片抛光中的最后一道工艺,具体是将外延片贴在化学机械抛光设备的陶瓷盘22上,然后在气缸21的加压下使外延片与抛光液和抛光垫23相互作用,可以将外延片表面的损伤层去除,从而降低表面粗糙度。只有经过良好的CMP加工才可以将外延片恢复至与原衬底相当的品质,利用时才能生长较好的外延。

以上就是天域半导体提出的碳化硅外延片去除外延再生衬底方案,该方案能够加工更高效、精确更高的去除外延层,保留衬底厚度,并提高CMP的加工效率和质量,从而实现不合格外延片再生衬底的重利用。

-

半导体

+关注

关注

336文章

30043浏览量

258965 -

碳化硅

+关注

关注

25文章

3342浏览量

51764 -

外延片

+关注

关注

0文章

40浏览量

9995

原文标题:不合格的碳化硅外延片如何再生重利用?这家企业告诉你~

文章出处:【微信号:DT-Semiconductor,微信公众号:DT半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

探索碳化硅如何改变能源系统

电能质量监测装置校准不合格时,如何维修?

[新启航]碳化硅 TTV 厚度测量技术的未来发展趋势与创新方向

![[新启航]<b class='flag-5'>碳化硅</b> TTV 厚度测量技术的未来发展趋势与创新方向](https://file1.elecfans.com/web3/M00/20/D6/wKgZPGhd-raAI0RYAACIgEePWXY565.png)

【新启航】碳化硅外延片 TTV 厚度与生长工艺参数的关联性研究

从衬底到外延:碳化硅材料的层级跃迁与功能分化

碳化硅功率器件有哪些特点

去除碳化硅外延片揭膜后脏污的清洗方法

碳化硅外延晶片硅面贴膜后的清洗方法

碳化硅薄膜沉积技术介绍

钟罩式热壁碳化硅高温外延片生长装置

天域半导体IPO:国内碳化硅外延片行业第一,2024年上半年陷入增收不增利困局

什么是MOSFET栅极氧化层?如何测试SiC碳化硅MOSFET的栅氧可靠性?

高温大面积碳化硅外延生长装置及处理方法

8英寸单片高温碳化硅外延生长室结构

不合格的碳化硅外延片如何再生重利用?

不合格的碳化硅外延片如何再生重利用?

评论