针对用户的使用手册经常归纳出一些事先选好的操作方式。对于常用的初始化、正常处理、中断处理等给出了输入序列建议。

使用手册如果涉及太多细节或者给用户太多的选择会使他们手足无措。使用手册中的操作方式一般也都是大部分生态用户实践证明了的方式,芯片的操作不会有太大的学习成本。这就是生态的力量。

对于一颗芯片,绝大多数的用户不会越过芯片最基本的使用手册,即使芯片可能会支持那些复杂的操作。

一个芯片必须确保这些常用的功能正确并且使用方便,这样用户才会花钱。从验证的角度来看,验证这样的功能非常重要,甚至可以说优先级最高。

对于User guide验证法,我们会像一个谨慎的用户,遵循用户手册的建议,从不偏离其引导。

User guide验证法要求验证人员通过阅读用户手册并严格遵照手册的建议执行操作。如果手册描述了某个特性以及如何使用该特性时,验证人员要特意留心那些指令。目的是尽量忠实地执行用户手册中描述的每个场景。这个验证法不仅可以验证芯片确实实现了手册所描述的各种特性,同时也验证了用户手册的准确性。

User guide验证法变种

User guide验证法还会有一些变种:

专家验证法要求验证人员遵循第三方(可能是一些潜在客户或者在该领域有一些经验的技术人员)的建议来验证,其中某些建议可能非常刁钻,但都是很有重要的验证参考。

竞争对手验证法,这种方法竞争对手的使用手册自己的产品进行验证,尤其是竞争对手是市场领先者,而自己产品在其后紧追的情况。在这种情况下,那些从竞争对手产品迁移到我们产品的用户可能更习惯于按照从前的使用方式来使用我们的芯片,因此,验证人员也应该像许多(希望真的是很多)转投的用户一样,用他们过去的使用方式来探索和验证芯片,这种验证最好应该由验证人员进行,而不是让用户去发现芯片是否满足他们的需求。

User guide验证法(包括其各个变种验证法)用于验证芯片是否提供了其所宣传的特性。它是一种直观、易懂的验证,如果芯片特性与用户手册所描述的不一致,就应该上报这些bug(包括性能/安全性/易用性/维护性/测试性等等)。结果也许只是需要更新用户手册,但是不管怎样,这都是在服务于用户。所以,文档问题最好也要提出来~

User guide验证法强迫验证人员按用户的使用方式把芯片特性串起来验证,同时还要求这些特性按用户的真实使用方式相互交互。所以这时发现的任何bug都很可能是极其重要的问题。

审核编辑:刘清

-

芯片制造

+关注

关注

11文章

734浏览量

30527

原文标题:验证方法-User guide验证法

文章出处:【微信号:数字芯片实验室,微信公众号:数字芯片实验室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于瑞芯微平台的 eMMC 颗粒验证全流程指南

RDMA设计38:寄存器功能验证与分析

RDMA设计35:基于 SV 的验证平台

SUREWARE ULTRA RUGGED HARDWARE之BOARD - TO - BOARD GUIDE POST STANDOFF介绍

车载OBC电源模块车规电容选型流程与实战方法

【工程师必看】DDR缺货涨价?5步教你验证新内存颗粒“抗不抗造”!

代购系统 API 介绍

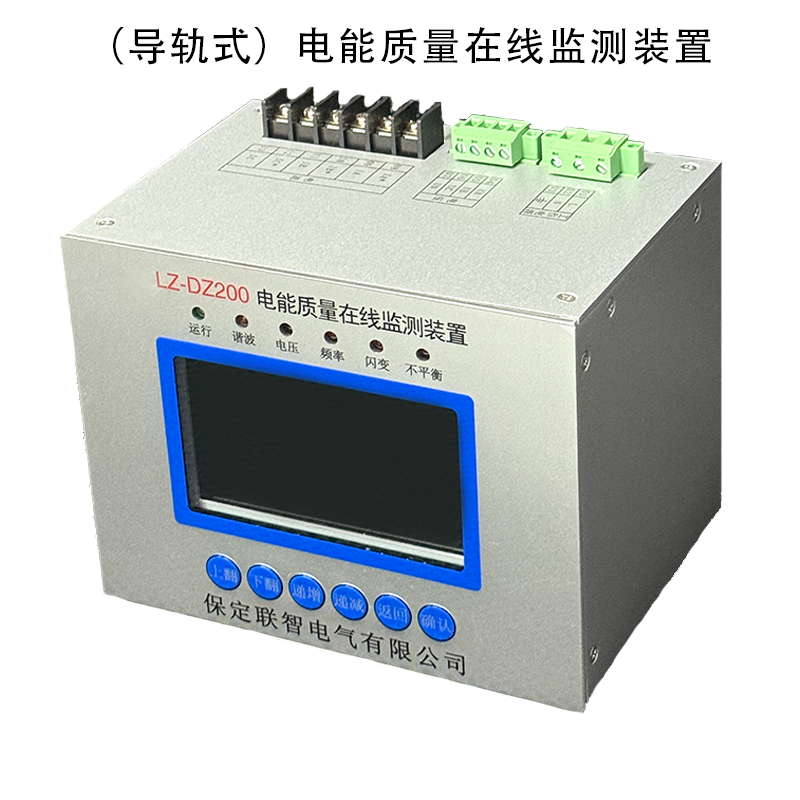

电能质量在线监测装置硬件故障检测的一般流程是什么?

如何验证硬件冗余设计的有效性?

NVMe高速传输之摆脱XDMA设计24: UVM 验证包设计

请问 sotAP(CYW55512)模式是否支持“b only”和“b/g”?

CY4500 ez-pd 协议分析仪总是断开连接怎么解决?

硬件辅助验证(HAV) 对软件验证的价值

FPGA EDA软件的位流验证

User guide验证法介绍

User guide验证法介绍

评论