板子lay的好,ESD没烦恼。提高ESD静电防护,PCB设计需要做好以下几点:

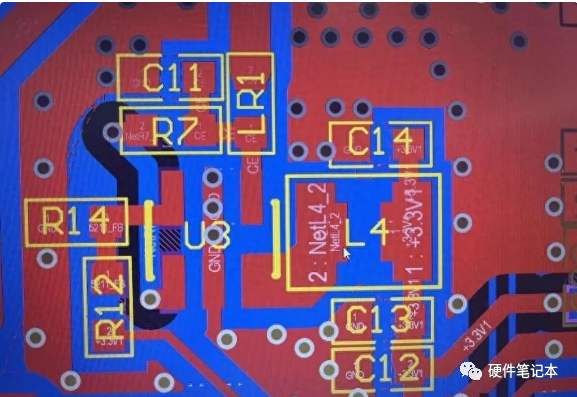

对于电源布局的整改,如图1所示:

图1

1、DCDC电源布局,在电压输出端经过电感,旁路电容和储能电容的布局如上图,旁路电容C14、C13尽量靠近电感输出,取电压最好是经过电容C12后取电。目的是电路可更好滤波,减少干扰。

2、所有通过电源线、信号线上的高频旁路电容都尽量就近接地,以减小进入电路系统的ESD大电流,起到更好的吸收干扰的作用。

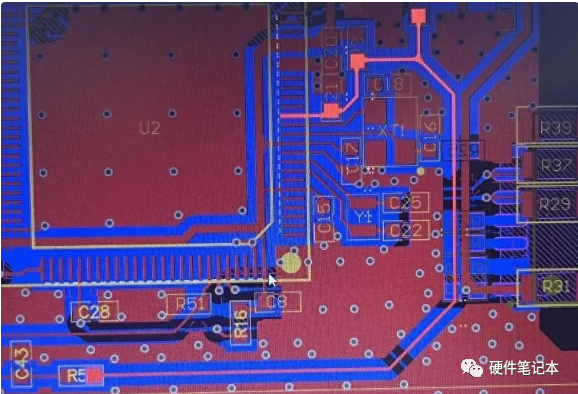

3、复位线、恢复出厂信号线要尽可能短。因为越长的走线就越难承受ESD能量,故元器件的布局尽可能凑近以减短走线长度。若实在无法避免,线的两边尽量有地包裹,如图2所示。(感谢关注微信公众号:硬件笔记本)目的是减少其他信号干扰,避免受到干扰使芯片无故重启。同时也可在电路上加电容或电阻,可增大内阻,防止过大的干扰信号。

图2

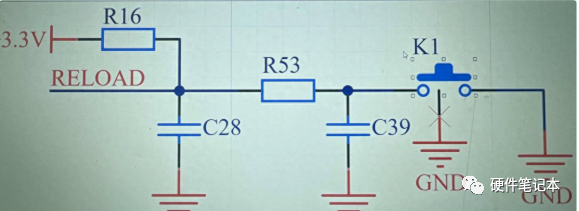

4、开关复位线布局也是同样的原理,在电路上可加上一个π型滤波电路,如下图图3所示,可更好的消除外界干扰,防止芯片重置。

图3

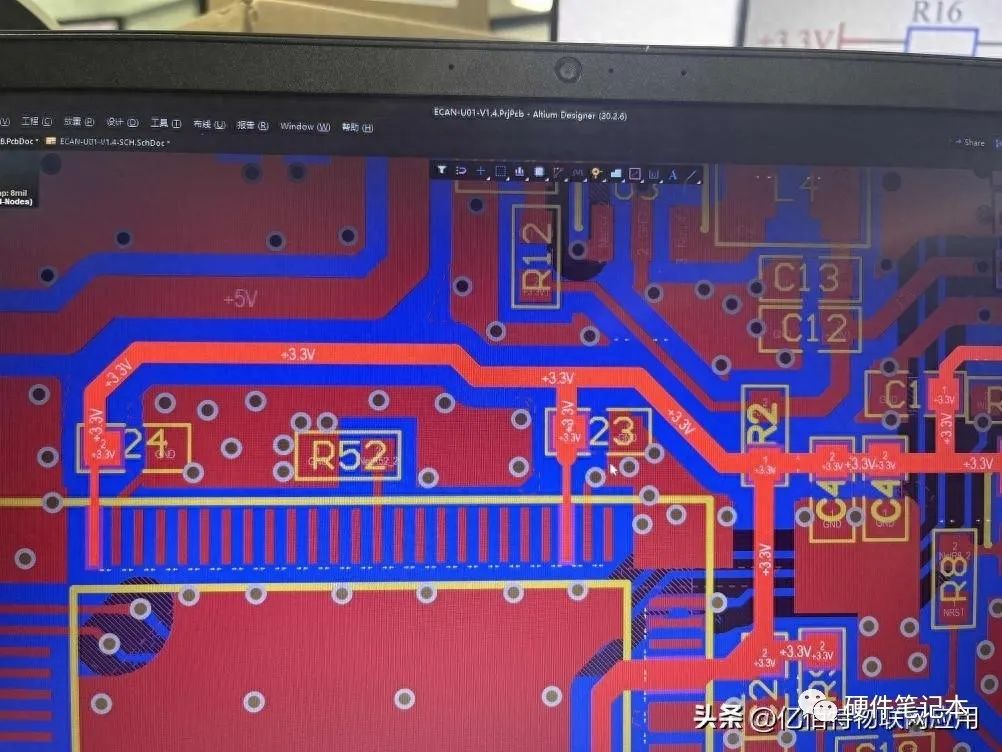

5、给芯片供电,电源走线尽量是先通过电容再流向芯片,对芯片起到保护作用。如图4所示。

图4

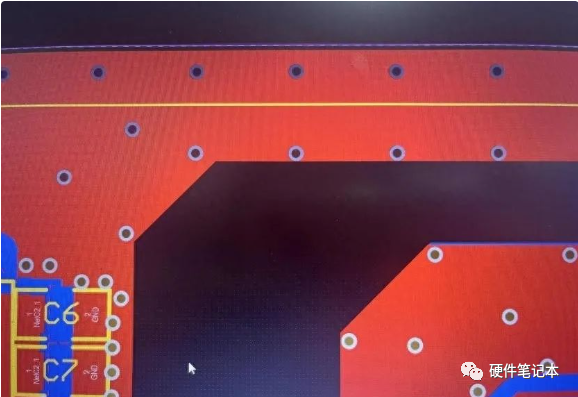

6、地线铺铜尽量避免直角。尽量使用拐角大于90°,直角尖会产生干扰,会导致放电路径不一致。如图5所示。

图5

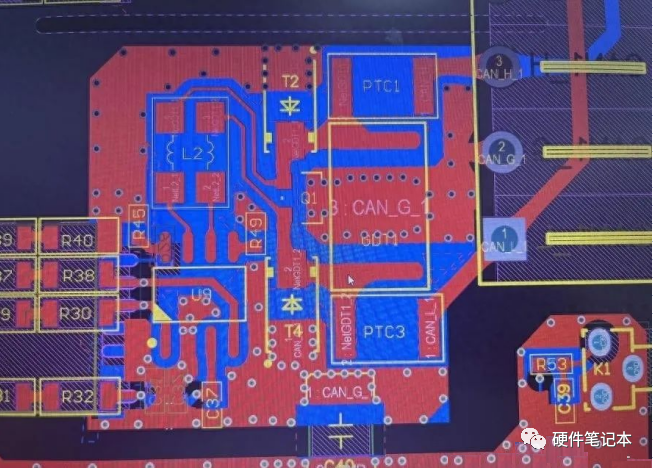

7、通讯线先经过保护器件,再经过防雷管放电,防雷管就近接地,再经过TVS放电。线尽量短,回路尽可能小,可快速消除干扰信号。(感谢关注微信公众号:硬件笔记本)在地线上加上Y电容,可快速放电,消除静电。

图6

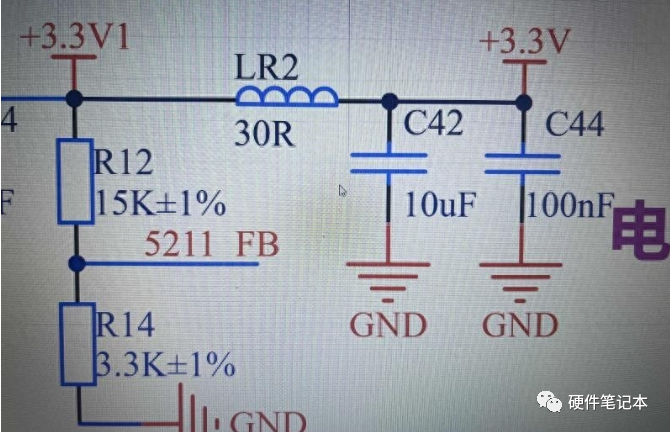

8、MCU和其他芯片可以分开取电,避免相互干扰,可在电路上加LC滤波电路。电路如图所示:

图7

9、也可使用多层板。多层板可大大改善系统抵抗ESD放电的能力。将第一层接地平面尽可能靠近信号走线层,可使用ESD瞬态放电在到达走线时能很快抵消。

10、加隔离。电气隔离也是抑制静电放电冲击的一种方法。在PCB上加隔离芯片或者光耦、变压器等,以及结合截止隔离和屏蔽可以很好抑制静电放电冲击。

总的来说,关于防止ESD静电干扰的设计,电源平面、接地平面和信号线的布局是PCB ESD防护设计的重要措施之一。

审核编辑:汤梓红

-

ESD

+关注

关注

50文章

2428浏览量

180458 -

pcb

+关注

关注

4418文章

23979浏览量

426396 -

DCDC

+关注

关注

30文章

941浏览量

75889 -

静电防护

+关注

关注

11文章

235浏览量

48673

原文标题:板子lay的好,ESD没烦恼

文章出处:【微信号:gh_a6560e9c41d7,微信公众号:硬件笔记本】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何提高ESD静电防护 PCB ESD防护设计的重要措施

如何提高ESD静电防护 PCB ESD防护设计的重要措施

评论