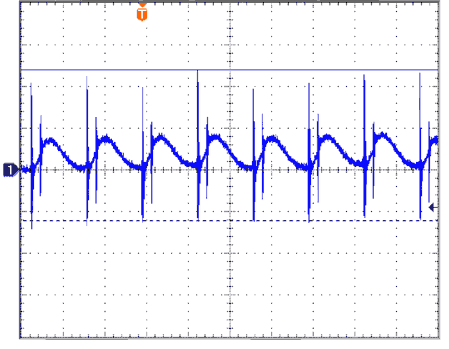

- 它们在输出信号上显示为噪声(包括时序噪声和信号电平噪声),可能导致逻辑电平的误读

- 它们产生的辐射EMI可以从电路板上测量,通常是从边缘测量

|

元素 |

对电源完整性的影响 |

|

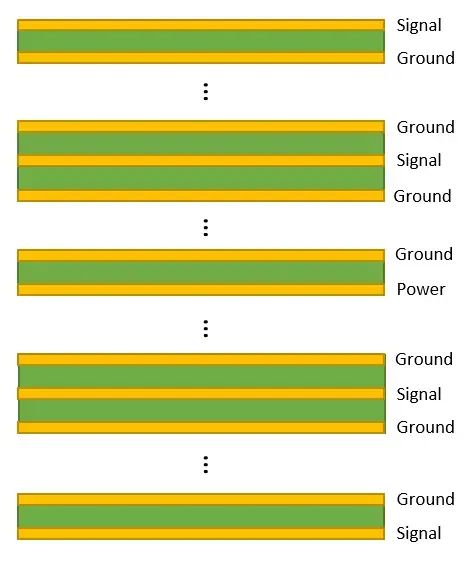

电源和接地层对 |

|

|

离散电容器 |

|

|

电容器封装和过孔电感 |

|

|

嵌入式电容 |

|

|

封装寄生效应 |

|

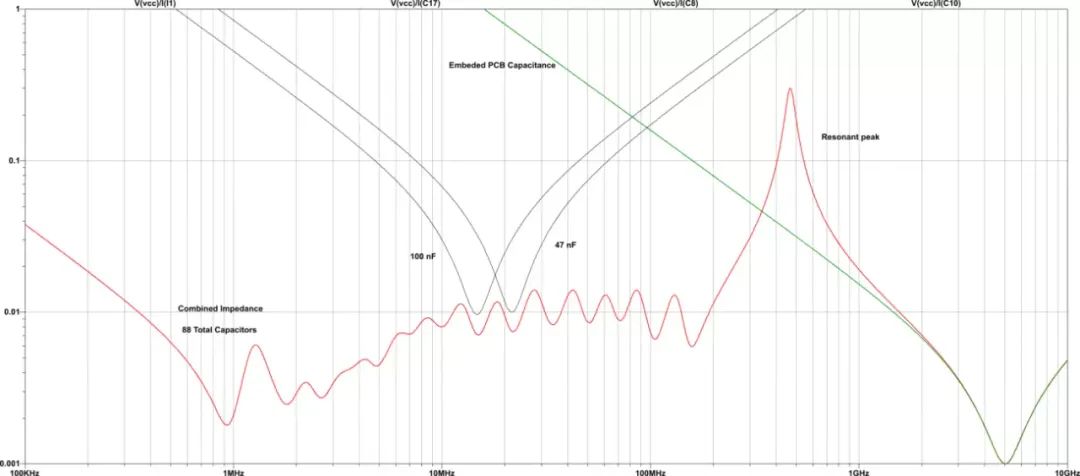

总的来说,这些元素将决定PDN的阻抗频谱。PDN的各种贡献因素如下图所示,这些贡献大致按频率范围划定。此处显示的阻抗谱由大量电容器构成,这是以快速边沿速率运行的、具有高I/O计数的数字处理器的典型特征。

PDN拓扑

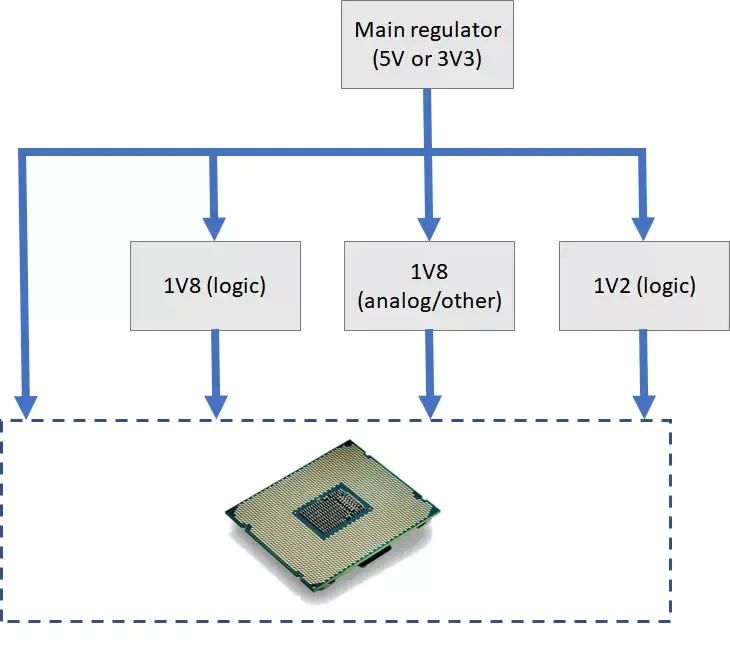

所有为高级处理器供电的PDN都是多端口网络。它们需要多重稳定电压,从高值到低逻辑电平。在高引脚数处理器上,电压从较高逻辑电平(5V0或3V3)下降到低至0V8是很常见的。

定义高级处理器PDN的电源树如下所示。该示例旨在说明如何构建不同的电源轨,这些轨道来自为整个系统供电的主电源或稳压器。

处理器的PDN拓扑示例需要四个电压逐渐降低的不同电源轨

处理器的PDN拓扑示例需要四个电压逐渐降低的不同电源轨

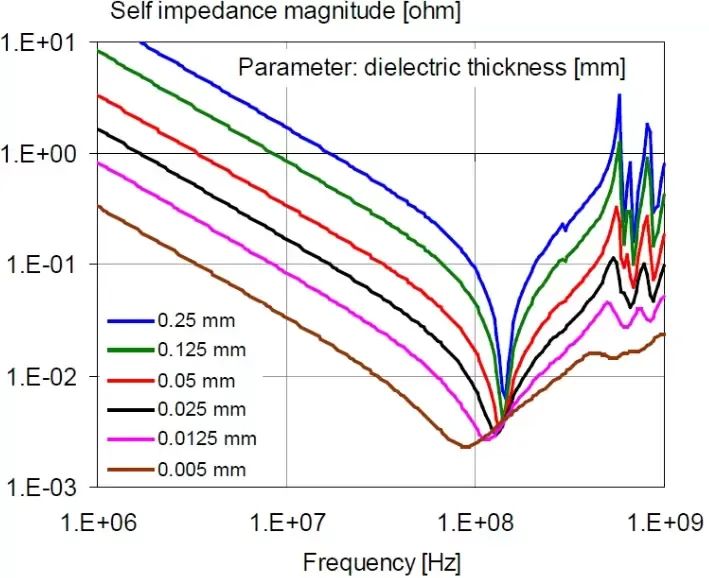

- 在中档频率下提供更高的电容,从而降低阻抗(高达1 GHz)

- 将与电源/接地层对相关的PDN谐振移至较低频率

- 抑制与电源/接地层对相关的GHz范围内的PDN谐振峰值

- 将与平面电容相关的PDN阻抗谷值(从0.1到1 GHz)移至较低频率

-

pcb

+关注

关注

4391文章

23742浏览量

420693

原文标题:PCB电源完整性完整指南:从电路板到封装

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高频PCB布线“避坑指南”:4大核心技巧让信号完整性提升90%

了解信号完整性的基本原理

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

电源完整性基础知识

各种常用电路模块设计原则:电源完整性

受控阻抗布线技术确保信号完整性

使用罗德与施瓦茨RTE1104示波器进行电源完整性测试

电源完整性分析及其应用

技术资讯 | 信号完整性测试基础知识

电源完整性理论基础

是德示波器在电源完整性分析中的应用

听懂什么是信号完整性

PCB电源完整性完整指南:从电路板到封装

PCB电源完整性完整指南:从电路板到封装

评论