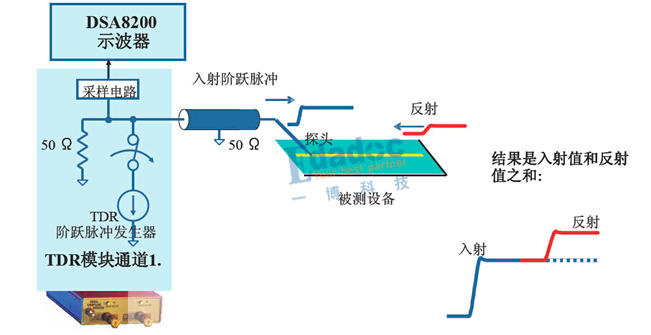

经常测试阻抗的朋友应该知道,当PCB板Trace走线较长时,测试阻抗 结果会出现末端上飘现象。

原因:较长走线的DC电阻叠加在阻抗曲线上,看上去曲线后段阻抗偏高,其实并不是走线的真实阻抗。

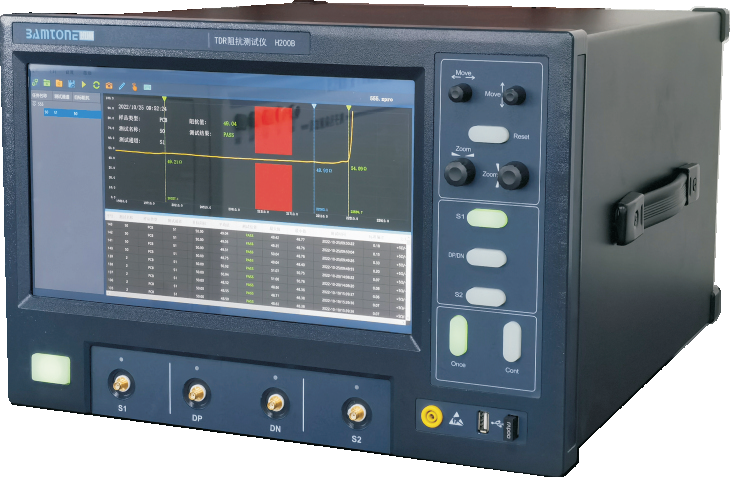

为了更清楚判断常规上飘的大致位置,做了以下几个实验:

验证如下:

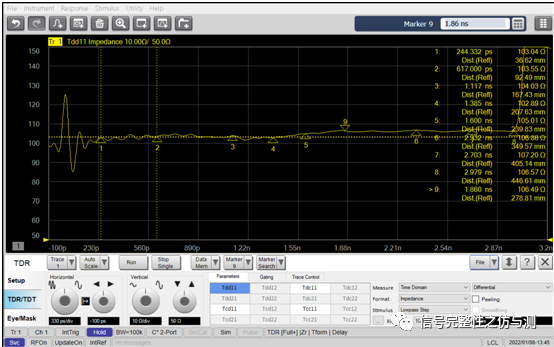

1. 10inch表层走线

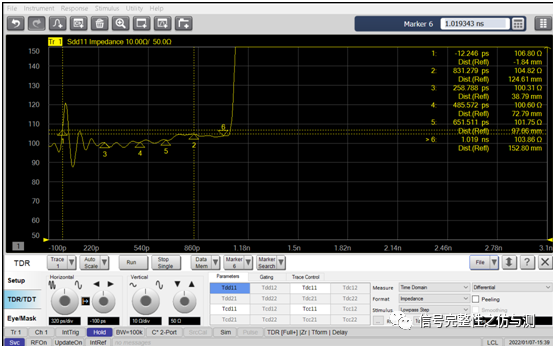

从走线左右端测试点分别测试,Mark9 1.86ns处均开始明显上飘。图1的Mark6对应图2的Mark2,对应不上,说明此处已经上飘。图1的Mark9对应图2的Mark3,反过来亦成立。Mark4和Mark5也成立。说明Mark9是上飘临界点成立。

换算后为约为6inch长度。

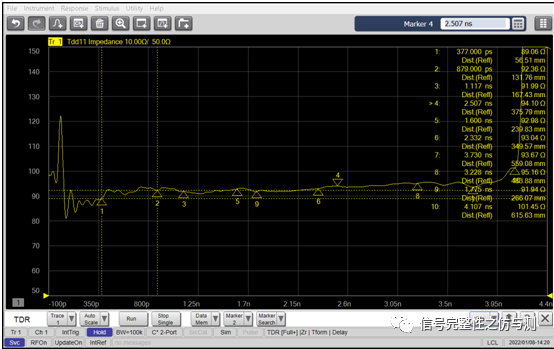

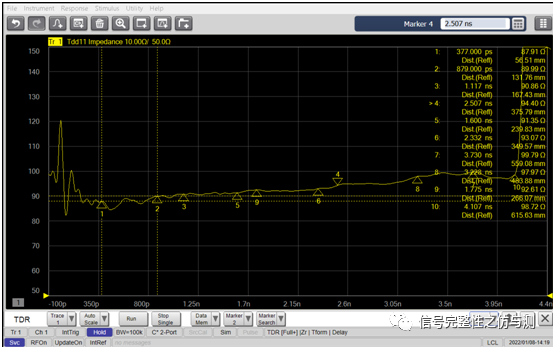

2.13inch内层走线

同样从左右两端测试,均是Mark6 2.332ns处明显上飘。图1的Mark4与图2的Mark5对应不上,说明此处已经上飘。图1的Mark6对应图2的Mark9,反之亦成立。说明Mark6是上飘临界点成立。

换算后为约为7inch长度。

解决方案:阻抗测试时读数不要读取上飘后的数据,如果需要确认是否是上飘可以从左右两端分别测试,看看阻抗曲线前半部分,验证一下上飘是否是真实的。

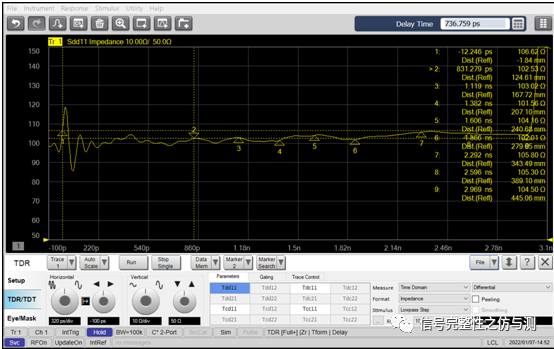

3.全长曲线和切除上飘后的曲线,可以看到上飘不影响前端走线阻抗值。

4.全长曲线、切除上飘后左端测试、切除上飘后右端测试。有时候上飘的位置阻抗确实就是没做好,是真的高。

左端测试

右端测试

当然,这个上飘位置不是绝对的,还跟你用的板材,线宽、铜厚、线长等因素都有关系。只能说给自己留有个判断的依据而已。

其实测的多了,波形上几乎也就看出来了。

审核编辑:汤梓红

-

PCB板

+关注

关注

27文章

1506浏览量

55558 -

波形

+关注

关注

3文章

407浏览量

33217 -

TDR

+关注

关注

1文章

78浏览量

21109 -

阻抗测试

+关注

关注

0文章

16浏览量

1880

原文标题:TDR阻抗测试上飘问题

文章出处:【微信号:si-list,微信公众号:高频高速研究中心】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Pico示波器PicoScope 9311进行TDR测试流程详解

高速串行数据挑战与TDR阻抗测试和高速串行链路的分析

什么是TDR?TDR测试原理分析

传输线的TDR阻抗的原因和原理分析

如何用LOTO示波器TDR方法测试电线长度?

TDR阻抗测试上飘问题分析

TDR阻抗测试上飘问题分析

评论