引言:在异步逻辑器件中,信号不与时钟信号同步,或者说该信号压根就没有对位的时钟信号。本节简述基本的异步逻辑--->1位拓扑和多位拓扑的缓冲器、反相器、驱动器和收发器。

1.反相器

反相器实质就是一个非门,单反相器就是一个单非门,正逻辑中执行布尔函数

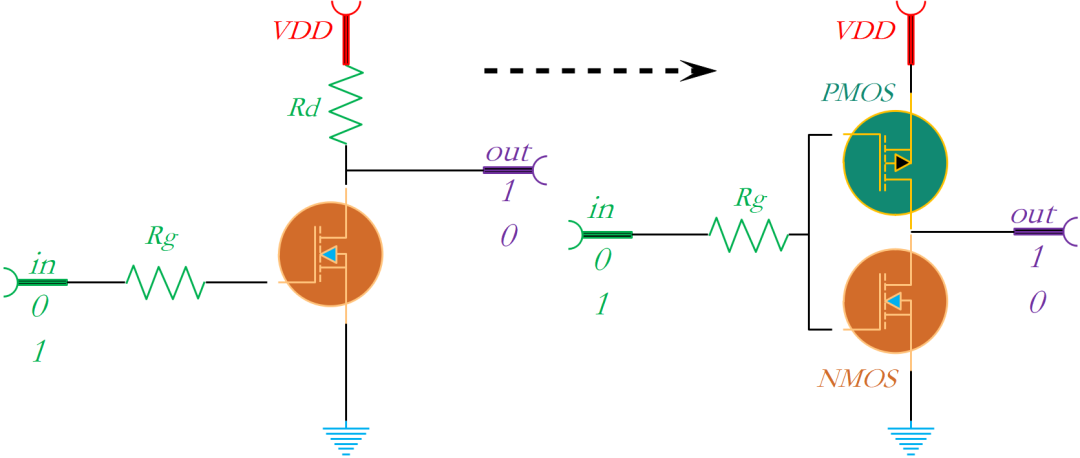

Y=A。如图2-1右所示是CMOS结构的非门,芯片里面的最原始的构成就是如此。

图2-1:CMOS结构的非门

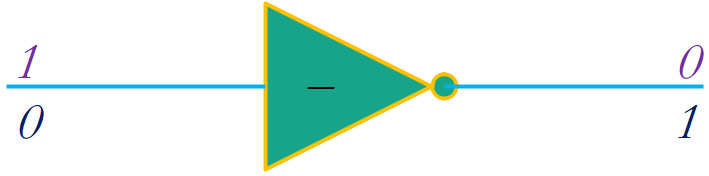

图2-2:非门图例

图2-3:反相器输入输出波形

对于反相器的关键参数,一个是时延,即输入和输出之间的延迟,一个是上升/下降时间,这两个体现出反相器的性能

2.缓冲器(驱动器)

图2-4:缓冲器图例

如图2-4是缓冲器的图例,注意这里是缓冲而不是缓存Buffer,缓冲器在结构上是由两个及以上反相器组成,如图2-5是偶数的同相缓冲器示例,图2-6是奇数反相缓冲器示例,图2-7是带控制的单通道同相缓冲器。

图2-5:同相缓冲器

图2-6:反相缓冲器

图2-7:带控制单通道同相缓冲器

从图2-1的结构可以看出缓冲器将开关变化映射到VDD的切换,所以缓冲器可以用于刷新微弱的数字信号,这些信号通常是由连接到相当大的电容性负载或许多并联输入端的低强度驱动输出产生的。缓冲器的输出能重建一个适当形状的数字波形并改善信号完整性,提供同相和反相两种功能,图2-8显示缓冲器的刷新效果。

图2-8:同相缓冲器改善波形

3.收发器

如 图2-9

,收发器是一个双向缓冲器,用于从数据总线接收和/或向数据总线发送数据,使用方向控制引脚选择数据流的方向。数字信号的本质就是0和1,电气层面就是高低电平不断切换,芯片接收端接收到信号后传递给ADC或者电平比较器作阈值判断以此来识别接收的信号是0还是1。

独立的收发器元器件,从其缓冲器构成来看,也是做一个信号中继和增强,重建一个适当形状的数字波形并改善信号完整性。

图2-9:收发器结构

简单的收发器由两个缓冲器和方向控制电路组成,其他类型的收发器还包括锁存器或寄存器,可以存储输入值并在需要时将其释放到输出端。收发器具有多种拓扑,例如与总线连接要求有关的1、2、4、8、16或18位版本,收发器可提供多种相关功能:

1:开漏输出

2:输入总线保持功能可在输入端未获有效驱动时保持输入值

3:施密特触发器和施密特动作输入提供输入迟滞

-

收发器

+关注

关注

10文章

3838浏览量

111458 -

驱动器

+关注

关注

54文章

9115浏览量

156509 -

缓冲器

+关注

关注

6文章

2236浏览量

49050 -

反相器

+关注

关注

6文章

332浏览量

45344 -

逻辑器件

+关注

关注

0文章

108浏览量

20772

发布评论请先 登录

缓冲器/线路驱动器,非反相(IC)74HC244D,65374HC244D

具有开漏输出的十六进制反相器缓冲器/驱动器SN74AUC06 数据表

漏极开路输出的十六进制反相器缓冲器/驱动器SN74LVC06A数据表

异步逻辑器件之反相器、缓冲器(驱动器)和收发器

异步逻辑器件之反相器、缓冲器(驱动器)和收发器

评论