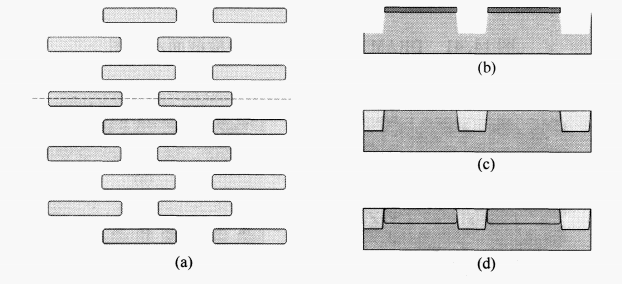

在下面的图中较为详细的显示了堆叠式DRAM单元STI和阱区形成工艺。下图(a)为AA层版图,虚线表示横截面位置。下图(b)为AA刻蚀后的横截面;下图(c)为形成STI后的横截面;下图(d)显示了P阱形成后的横截面。STI和P阱形成过程由于相对较为独立,所以可以同时在外围区域进行。此处P阱形成通过一个P阱光刻版。外围区域有更精细的图形,单元区域为空白。N阱只在外围区域,而不在单元区域,这是因为DRAM单元只有NMOS。

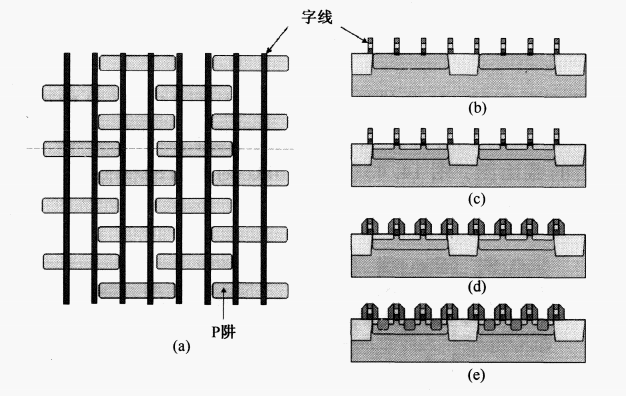

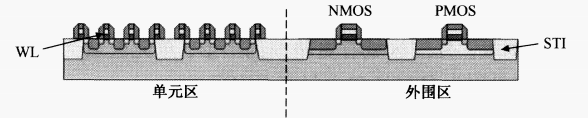

下图详细显示了堆叠式DRAMSTI和阱区形成过程。下图(a)所示为与AA层重叠的WL层布局图,虚线表示横截面的位置。下图(b)显示了DRAM单元NMOS栅的横截面,这就是字线(WL)。下图(c)所示为轻掺杂漏(LDD)形成工艺;下图(d)为侧壁间隔层形成工艺;下图(e)为源/漏极形成工艺。两个版图没有显示在下图中,分别为外围区域的PMOSLDD和PMOSSD(见下图的右侧)。钻硅化物用于外围区域以减小接触电阻。

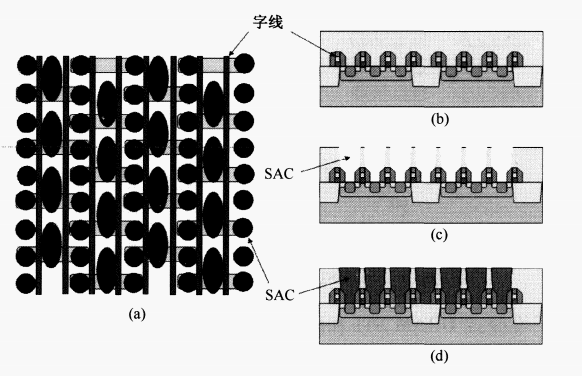

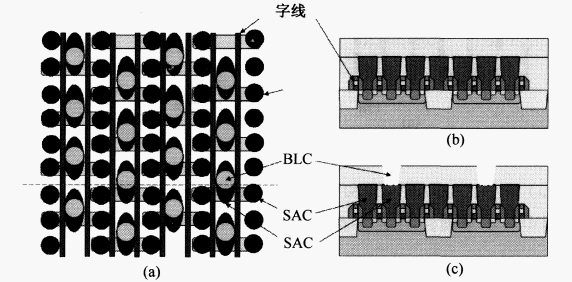

下图(a)显示了第一层接触,即所谓的堆叠式DRAM自对准接触(SAC)。有些人也称这种模式为刻蚀后焊盘接触(LPC),或多晶硅CMP后的多晶硅焊盘(LPP)。因为内部接触孔和短的WL是致命缺陷,通过ILD0刻蚀接触孔非常具有挑战性,通常在密集的字线之间使用硅酸盐玻璃(BPSG)达到NMOS的源/漏极。因此,需要发展自对准接触工艺。通过在字线的顶部保留氮化物硬掩膜并在两边形成侧壁氮化物,WL被氮化物包围。当SAC刻蚀工BPSG和氮化物之间具有足够高的刻蚀选择性时,刻蚀过程成为自对准过程,这样可以使得接触孔通过密集的WL达到硅表面而无短路。

多晶硅沉积填充SAC孔之前,通常使用高剂量N型接触离子注入用于减小接触电阻。电子束检查通常用于捕获刻蚀和多晶硅CMP后形成的无孔接触或栓塞WL接触缺陷。SAC工艺在阵列区域。

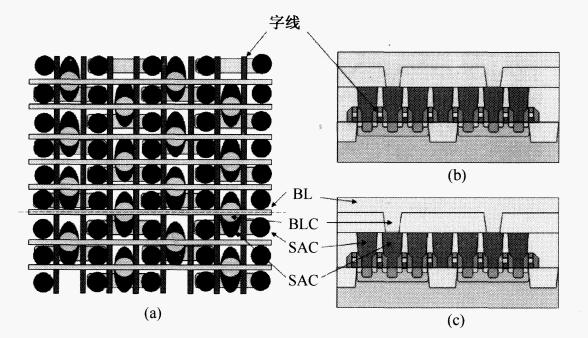

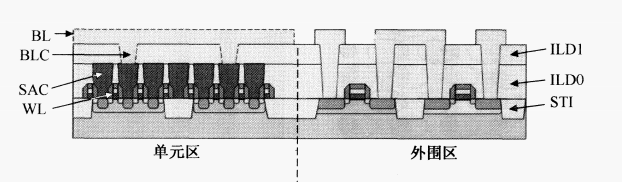

在下图中显示了堆叠式DRAM位线接触(BLC)。从下图(a)中可以看出位线接触在SAC栓塞上连接到AA层的中间部分。每个BLC连接两个DRAM单元。下图(b)显示了ILD1沉积和CMP后的截面图,下图(c)中BLC刻蚀后的横截面。对于堆叠式DRAM,ILD1通常是BPSG。

外围区域的位线接触可以通过阵列区域的BLC图形化,由于阵列和外围区域的BLC在尺寸和深度方面差别很大,因此工艺工程师一般将这两种接触工艺过程分开。

下图(a)显示了堆叠式DRAM的位线(BL)结构。可以看出,位线通过和位于SAC栓塞上的BLC与AA层中间部分连接。鸨(W)是最常用于形成BL的金属。Ti/TiN阻挡层/黏合层沉积后,W使用CVDX艺沉积填充BLC孔并在晶圆表面形成薄膜。BL光刻版定义出阵列和外围区域的BL金属线,并通过金属刻蚀过程形成BL图形。下图显示了BL和BLC形成后阵列和外围区域的横截面。为了防止BL短路接触,通常在BL侧壁上形成空间层。

审核编辑:刘清

-

半导体

+关注

关注

328文章

24506浏览量

202146 -

DRAM芯片

+关注

关注

1文章

80浏览量

17881 -

CMP

+关注

关注

6文章

136浏览量

25667 -

接触电阻

+关注

关注

1文章

88浏览量

11702 -

NMOS管

+关注

关注

2文章

115浏览量

5230

原文标题:半导体行业(二百零二)之ICT技术(十二)

文章出处:【微信号:FindRF,微信公众号:FindRF】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

13um应变补偿多量子阱SLD台面制作工艺的研究

三星宣布:DRAM工艺可达10nm

浅析DRAM和Nand flash

基于嵌入式系统中DRAM控制器该怎么设计?

DRAM,SRAM,FLASH和新型NVRAM:有何区别?

芯片堆叠的主要形式

求一种DRAM控制器的设计方案

DRAM芯片中的记忆单元分析

配备DRAM的三层堆叠式CMOS影像传感器介绍

张卫:先进CMOS制造工艺的技术演进及自主发展思考

动态随机存储器集成工艺(DRAM)详解

堆叠式DRAM存储节点相关部分的结构分析

堆叠式DRAM单元STI和阱区形成工艺介绍

堆叠式DRAM单元STI和阱区形成工艺介绍

评论