1 LVPECL与LVPECL之间的连接

LVPECL 到LVPECL 的连接分直流耦合和交流耦合两种形式

1.1 直流耦合

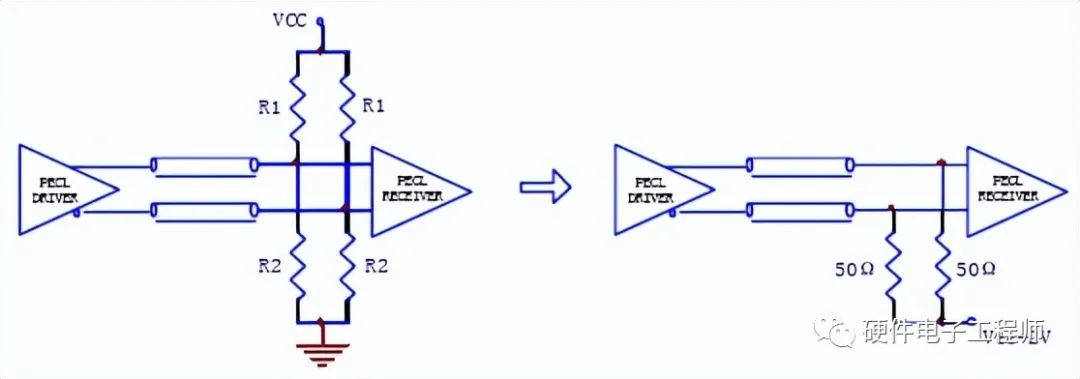

LVPECL 负载一般考虑是通过50Ω接到Vcc-2V 的电源上,一般该电源是不存在的,通常的做法是利用电阻分压网络做等效电路,如图3.1 中所示,该等效电路应满足如下方程:

图3.1 等效电路

Vcc − 2 V = Vcc R2/(R1+R2)

R1*R2/(R1 + R2)=50Ω

解上面方程组,得到:

R1 = 50VCC/(VCC-2V) R2 = 25VCC

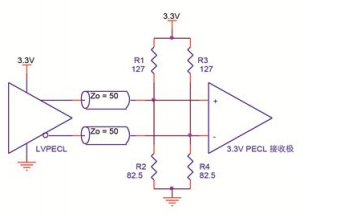

图3.2 给出了这两种供电情况时的详细电路。

图3.2 PECL电路之间直流耦合

在3.3V 供电时,电阻按5%的精度选取,R1为130Ω,R2为82Ω;在5V 供电时(此时为PECL电平),R1为82Ω,R2为130Ω。

1.2 交流耦合

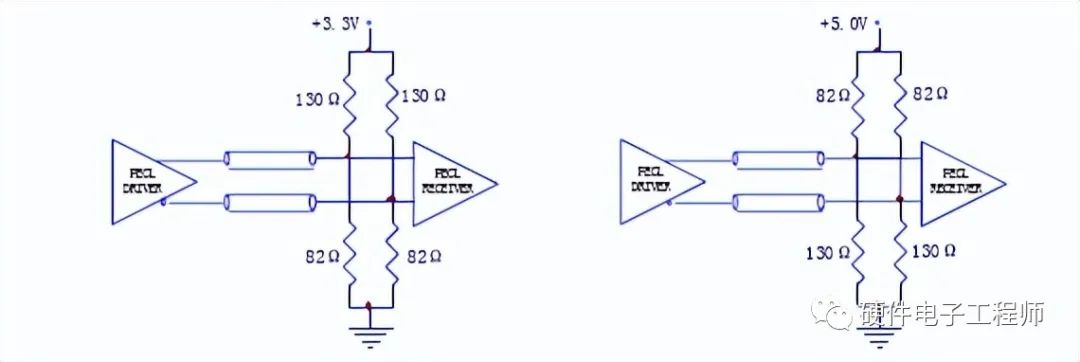

PECL 的输出共模电压需固定在Vcc-1.3V,在选择直流偏置电阻时仅需该电阻能够提供

14mA 到地的通路,这样R1=(Vcc-1.3V)/14mA。在3.3V 供电时,R1=142Ω,5V 供电时,R1=270Ω。然而这种方式给出的交流负载阻抗低于50Ω,在实际应用中,3.3V 供电时,R1 可以从142Ω到200Ω之间选取,5V 供电时,R1 可以从270Ω到350Ω之间选取,原则是让输出波形达到最佳。

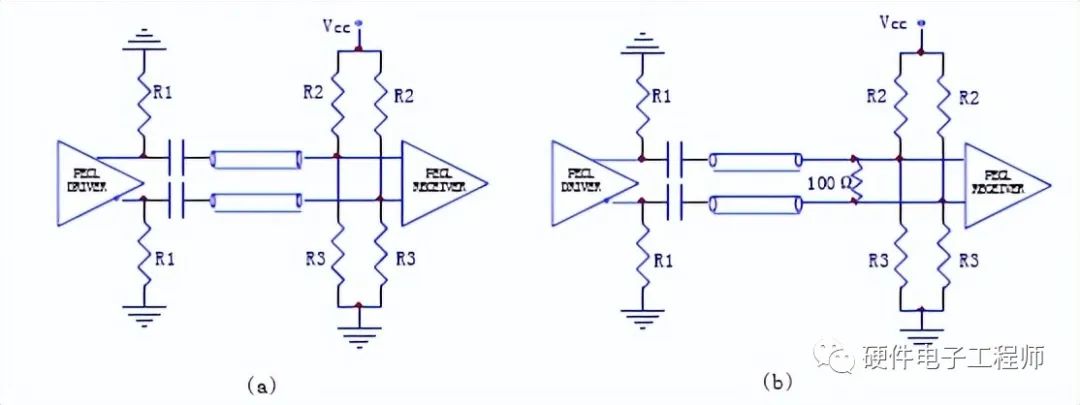

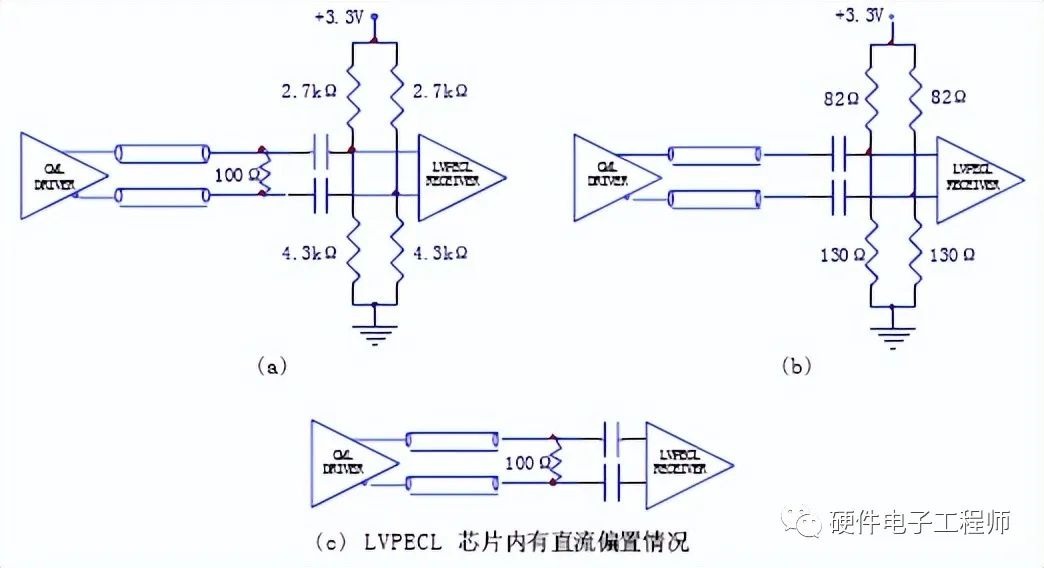

图3.3中分别给出了两种电路结构,在图3.3 (a)有一个缺点就是它的功耗较大,当对功耗有要求时,可以采用图3.3(b)所示电路结构。

图3.3 PECL电路间交流耦合

在图3.3 (a)中,R2和R3通常选取:

R2 = 82 Ω / R3 = 130 Ω +3.3 V供电时

R2 = 68 Ω / R3 = 180 Ω +5 V供电时

在图3.3 (b)中,R2和R3通常选取:

R2 = 2.7 KΩ / R3 = 4.3 KΩ +3.3 V供电时

R2 = 2.7 KΩ / R3 = 7.8 KΩ +5 V供电时

2 LVDS与LVDS接口的连接

LVDS 用于低压差分信号点到点的传输,该方式有三大优点,从而使得它更具有吸引力:

(1)LVDS 传输的信号摆幅小,从而功耗低,一般差分线上电流不超过4mA,负载阻抗为100Ω。这一特征使它适合做并行数据传输。

(2)LVDS 信号摆幅小,从而使得该结构可以在2.4V 的低电压下工作。

(3)LVDS 输入单端信号电压可以从0V 到2.4V 变化,单端信号摆幅为400mV,这样允许输入共模电压从0.2V 到2.2V范围内变化,也就是说LVDS 允许收发两端地电势有±1V的落差。

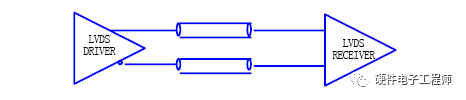

图3.4 LVDS间连接

因为LVDS 的输入与输出都是内匹配的,所以LVDS 间的连接可以如图3.4那样直接连接。但在设计时需要确认芯片内部,其接收端差分线对间是否已有100Ω电阻匹配,若没有则需在外面加100Ω电阻,电阻需靠近接收端放置。

3 CML电平之间的连接

CML 是所有高速数据接口形式中最简单的一种,它的输入与输出是匹配好的,从而减少了外围器件,也更适合于在高的频段工作。它所提供的信号摆幅较小,从而功耗更低。

CML 接口的输出电路形式是一个差分对,该差分对的集电极电阻为50Ω。假定CML 输出负载为一50Ω上拉电阻,则单端CML 输出信号的摆幅为Vcc~Vcc-0.4V。在这种情况下,差分输出信号摆幅为800mV,共模电压为Vcc-0.2V。若CML输出采用交流耦合至50Ω负载,这时的直流阻抗有集电极电阻决定,为50Ω,CML 输出共模电压变为Vcc-0.4V,差分信号摆幅仍为800mV。

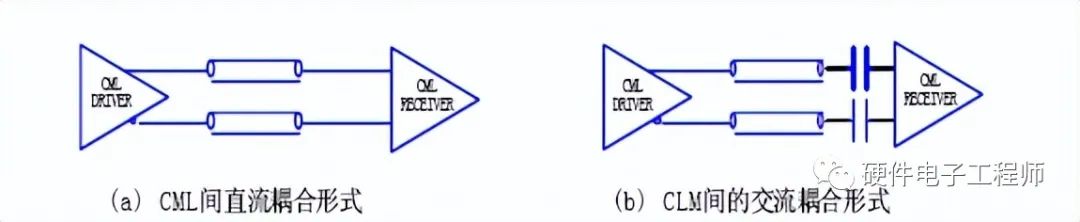

CML 到CML 之间连接分两种情况:

(1)当收发两端的器件使用相同的电源时,CML 到CML 可以采用直流耦合方式,这时不需加任何器件;

(2)当收发两端器件采用不同电源时,一般要考虑交流耦合,如图3.5 中所示,注意这时选用的耦合电容要足够大,以避免在较长连0 或连1 情况出现时,接收端差分电压变小。

图3.5 CML接口间连接

4 LVPECL到CML的连接

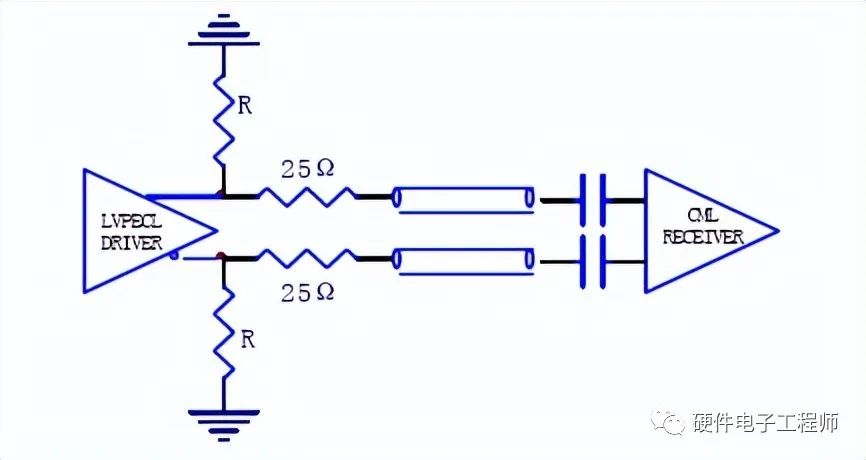

4.1 交流耦合

LVDS到CML的交流耦合连接方式如图3.6 所示。在LVPECL的两个输出端各加一个到地的偏置电阻,电阻值选取范围可以从142Ω到200Ω。如果LVPECL 的输出信号摆幅大于CML 的接收范围,可以在信号通道上串一个25Ω的电阻,这时CML 输入端的电压摆幅变为原来的0.67 倍。

图3.6 LVPECL到CML的交流耦合连接

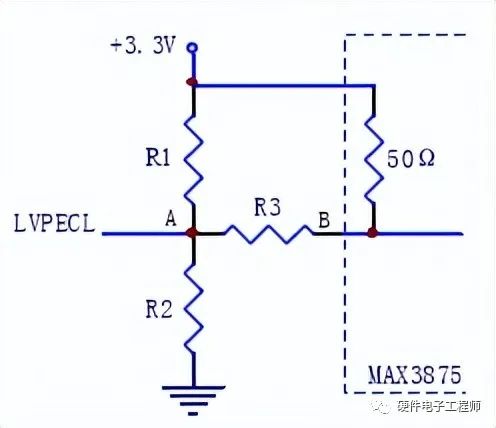

4.2 直流耦合

在LVPECL 到CML 的直流耦合连接方式中需要一个电平转换网络,如图3.7(a)中所示。该电平转换网络的作用是匹配LVPECL 的输出与CML的输入共模电压。一般要求该电平转换网络引入的损耗要小,以保证LVPECL 的输出经过衰减后仍能满足CML 输入灵敏度的要求;另外还要求自LVPECL端看到的负载阻抗近似为50Ω。下面以LVPECL驱动MAX3875 的

(a)直流耦合时电阻网络

(b)直流耦合连接

图3.7 LVPECL到CML的直流耦合连接

CML 输入为例说明该电平转换网络。如前所述,电阻网络需满足:

VA = VCC - 2.0V = R2·VCC /(R2 + R1//(R3 + 50Ω))

VB = VCC - 0.2V = (VCC·R3 + 50Ω·(VCC - 1.3V))/(R3 + 50Ω)

Zin = R1// R2 // (R3 + 50 Ω)= 50 Ω

Gain = 50 /(R3 + 50) ≥ 0.125

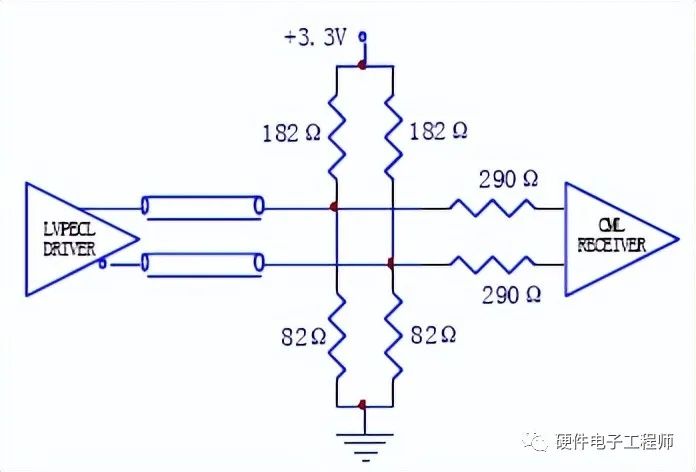

求解上面的方程组,我们得到R1=182Ω,R2=82Ω,R3=290Ω,VA=1.35V,VB=3.11V,Gain=0.147,Zin=49Ω。

LVPECL 到MAX3875 的直流耦合结构如图3.7(b) 所示。对于其它产品的CML 输入,最小共模电压和灵敏度可能不同,设计时可修改VB值,再根据上面的公式计算所需的阻值。

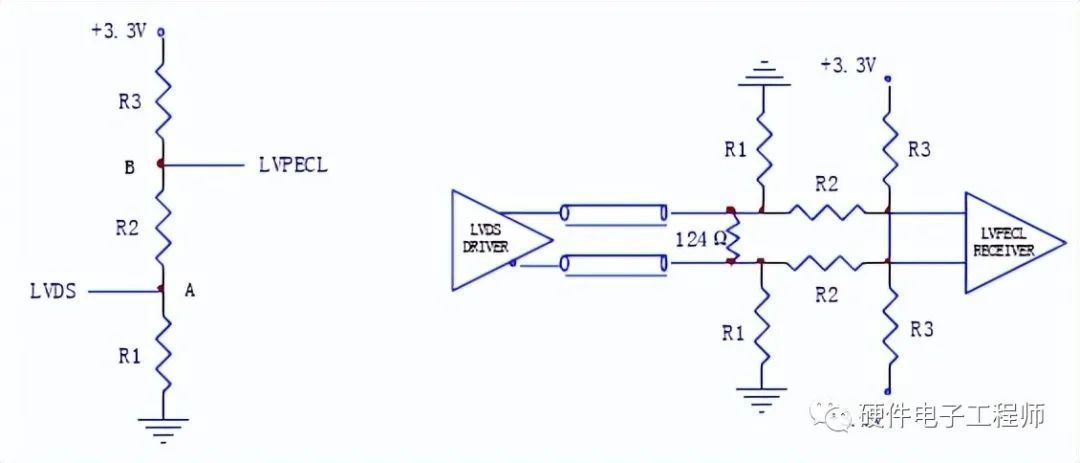

5 CML到LVPECL的连接

图3.8中,给出了CML到LVPECL的交流耦合连接。由于CML与LVPECL接口的中心电平不同,

图3.8 CML到LVPECL的交流耦合连接

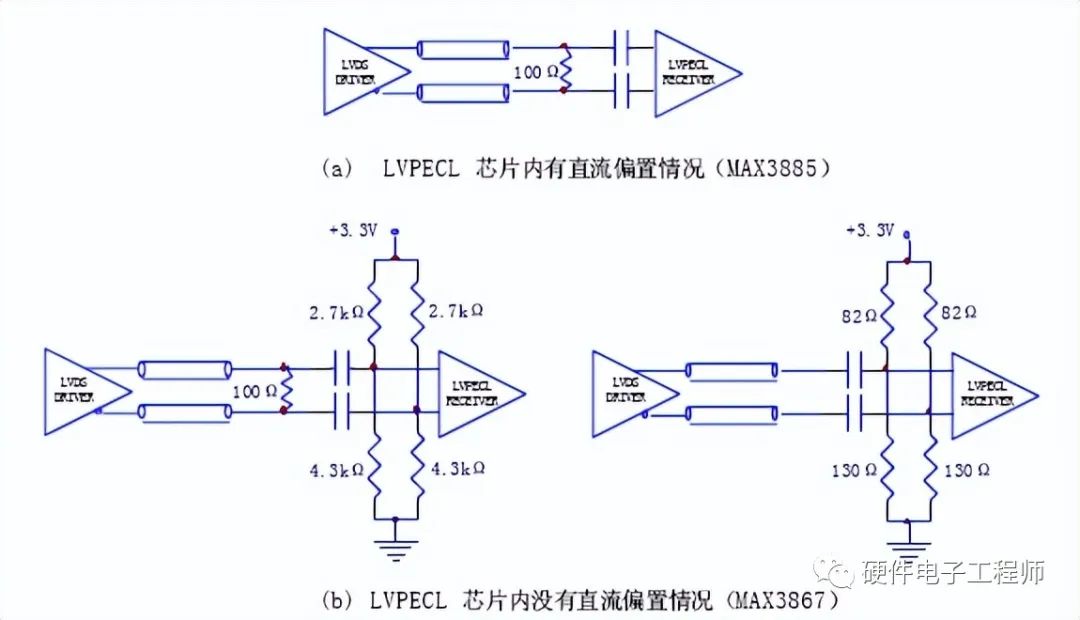

通常采用交流耦合,LVPECL输入接口需要外加直流偏置,保证中心电平在VCC-1.3V,图8(a)、(b)分别是外部加直流偏置电阻的连接方式。其中,(a)的连接方式功耗较低。(c)为芯片内已有直流偏置时的连接电路。

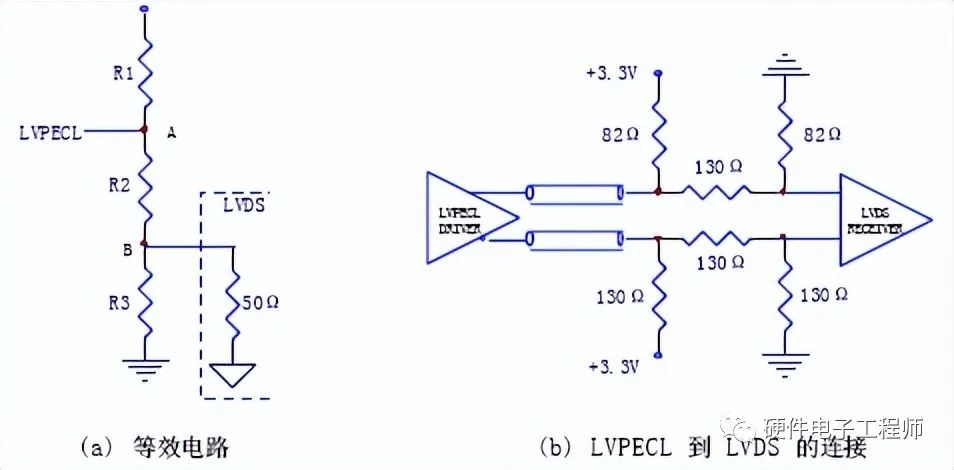

6 LVPECL到LVDS的连接

6.1 直流耦合

LVPECL到LVDS 的直流耦合结构需要一个电阻网络,如图3.9中所示,设计该网络时有这样几点必须考虑:首先,我们知道当负载是50Ω接到Vcc-2V 时,LVPECL 的输出性能是最优的,因此我们考虑该电阻网络应该与最优负载等效;然后我们还要考虑该电阻网络引入的衰减不应太大,LVPECL 输出信号经衰减后仍能落在LVDS 的有效输入范围内。

注意LVDS 的输入差分阻抗为100Ω,或者每个单端到虚拟地为50Ω,该阻抗不提供直流通路,这里意味着LVDS输入交流阻抗与直流阻抗不等.经计算,电阻值为:R1=182Ω,R2=48Ω,R3=48Ω。电阻靠近接收侧放置。

图3.9 LVPECL到LVDS的直流耦合结构

6.2 交流耦合

LVPECL 到LVDS 的交流耦合结构如图3.10 所示,LVPECL 的输出端到地需加直流偏置电阻(142Ω到200Ω),同时信号通道上一定要串接50Ω电阻,以提供一定衰减。LVDS 的输入端到地需加5KΩ电阻,以提供近似0.86V 的共模电压。

图3.10 LVPECL到LVDS的交流耦合结构

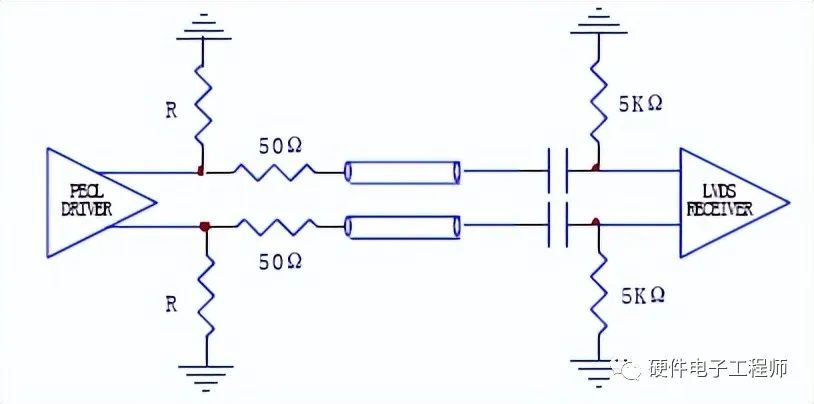

7 LVDS到LVPECL的连接

7.1 直流耦合

LVDS到LVPECL 的直流耦合结构中需要加一个电阻网络,如图3.11 所示,该电阻网络完成直流电平的转换。LVDS输出电平为1.2V,LVPECL的输入电平为Vcc-1.3V。LVDS 的输出是以地为基准,而LVPECL 的输入是以电源为基准,这要求考虑电阻网络时应注意LVDS 的输出电位不应对供电电源敏感;

另一个问题是需要在功耗和速度方面折中考虑,如果电阻值取的较小,可以允许电路在更高的速度下工作,但功耗较大,LVDS 的输出性能容易受电源的波动影响;

还有一个问题就是要考虑电阻网络与传输线的匹配。经计算,电阻值选取为:R1=374Ω,R2=249Ω,R3=402Ω,VA=1.2V,VB=2.0V,RIN=49Ω,Gain=0.62。LVDS 的最小差分输出信号摆幅为500mV,在上面结构中加到LVPECL 输入端的信号摆幅变为310mV,该幅度低于LVPECL 的输入标准,但对于绝大多数MAXIM 公司的LVPECL 电路来说,该信号幅度是足够的。设计中可根据器件的实际性能作出自己的判断。

图3.11 LVDS到LVPECL的直流耦合结构

7.2 交流耦合

LVDS 到LVPECL 的交流耦合结构较为简单,只需要LVPECL输入侧加直流偏置,满足其中心电压的要求。图3.12 (a)、(b)两种为常用到的结构。

图 3.12 LVDS到LVPECL的交流耦合结构

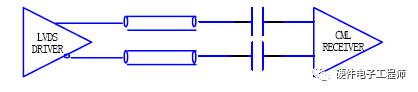

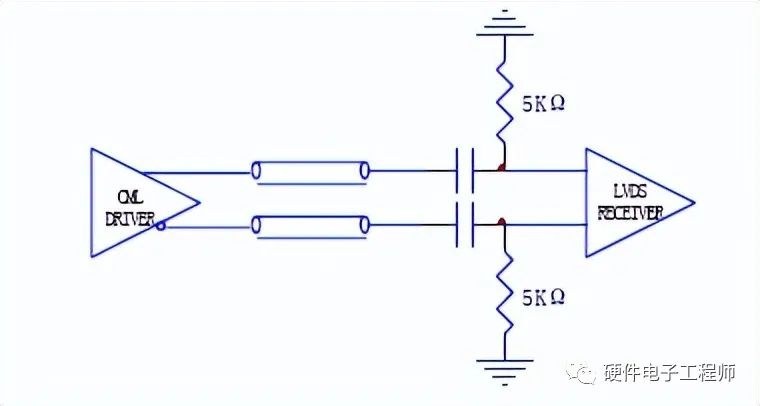

8 CML到LVDS的连接

CML到LVDS的连接通常采用交流耦合结构,图3.13、14给出了两种电路结构,需注意CML 的输出信号摆幅应落在LVDS 的有效工作范围内。

图3.13 CML到LVDS的交流耦合结构

图3.14 CML到LVDS的交流耦合结构

9 差分信号设计原则

在差分信号传输设计中,不同类型的差分线,其输入输出的中心电平不同,摆幅也不同。但设计中,以下设计原则还是比较通用的。

(1)差分线的正、负端要求等长。一般来说,对于155Mbps的差分线对,其长度差应控制在160mil以内,建议控制在80mil以内;622Mbps的差分线对,控制在40mil以内;其余按速率类推,或根据datasheet推荐的值进行约束。

(2)差分阻抗控制在100 +/-10%Ω。

(3)数据差分线与其它非时钟信号线的边到边间距应大于2倍线宽,与时钟信号线或时钟差分线应大于3倍线宽。

(4)一般来说,差分线在布线时尽量走内层,且要邻近平面层,表层走线尽量短;

(5)对于高速差分线为减少过孔数目,有时也允许走表层。差分线的过孔数目越少越好,在需要打过孔的情况下,差分线正、负信号线要成对打过孔,也即若正端信号线需要打过孔换层,负端信号线也需要在相应的位置打过孔。一般来说,155Mbps速率的差分线对,其过孔应数目控制在4个以内,622MGbps及1.25Gbps速率的应控制在3个以内;而2.5Gbps速率及以上的差分对,除在BGA下出线必须打过孔以及压接式接插件必须的压接过孔外,在其信号走线的其它位置尽量不要再打过孔。

(6)时钟信号在不同电平间转换时,尽量采用交流耦合结构。交流耦合电容,选取不宜太小,通常1GHz以上频率选0.01µF,以下的选取0.1µF。泻放电阻和匹配电阻在PCB中的布局和选择。对于有泄放电阻或终端匹配电阻的差分接口电路,泄放电阻R1应尽量放在驱动pin附近,匹配电阻R2和R3尽量靠近接收pin;

(7)考虑到散热和能承受的额定功率,最好选择选择0603封装的电阻,或者0805封装的电阻,不应选用0402及更小封装的电阻,否则应具体计算该电阻上的功耗。

审核编辑:刘清

-

PCB板

+关注

关注

27文章

1506浏览量

55560 -

电阻器

+关注

关注

22文章

4247浏览量

65710 -

电平转换器

+关注

关注

1文章

268浏览量

21199 -

LVPECL

+关注

关注

2文章

77浏览量

18902 -

交流耦合

+关注

关注

0文章

44浏览量

12643

原文标题:PECL/CML/LVDS高速接口互连电路设计

文章出处:【微信号:电子设计联盟,微信公众号:电子设计联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

LVDS、CML、LVPECL不同逻辑电平之间的互连(二)

浅谈LVDS、CML、LVPECL三种差分逻辑电平之间的互连

SiTime差分晶振的LVDS、LVPECL、HCSL、CML模式相互转换过程介绍

DAC3164 LVPECL接口的供电电压Vcc是3.3V吗?

关于LVPECL时钟信号的的疑问

LVPECL、VML、CML、LVDS 与LVDS之间的接口连接转换

LVPECL驱动器终端设计介绍

如何将Virtex 5 LVPECL_25连接到另一个设备的3.3v lvpecl?

如何使用BLVDS或其他驱动Kintex LVPECL输入的方法的信息?

如何在LVPECL、VML、CML、LVDS和子LVDS接口之间转换

如果ad9680的clk和sysref信号采用lvpecl格式输入,交流耦合的话前端网络如何设计?

设计LVPECL终端需要考虑那些原因

LVDS和CML与LVPECL的同种差分逻辑电平之间的互连教程

获得连接:LVPECL、VML、CML、LVDS 与子 LVDS 之间的接口连接

LVPECL与LVPECL之间是如何进行连接的?LVPECL到CML的连接?

LVPECL与LVPECL之间是如何进行连接的?LVPECL到CML的连接?

评论