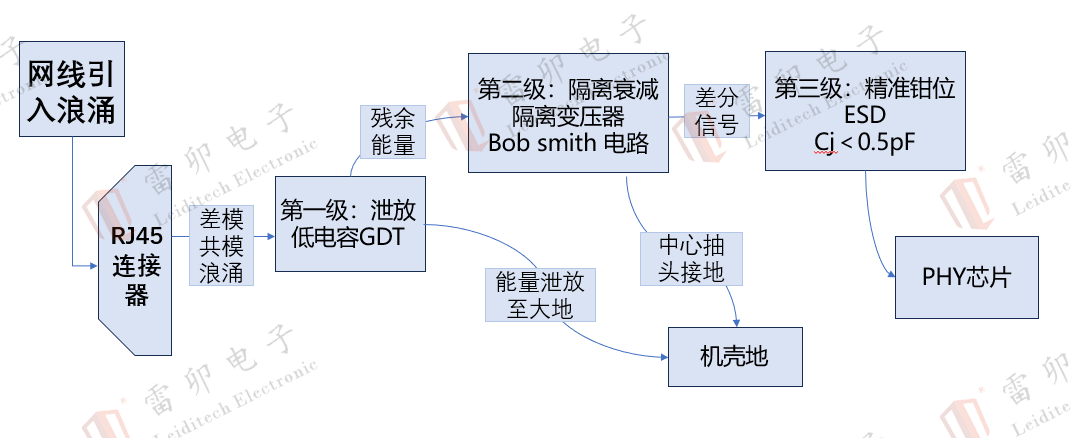

方案简介:

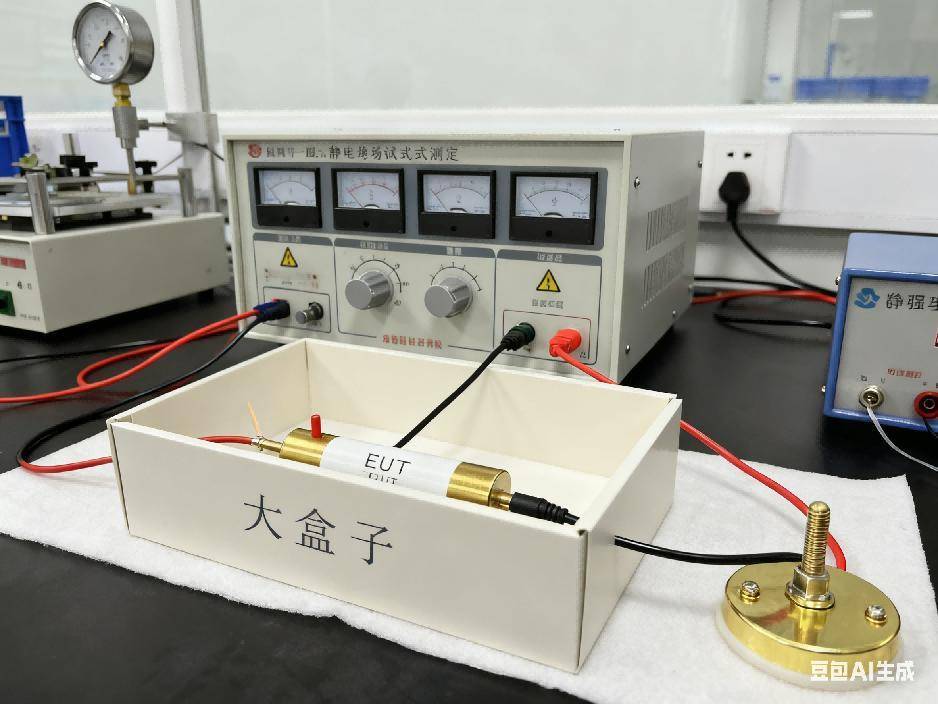

LVDS 是一种低摆幅的差分信号技术,利用非常低的电压摆幅(约 350mV)在 2 条 PCB 走线或者一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输,采用 LVDS 接口,可以使得信号在差分 PCB 线或平衡电缆上以几百 Mbps 的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗,LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用,常见于液晶电视中,LVDS 其较高的数据传输速率,普通的防护方案会对数据的传输造成一定影响。此方案高速差分信号部分采用集成低压四通道保护(有效降低后端残压值)、超低容值、低漏电、低残压的 ESD 防护器件,在不影响数据传输的前提下满足 IEC61000-4-2 Level 4 静电放电防护需求,让后端的电路得到有效防护。

产品图示:

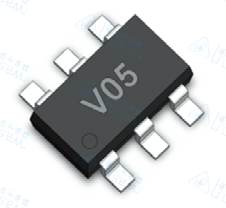

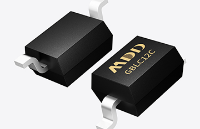

SRV05-4

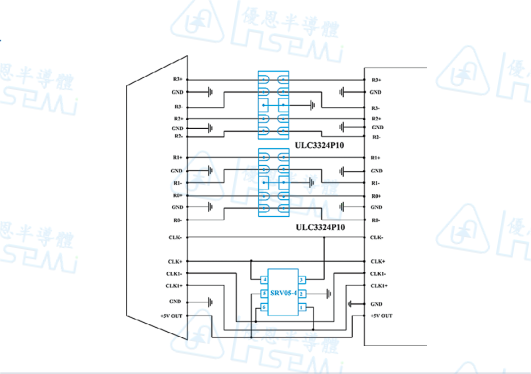

SRV05-4 ULC3324P10

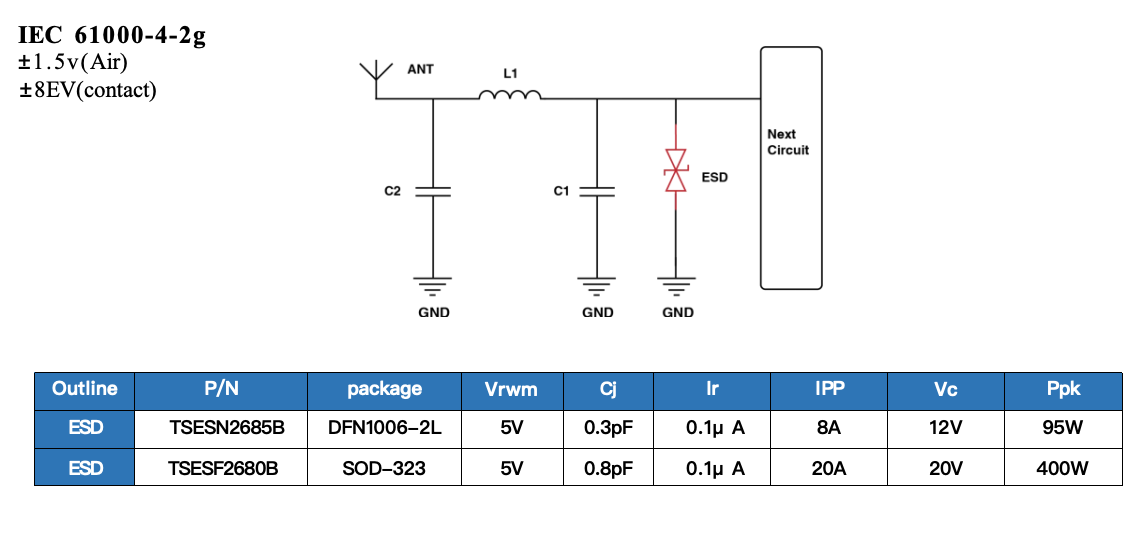

ULC3324P10应用示例:

符合要求 : ESD IEC 61000-4-2 Level 4

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电子元器件

+关注

关注

134文章

3970浏览量

114464 -

静电放电

+关注

关注

4文章

312浏览量

46089 -

lvds

+关注

关注

2文章

1244浏览量

70250 -

电路防护

+关注

关注

0文章

64浏览量

8419 -

集成元件

+关注

关注

0文章

2浏览量

5184

发布评论请先 登录

相关推荐

热点推荐

电子设备防护器件选型指南:守住电路的第一道防线

(ESD)专用器件

静电放电是电子设备最常遇到的威胁,尤其是在插拔接口、按键、外壳缝隙等处。

1. 关键参数

动态电阻 :比钳位电压更能反映ESD抑制能力。低动态电阻(<0.5Ω)的器

发表于 04-29 08:54

LVDS高速差分传输设计:全链路滤波与防护实战方案

。

四、典型LVDS 防护架构

CPU 输出的 LVDS 差分信号进入接口链路后:

先经过共模电感滤除电源与空间辐射带来的共模噪声;

再通过低容TVS 阵列吸收静电、浪涌、热

发表于 03-24 14:59

ESD防护入门:静电放电的本质与测试体系

讲解冬天脱毛衣时听到“噼啪”声,摸门把手时被“电”了一下?这就是生活中最常见的静电放电(ESD)现象。看似微小的静电,对电子设备来说可能是“致命杀手”——手机屏幕失灵、传感器误触发、芯片烧毁,很多时候都和ESD脱不了干系。今天我

静电放电?ZLG致远电子的“防护盾”了解一下

ESD是电子设备的常见隐患,它可能在不经意间对设备造成严重损害。本文将探讨ESD的成因、危害,以及ZLG致远电子如何通过其静电防护方案,确保电子设备的稳定运行。静电放电的成因与危害

电火工品静电敏感度测试及静电防护

危害,通过特定的电容器容量、放电电阻和测试电压等参数,对电火工品进行静电放电试验,观察其响应情况。 • 关键参数 :模拟人体试验时,电容器容量为 500pF /2nF,

电火工品静电敏感度测试及静电防护

电火工品静电敏感度测试主要依据GJB736.11A-2019《火工品试验方法第11部分:电火工品静电感度试验》。以下是该标准的详细要求:•试验原理:采用电容放电模型模拟人体静电危害,通

MDD静电二极管选型只看“静电电压等级”就够了吗?

在电子产品设计中,MDD辰达半导体的静电二极管是最常用的接口防护器件。许多工程师在选型时,往往会首先关注器件的ESD等级,例如标称可承受±8kV接触放电或±15kV空气放电。似乎只要

TVS布局对静电放电防护效果的影响分析

在产品开发设计的过程中发现,即使静电防护器件的选型足够严谨,器件设计参数的裕度足够充分,有时也不能达到理想的设计效果,在静电放电 (ESD) 测试过程中,常会出现功能丢失、死机等软失效

射频(RF)接口的ESD静电防护

上一期我们揭开了智能手环整体ESD防护的“防御体系”,从传感器到电路,每一层防护都在与静电这个“隐形杀手”博弈。而在这些防护环节中,射频(RF)接口堪称智能手环的“数据咽喉”——它

静电放电发生器操作步骤 干货满满

静电放电抗扰度测试仪是一种在性能上完全满足IEC61000-4-2、GB/T17626.2 标准要求的测试仪。其最大静电电压可以达到 30kV,足以覆盖标准中最严酷的

LVDS- 静电放电及插拔脉冲电压防护

LVDS- 静电放电及插拔脉冲电压防护

评论