直接数据频率合成器(DDS)因能产生频率捷变且残留相位噪声性能卓越而著称。另外,多数用户都很清楚DDS输出频谱中存在的杂散噪声,比如相位截断杂散以及与相位-幅度转换过程相关的杂散等。此类杂散是实际DDS设计中的 有限相位和幅度分辨率造成的结果。

其他杂散源与集成DAC相关——DAC的采样输出产生基波和相关谐波的镜像频率。另外,因DAC非理想的开关属性可能导致低阶谐波的功率水平升高。最后一种杂散源是在系统时钟频率的基波与任何内部分谐波时钟(例如,ADI直接数字频率合成器提供的SYNC_CLK)之间产生的混频产物。

上述杂散噪声的全部已知来源都可根据相对于DDS/DAC输出处基波信号的频率偏移进行预测。以下内容旨在帮助您确定DDS输出信号频谱中的杂散源。如果通过改变DDS频率调谐字使杂散与DDS/DAC相关,则并不难确定杂散源。这是因为改变调谐字时,上述所有杂散噪声的频率偏移均随基波变化。

如何确定DDS输出信号频谱中的杂散源例如,24 MHz基波有一个72 MHz的三阶谐波。如果DDS系统时钟为100 MHz,则三阶谐波与系统时钟的产物会折回到至28 MHz,与基波仅偏移4 MHz。如果基波增加10 KHz至24.010 MHz,则新的后叠积将偏移基波3.97MHz,这是可以提前预测的。 如果无论频率调谐字如何变化,杂散相对基波的频率偏移均保持不变,则DDS/DAC不是杂散源。相反,如果杂散相对基波的频率偏移随DDS调谐改变而变化,则DDS/DAC很可能是杂散源。通过确保频率调谐字变化包括频率调谐字的截断部分和未截断部分,可为发现杂散源带来方便。截断部分一般为调谐字的14位至19位(MSB)。

当DDS频率调谐字发生变化时,相对基波(载波)的频率偏移不发生改变的杂散一般分为两类:

注意,如果DDS的内部参考时钟乘法器(PLL)被启用,则DDS输出同样存在相对于基波的固定边带杂散,其频率偏移等于参考时钟频率。

参考时钟源杂散

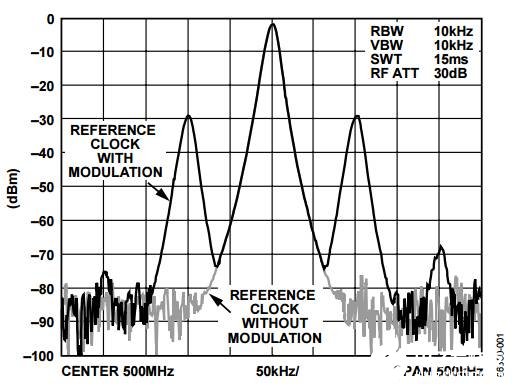

图1所示为DDS的500 MHz参考时钟,由一个100 KHz音实现10%的AM调制。该参考时钟源是一款Rohde andSchwartz具有调制功能的SMA信号发生器。图1中的灰色线为无调制条件下的参考时钟。

图1. DDS的500 MHz参考时钟

(由一个100 kHz音(蓝色线)实现10%的AM调制)

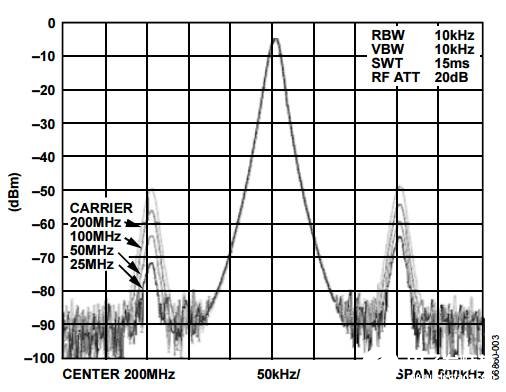

图2中,同一100 KHz音以完全相同的频率偏移传输到DDS/DAC输出,不受调谐字频率影响。图2中的频率调谐字表现出四个相互叠加的不同DDS载波。注意,在全部四个载波改变时,参考时钟杂散的频率偏移保持不变;但该杂散的幅度以20 log(x)为单位发生变化,其中,x为参考时钟频率与DDS载波频率之比。

图2. 四个DDS输出载波表现出100 kHz杂散产生的效应,该杂散对DDS的参考时钟(500 MHz)进行AM调制

开关电源杂散

图3和图4展示了DDS电源上的杂散(如开关电源)与DDS输出之间的关系。注意,如前所述,在相对于相同的载波变化时,它们也保持相同的固定频率偏移。

图3. 四个DDS输出载波表现出150 kHz杂散产生的效应,该杂散对DDS的电源进行AM调制

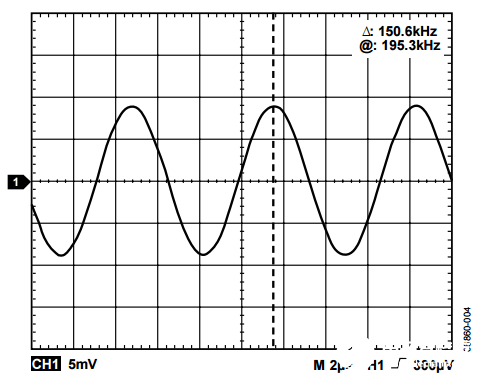

图4为DDS电源的实际时域,其中,一个150 kHz调制音施加于DDS电源之上,以仿真电源开关杂散。

图4. 150 kHz音(16 mV p-p)通过一个函数发生器施加于DDS电源之

DDS参考时钟或电源(一般为AVDD)上的杂散会对DDS输出产生一定的影响。结果,当载波变化时,以载波为中心的边带将保持不变。因此,调谐字发生变化时,如果在DAC/DDS输出中观察到固定杂散,则应检查参考时钟源和DDS电源中是否存在杂散。

查看往期内容↓↓↓

查看往期内容↓↓↓

原文标题:如何判定杂散来源?

文章出处:【微信公众号:亚德诺半导体】欢迎添加关注!文章转载请注明出处。

-

亚德诺

+关注

关注

6文章

4681浏览量

16731

原文标题:如何判定杂散来源?

文章出处:【微信号:analog_devices,微信公众号:analog_devices】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

压力变送器出现故障时应如何判定?又该遵循怎样的分析流程?

微电网稳定性分析:电压、频率稳定的核心判定标准

PCB外观品质标准判定规则

LightTools软件中光线路径分析仪的功能和使用方法

分享光纤受损的判定与诊断方法

API数据分析:淘宝流量来源分析,渠道优化!

PCB工程师必看!通孔、盲孔、埋孔的判定技巧

HUD纳米涂层的阳光模拟多角度杂散光测量

什么是晶振的杂散电容?

太阳光模拟器太空环境应用:光学载荷的杂散光性能测试

自动驾驶事故如何判定?谁应负主要责任?

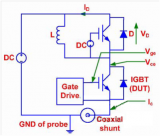

IGBT功率模块动态测试中夹具杂散电感的影响

无杂散、50 MHz 至 2.1 GHz 单通道小数 N 分频频率合成器 skyworksinc

杂散电感对IGBT开关过程的影响(2)

杂散电感对IGBT开关过程的影响(1)

如何判定杂散来源?

如何判定杂散来源?

评论