简介

UnixBench是一个开源的GPLv2许可的工具,它提供了对类Unix系统性能的基本指标。

通过运行UnixBench,可以获得有关系统性能的基本指标,用于与其他系统进行比较,也可以作为改进系统性能的参考。但UnixBench并不是一个综合性能评估工具,它只提供了一些基本的性能指标。要全面评估系统性能,还需要结合其他工具和测试来获得更全面的信息。

测试环境

| [硬件参数] | |

| 处理器: | SOPHON SG2042 x1 |

| 核心数: | 64核 |

| L1 Cache: | I:64KB and D:64KB |

| L2Cache: | 1MB/Cluster |

| L3Cache: | 64MB System Cache |

| DRAM: | Micron 2RX8 32G3200 RDIMM 4slot |

| [软件环境] | |

| linux版本: | 22.1 |

| gcc版本: | 12.2.0 |

| Unixbench版本: | 5.1.3 |

UnixBench测试项目介绍

Dhrystone(整数运算测试):

此基准用于衡量和比较计算机的性能。测试重点在于字符串处理,因为它没有浮点数运算。它受硬件和软件设计、编译器和链接器选项、代码优化、缓存内存、等待状态和整数数据类型等多种因素影响。

Whetstone(浮点数运算测试):

测量浮点数运算的速度和效率。该测试包含多个模块,用于表示科学应用程序中常用的操作混合。它使用了许多C函数,包括sin、cos、sqrt、exp和log等浮点数和整数数学运算,数组访问、条件分支和过程调用。此测试同时测量整数和浮点数算术。

Execl 吞吐量:

该测试测量每秒钟可以执行的 execl 调用次数。Execl 是 exec 函数族的一部分,它将当前进程图像替换为新的进程图像。它和许多其他类似的命令都是 execve() 函数的前端。

File Copy测试:

该测试测量数据从一个文件传输到另一个文件的速率,使用不同的缓冲区大小。文件读取、写入和复制测试捕获在指定时间内(默认为10秒)可以写入、读取和复制的字符数。

Pipe Throughput(管道吞吐)测试:

管道是进程之间最简单的通信形式。管道吞吐量是一个进程每秒钟可以将 512 字节写入管道并读取回来的次数。管道吞吐量测试在真实世界的编程中没有真正的对应项。

Pipe-based Context Switching (基于管道的上下文交互)测试:

此测试测量两个进程可以通过管道交换递增整数的次数。基于管道的上下文切换测试更像是一个真实的应用程序。测试程序生成一个子进程,通过双向管道进行对话。

Process Creation(进程创建)测试:

该测试测量一个进程可以 fork 和 reap 一个立即退出的子进程的次数。进程创建是指实际上为新进程创建进程控制块和内存分配,因此直接涉及内存带宽。通常,此基准测试用于比较各种操作系统进程创建调用的实现。

Shell Scripts测试:

Shell 脚本测试测量一个进程每分钟可以启动和收回一组一个、两个、四个和八个并发副本的 shell 脚本的次数,其中 shell 脚本对数据文件进行一系列转换。

System Call Overhead (系统调用消耗)测试:

估算进入和离开操作系统内核的成本,即执行系统调用的开销。它由一个简单的程序反复调用 getpid(返回调用进程的进程ID)系统调用组成。执行此类调用所需的时间用于估算进入和退出内核的成本。

Graphical Tests(图形)测试:

提供了2D和3D图形测试;目前,特别是3D套件非常有限,只包含 "ubgears" 程序。这些测试旨在提供对系统的2D和3D图形性能的大致了解。当然,报告的性能不仅取决于硬件,还取决于系统是否有适当的驱动程序。

测试

执行命令测试:

ubuntu@perfxlab:/public/benchmark/byte-unixbench_v5.1.3/UnixBench# ./Run

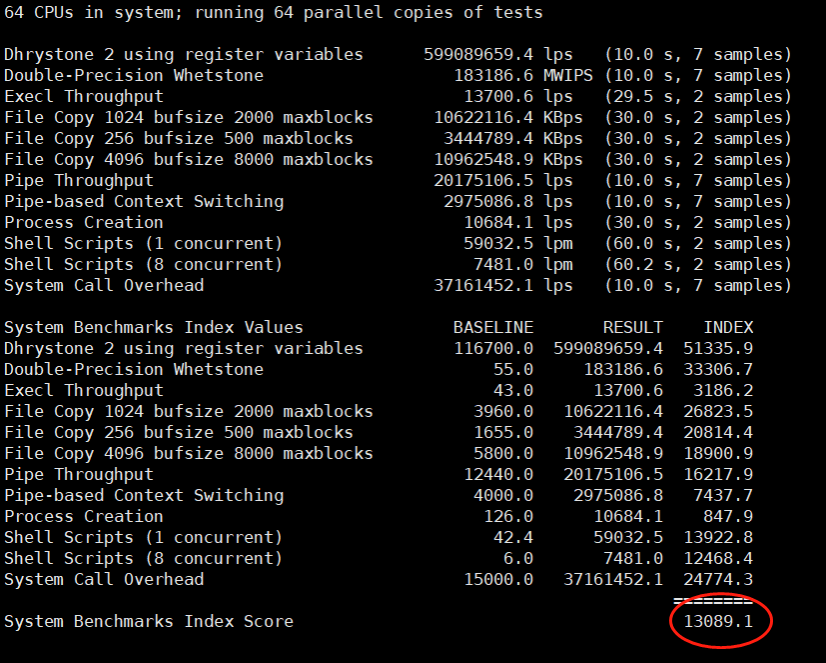

64核测试结果

结论

根据所提供的UnixBench基准测试结果,在多核情况下进行了系统性能测试。多核测试中,使用了所有64个CPU核心进行并行测试。

综合来看,多核测试明显展现了系统的并行计算优势,性能指标在各个方面得到了大幅提升。这些测试结果有助于评估系统在不同负载下的性能表现,并为优化系统配置和选择合适的硬件提供参考依据。需要注意的是,不同的应用场景可能对性能有不同的要求,因此综合考虑各个方面的指标是重要的。

正文完

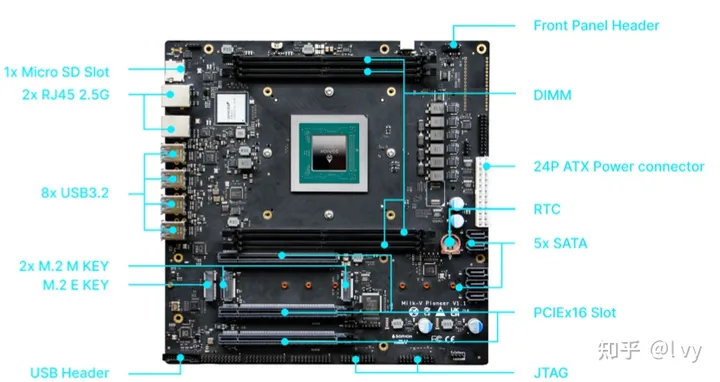

About HS-2

HS-2 RISC-V通用主板是澎峰科技与合作伙伴共同研发的一款专为开发者设计的标准mATX主板,它预装了澎峰科技为RISC-V高性能服务器定制开发的软件包,包括各种标准bencmark、支持V扩展的GCC编译器、计算库、中间件以及多种典型服务器应用程序。

HS-2 RISC-V通用主板搭载了一颗国产RISC-V 64核处理器(SG2042)。SG2042是目前已量产的性能最高的RISC-V处理器,主要针对高性能计算领域需求设计,适用于科学计算、工程计算、AI计算、融合计算等大算力应用场景。

关于RISC-V公共测试平台

RISC-V高性能处理器公共测试云平台 · 快速使用指南,下载链接:https://www.kdocs.cn/l/cmnYcyFIlVRx

RISC-V公共测试云平台系列文章

1. RISC-V公测平台发布 ·Stream带宽完整测试

2. RISC-V公测平台发布 · 我的世界MohistMC

3. RISC-V公测平台发布 · 第一个WEB Server“Hello RISC-V world!”

4. RISC-V公测平台发布 ·如何在SG2042上玩转k3s

5.“RISC-V成长日记” blog发布,第一个运行在RISC-V服务器上的blog?

6. RISC-V公测平台发布:如何在SG2042上玩转OpenMPI

7. RISC-V公测平台发布:Compiling The Fedora Linux Kernel Natively on RISC-V

8. RISC-V公测平台发布 · Unix Bench完整测试(本篇)

审核编辑 黄宇

-

处理器

+关注

关注

68文章

20339浏览量

255346 -

RISC-V

+关注

关注

49文章

2954浏览量

53602

发布评论请先 登录

RISC-V创新中心联合达摩院玄铁发布无剑芯片设计平台定制版

大咖集结·即刻报名 | 2026 玄铁 RISC-V 生态大会主论坛议程正式发布!

RISC-V vs ARM:为什么工业与边缘计算仍然选择 ARM 架构?

新思科技ARC-V处理器驱动RISC-V市场无限机遇

重磅合作!Quintauris 联手 SiFive,加速 RISC-V 在嵌入式与 AI 领域落地

探索RISC-V在机器人领域的潜力

提高RISC-V在Drystone测试中得分的方法

全球首款RiSC-V企业级模拟平台,跃昉科技LeapEMU正式亮相

跃昉科技亮相2025 RISC-V软件生态研讨会

赛昉科技入驻RuyiSDK开发者社区,双平台协同推进RISC-V生态

RISC-V 手册

2025新思科技RISC-V科技日活动圆满结束

RISC-V 的平台思维和生态思维

DC-ROMA RISC-V AI PC 正式发布!

RISC-V公测平台发布 · UnixBench完整测试

RISC-V公测平台发布 · UnixBench完整测试

评论