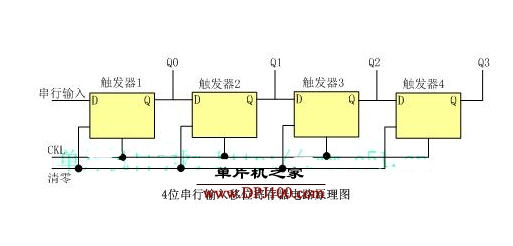

现代逻辑设计中,时序逻辑设计是核心,而寄存器又是时序逻辑的基础,下面将介绍几种常见的寄存器的Verilog设计代码供初学者进行学习理解。

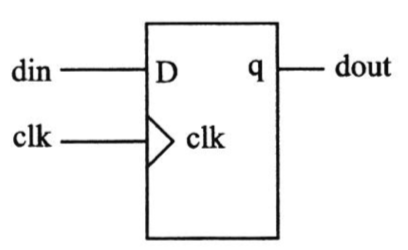

1、简单寄存器

基本寄存器

module dff(clk, din, dout)

input clk;

input din;

output dout;

reg dout;

always @ (posedge clk)begin

dout <= din;

end

endmodule

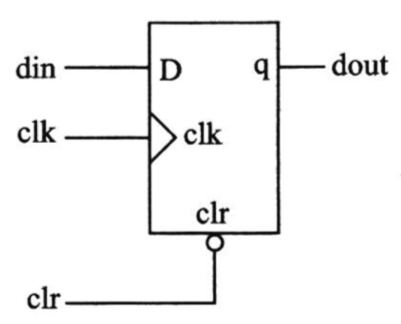

2、异步复位寄存器

异步复位寄存器

module dff(clk, rst_n, din, dout);

input clk;

input rst_n;

input din;

output dout;

reg dout;

always @ (posedge clk or negedge rst_n)begin

if(! rst_n)dout <= 1'b0;

else dout <= din;

end

endmodule

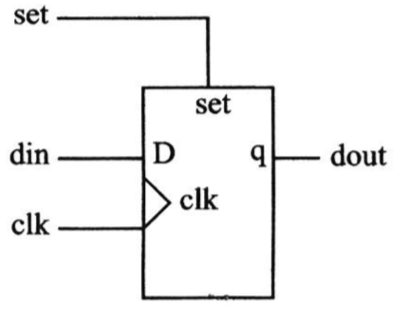

3、带异步置位的寄存器

异步置位寄存器

module dff(clk, set, din, dout);

input clk;

input din;

input set;

output dout;

reg dout;

always @ (posedge clk or posedge set)begin

if(set) dout <= 1'b1;

else dout <= din;

end

endmodule

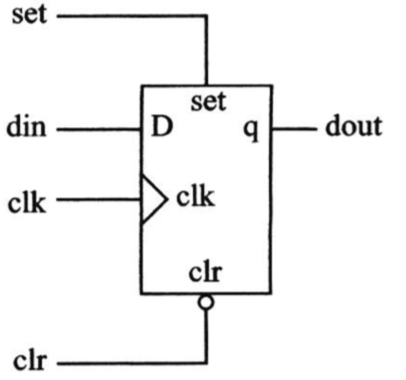

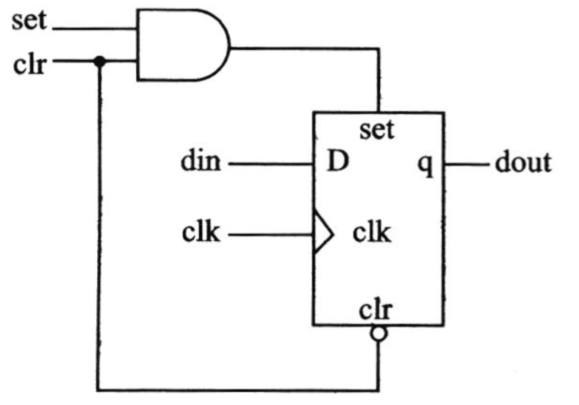

4、既带异步复位又带异步置位的寄存器

异步复位和置位寄存器

异步复位和置位寄存器(复位优先级高)

module dff(clk, rst_n, set, din, dout);

input clk;

input din;

input rst_n;

input set;

output dout;

reg dout;

always @ (posedge clk or negedge rst_n posedge set)begin

if(! rst_n) dout <= 1'b0;

else if(set) dout <= 1'b1;

else dout <= din;

end

endmodule

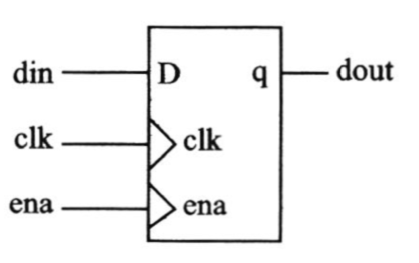

5、同步使能功能的寄存器

带同步使能的寄存器

module dff(clk, ena, din, dout);

input clk;

input din;

input ena;

output dout;

reg dout;

always @ (posedge clk) begin

if(ena) dout <= din;

end

endmodule

审核编辑:汤梓红

-

FPGA

+关注

关注

1655文章

22287浏览量

630317 -

寄存器

+关注

关注

31文章

5589浏览量

129070 -

Verilog

+关注

关注

30文章

1370浏览量

114144 -

时序逻辑

+关注

关注

0文章

39浏览量

9521 -

异步复位

+关注

关注

0文章

47浏览量

13643

发布评论请先 登录

Verilog中寄存器的定义

Verilog寄存器初始化没有复位引脚

移位寄存器怎么用_如何使用移位寄存器_移位寄存器的用途

寄存器变量

移位寄存器的原理

Verilog设计寄存器

Verilog设计寄存器

评论