来源:航天科工防御技术研究试验中心

摘要:

本文通过对典型案例的介绍,分析了键合工艺不当,以及器件封装因素对器件键合失效造成的影响。通过对键合工艺参数以及封装环境因素影响的分析,以及对各种失效模式总结,阐述了键合工艺不当及封装不良,造成键合本质失效的机理;并提出了控制有缺陷器件装机使用的措施。

引言

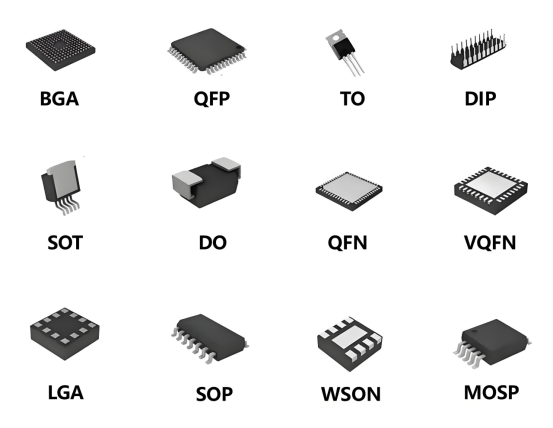

半导体封装内部芯片和外部管脚以及芯片之间的连接起着确立芯片和外部的电气连接的重要作用。半导体器件的封装中,多采用引线键合的方式实现内部芯片和外部管脚以及芯片之间的互联技术;引线键合以工艺实现简单、成本低廉、适用多种封装形式而在连接方式中占主导地位,目前所有封装管脚的90 %以上采用引线键合连接。键合是半导体器件生产过程中的关键工序,对半导体器件的产品合格率有很大影响。

在半导体器件的使用过程中,只要其中一个键合点损坏,将导致器件失效,轻者造成器件部分功能丧失,严重者则完全功能丧失。半导体器件的本质失效约有1/3~1/4是由引线键合引起的,故其对半导体器件长期使用的可靠性影响很大。

键合失效表现出来的失效模式主要为开路(包括阻抗增大),个别情况为短路。分析其本质失效的原因,有些是与器件键合工艺有关,有些与器件的封装有关,下面结合具体案例分析介绍。

1 键合工艺不良造成失效

键合焊接时,劈刀寿命达到期限,磨损过多,以及焊接参数(时间、压力)设置不当,都可能导致键合点在以后器件使用过程中产生失效。

1.1 键合压力大造成键合点失效

某型号检波二极管在随组合完成振动试验后,发现两只器件失效,失效模式均为开路。用体视镜对两只失效器件外观进行观察,未发现明显异常。启封器件,置于显微镜下观察,发现两只失效器件内部芯片键合点脱键。从开路键合点的形貌看,键合点金丝变形非常严重,边缘已经变得非常薄且有明显的开裂现象,说明键合焊接时,压力过大。键合压力大,键合点根部损伤严重,容易开路,另外,由于键合点非常薄且很容易出现“压裂”情况,受机械力的冲击,很容易出现开路失效。

1.2 键合压力小引发开路

键合时压力小,有可能造成键合点“未压牢”,键合丝与焊盘之间“融合”面积较小,受到机械冲击力作用,或者是温度应力作用(尤其是被塑封材料包封的键合点),键合点很容易与焊盘分离而开路失效。

某型号多丝发光二极管随整机进行试验时失效。对失效二极管外引脚进行测试,发现二极管开路失效。对器件进行X射线检查,键合丝未见明显断丝现象。对发光二极管外壳进行解剖,采用化学方法去除环氧树脂包封料,并对暴露出来的8个二极管的各个连接端进行测试,发现1#二极管开路。采用体视显微镜和扫描电镜进行观察,发现1#二极管内键合点与芯片焊盘脱键,与正常键合点比较,失效键合点变形较小。对器件内部所有键合丝进行非破坏键合拉力试验,1#二极管内键合点脱键,“零克力”失效,其它键合丝合格。使用扫描电镜对1#键合脱键位置进行观察,发现1#键合焊接面积较小。

1.3 键合丝塌丝引发短路失效

键合丝塌丝触及器件内部裸露的导体即造成短路失效。引起键合丝塌丝的原因很多,有些是因为键合丝的长短控制不当引起的,有些是因为键合丝走向不合适导致的,还有些是因为键合之后人为失误造成的。由于键合丝搭接处于一种不稳定状态,有时器件的失效现象很难复现,给失效分析工作带来困难,下面的案例充分说明了这一点。

某型号隔离放大器随整机进行振动试验时,发生失效。常温下,对失效器件进行综合电性能测试,结果为合格。之后,分别进行低温(-18 ℃,保温0.5 h后持续加电20 min)、高温(+60 ℃环境下,持续加电20 min)、常温(持续加电20 min) 测试,器件功能正常。又对器件进行5次温冲试验(-55 ℃,125 ℃,0.5 h保温,转换时间小于1 min)后,常温持续加电20分钟测试,高温(+85 ℃环境下,持续加电50 min)测试,以及恒定加速度试验(条件为:3 000 g、Y1方向,1 min)后,常温持续加电20 min测试,结果均为合格。

将失效件返生产厂家进行振动试验。首先进行两次不加电振动试验,X、Y、Z方向各5 min。在每个方向的振动完成后,对器件加电510 min进行测试,结果为合格。第二次振动试验功率谱密度(PSD)比第一次增加50 %,X、Y、Z方向各5 min。同样在每个方向的振动完成后,对器件加电510 min进行测试,结果为合格。之后再对失效样品按第二次振动条件进行加电振动试验。首先进行Z向(器件最长边方向)振动,刚刚起振,样品的正负隔离电压输出异常。停止振动并断电,重新加电后测试也正常。以上试验结果表明,振动试验可以激励器件故障复现。将样品从振动台上取下,再次进行加电测试,样品的正负隔离电压不正常。说明器件故障现象已处于稳定状态。

接下来对器件进行X射线检查,发现器件内部管脚31键合金丝与附近独石电容端头间无明显间隙。开封器件,通过显微镜观察发现,器件内部+15 V电源(Pin 31)键合金丝与附近独石电容一端头搭接。可以看出,该键合丝明显过长。

隔离放大器失效机理为:器件内部管脚31(+15 V)键合金丝与附近独石电容一端头搭接,造成+15 V电源跳过限流电阻,直接加在内部振荡器芯片的正电源,导致器件内部振荡器不能正常供电,产品功耗增大,隔离电压降低,最终导致器件无输出。

以上介绍的是键合丝塌丝触及电容端头造成失效案例;有些案例是塌丝触及芯片边缘引起失效。

2 封装原因引起器件内部键合失效

因封装原因引发器件键合失效的情况包括:器件腔体内水汽含量高并有腐蚀性元素,造成键合点腐蚀开路失效,玻璃熔封DIP器件玻璃熔封料挤压外键合点开路失效,塑封器件分层造成内键合点脱键失效等。下面分别给予介绍:

2.1 内部键合点腐蚀开路失效

某型号三极管随组合进行试验过程中出现失效。对失效器件外部进行观察,发现:器件壳体表面存在熏黑迹象;底座管脚间蓝色橡胶垫局部存在过热、熔融现象。

对失效器件管脚间V-I特性进行测试,结果为:E、B及E、C极间正、反向均呈开路,B、C极间呈二极管特性。

对失效器件进行气密封检测,发现管壳与底座焊接区域存在微泄露,细检不合格。对失效器件进行粒子碰撞噪声检测,结果为合格。

启封器件,置于显微镜下观察,发现:发射极E极外合区及键合丝表面严重腐蚀,存在一层白色絮状腐蚀产物;E极外键合区附近键合丝熔断;底座及芯片表面靠近E极键合区附近区域存在变色发黑现象;B极键合丝未发现明显异常。

用扫描电镜观察,发现E极外键合区及键合丝表面腐蚀严重,存在一层白色絮状、似松球状腐蚀产物;E极外键合区附近键合丝已熔断。对E极外键合区附近进行能谱分析,发现除含有Al、Si、Fe、Ni等主元素外,还含有O、P等元素;对键合丝表面腐蚀物进行能谱分析,发现除有Al、Si、Fe、Ni等元素外,还有O、P、Cl等元素;对B极外键合区进行能谱分析,只有Ni元素。因此得出:失效器件由于密封不合格,导致使用过程中水汽进入器件内部,同时E极键合区残存P等腐蚀元素,使键合区及键合丝外表面形成腐蚀产物堆积,在电应力的作用下,进一步过流烧毁、熔断。

2.2 玻璃熔封料挤压外键合点开路失效

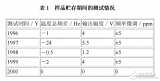

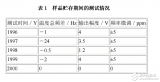

某型号玻璃熔封DIP器件在随整机进行温度冲击试验时,发现输出异常。对器件进行X射线检查,发现管脚11~14一侧玻璃熔封料较多。

对器件管脚间V-I特性进行测试,发现1Cext端口(管脚14)与地间开路,而正常器件则呈低阻特性。

启封器件,置于显微镜下观察,芯片表面未见明显的击穿烧毁及其它异常现象,但管脚1114一侧玻璃熔封料较多,致使管脚1114外键合焊盘已完全被玻璃熔封料覆盖。器件封盖与基座分开后,测试管脚14与焊盘间电连接无异常,管脚14焊盘上键合丝下面有一明显玻璃熔封料凸起部位。封盖上残留的玻璃熔封料粘连部分与管脚35、管脚1114相连键合丝。管脚14内键合丝出现两个断点,一个断点位于外键合颈缩部位,另一断点位于键合丝中部,芯片一侧仍残留一段管脚14的内键合丝。用万用表测试该段键合丝与地间电阻,呈低电阻特性。

用扫描电镜及EDX对芯片一侧1Cext端口残留键合丝进行形貌观察与检测,发现断口为斜断口,断裂部位有明显的颈缩现象,具有明显的受力塑性断裂特征。EDX检测发现含有Al、Si、C、O等元素,未发现腐蚀性元素。此处断裂为开封过程造成的。用扫描电镜及EDX对封盖上残留的1Cext端口外键合颈缩断裂部位进行形貌观察与检测,并与1Q端口(管脚13)外键合颈缩断裂部位进行比较,发现1Cext端口外键合断裂部位存在玻璃熔封料,而1Q端口外键合颈缩断裂部位呈明显的受力断裂特征,能谱分析显示主要为Al元素。因此得出:器件失效是由于1Cext端口在管脚键合点颈缩部位开路造成的。导致该部位开路的原因为:封盖时1Cext端口管脚键合根部下面渗入了玻璃熔封料,对键合丝形成了“翘起”作用,并造成应力集中部位-外键合颈缩处-损伤。器件装机使用后,在各种环境应力试验过程中,受到热应力和机械应力的作用,造成该部位损伤程度进一步恶化,最终开路失效。

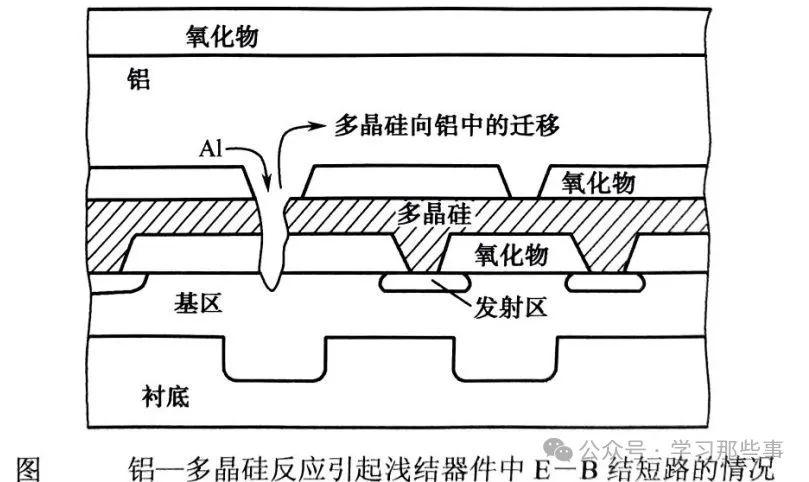

2.3 塑封器件分层造成内键合点脱键失效

塑封器件膜塑材料与芯片的热膨胀系数不同,如果塑封包封料与芯片间存在分层,温度变化将在塑封材料与芯片表面产生热机械剪切应力,芯片中心处的应力可以忽略,向外角或边缘延伸时应力成指数级增加;由于键合部位一般位于芯片边缘,很容易产生键合点脱键失效。

某型号集成电路在随整机进行试验时出现失效。对失效器件进行扫描超声显微镜检查,芯片表面及部分外键合部位呈现分层现象。

采用化学方法启封失效器件,置于显微镜下观察,发现器件内部部分与芯片基座相连的内键合丝已经脱落;多根内键合丝在芯片上的键合发生移位,说明键合与焊盘已经脱键。器件封装后,金丝球被塑封材料包裹,而塑封包封料与芯片间存在分层,芯片与塑封材料热涨系数差别较大,温度变化(如温度循环试验)将在塑封材料与芯片表面产生热机械剪切应力,加之键合点部位应力集中,造成部分键合点脱键失效。

3 预防措施

对于上述因制作工艺不当引起的键合失效,除了采取加强工艺控制的措施外,还可以通过相关的DPA试验项目或者筛选试验项目予以发现并剔除。下面详细介绍。

对于因键合压力大或压力小造成的键合缺陷,DPA试验中的内部目检可以发现键合点的异常形貌,DPA键合拉力试验也可以检测出键合力偏小(甚至“零克力”)的键合点。对于键合丝偏移、塌丝等缺陷,通过DPA试验中X射线检查(对Au丝),以及内部目检可以及早发现。对于键合点腐蚀缺陷,DPA试验中气密性检测可以发现器件密封问题,内部气体成份分析可以检测出器件内部水汽含量是否超标,内部目检可以及早发现腐蚀缺陷。恒定加速度的筛选试验也可以一定程度地暴露及剔除上述缺陷。

通过DPA试验中X射线检查,以及内部目检可以及早发现玻璃熔封料挤压外键合点缺陷。通过DPA试验中超声扫描检查,可以及早发现塑封器件分层缺陷。另外,温度循环试验也可以一定程度地暴露及剔除上述缺陷。

4 结束语

前面通过典型案例介绍,分析了键合工艺不当,以及器件封装因素对器件键合本质失效造成的影响。对以上分析进行总结,得出键合工艺不当,对元器件失效产生的影响主要体现在以下几方面:键合压力大造成键合点损伤,导致键合开路失效。键合时压力小,键合丝与焊盘之间“融合”面积较小,导致键合开路失效。键合丝的长短控制不当,或者走向不合适,导致短路失效。因封装原因引发器件键合失效的情况包括:空封器件腔体内气氛不良,造成键合点腐蚀开路失效,陶瓷玻璃熔封料挤压外键合点开路失效,以及塑封器件分层造成内键合点开路失效等。通过相关的DPA试验项目或者筛选试验项目可以及早暴露缺陷并予以剔除。

审核编辑:汤梓红

-

芯片

+关注

关注

463文章

54441浏览量

469421 -

半导体

+关注

关注

339文章

31248浏览量

266601 -

封装

+关注

关注

128文章

9333浏览量

149048 -

键合

+关注

关注

0文章

107浏览量

8305

原文标题:半导体器件键合失效模式及机理分析

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

元器件失效了怎么分析? 如何找到失效原因?

常见的电子元器件的失效机理及其分析

半导体集成电路键合强度原理、试验程序、试验条件、失效判据分享!

半导体“金(Au)丝引线键合”失效机理分析、预防及改善的详解;

半导体器件键合失效模式及机理分析

半导体器件键合失效模式及机理分析

评论