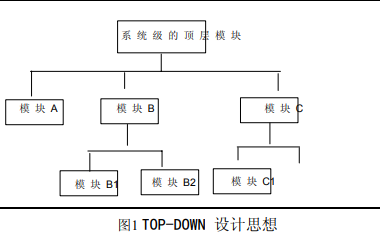

高质量6要素

高质量的verilog代码至少需要包含以下几个要素:可读性、功能、性能、标准化、稳定性、可定位。

标准化:iterlaken MAC PCIE 这些模块的设计必须要符合协议标准,能够与其他厂商的产品进行正常对接。

可读性:代码是容易阅读,是否容易理解原理

功能:功能是否正确,功能点是否全面,是否灵活可配置。

性能:读写、传输速率是否达标

稳定性:跨时钟等是否处理细致,异常情况代码是否能够保持稳定,是否能够自恢复,状态机是否会卡住。

可定位:定位手段是否添加全面、遇到故障,是否能够快速定位。

1、可读性

代码是否容易阅读理解,需要注意代码格式、关键信号命令、尽量多添加注释。

代码格式:代码编写需要采用普遍的格式、如空格的插入、if else的位置放置、特别是复杂的逻辑判断,该断行的需要断行,该添加括号的地方添加括号。

信号命名:信号命名需要注意:如请求信号以req命令,响应信号ack,流控信号fc,信号命令需要通俗易懂,采用常见的缩写。

注释清晰:一定要多写注释,很多代码时间长了,自己都看不明白了,就算能看明白,也需要花费不少时间

2、功能达标

代码功能点是否全面。

各个功能是否能够正常实现。

各功能是否灵活可配置,如是否具有使能开关

3、性能达标

模块性能是否达标。设计是否已考虑各项性能指标,如数据通路常见的指标为BPS和PPS。

极限(最佳速率和最差速率)和正常场景下性能是否达标。

特殊包长场景是否已考虑。是否能够及时处理突发数据。

4、标准化

模块设计是否符合标准协议,如IEEE802.3 MAC 模块设计是否符合标准,PCIE 是否能够与其他厂商的PCIE进行对接传输数据,且与主机相关的各项能力结构能够与主机正常交互。如interlaken接口是否能够与FPGA的interlaken进行正常对接。

5、稳定性

代码的稳定性需要关注常见的spyglass lint cdc、跨时钟信号、代码是否能够自恢复。

常见spyglass lint检查:信号位宽是否匹配,技术是否会溢出、是否产生了latch等等

跨时钟:跨时钟的信号是否都进行了同步处理、单bit、多bit信号是否正确同步。电平单bit、多bit数据、单bit脉冲、复位信号的同步方式各不相同,是否都正确同步了。信号同步的max_delay 延时是否符合要求。

自恢复:异常情况下,模块是否能够自行恢复,当异常情况消失后,模块是否够能够正常工作。异常情况有:

1)不符合规定的信号输入:输入信号eop_in/sop_in/vld_in/error_in的有效状态有一定的规律,不符合规律的输入信号是否会导致模块无法正常处理后面正确的输入数据。

2)状态机没有响应:状态机跳转信号没有响应,是否会导致状态机卡死,无法跳转到IDLE状态。

3)关键信号异常跳变:偶发性强电磁反应导致的信号跳变是否会导致模块一直无法正常工作。

6、可定位

常见的定位手段是否添加全面,比如:各类统计计数、关键信号状态是否可读、中断信号添加是否全面。

统计计数:模块进入数据包多少,输出数据包多少。完成了多少次xx操作。

关键信号可读:状态机当前状态要求可读,关键信号要求可读

中断:fifo和ram的写溢出、空读、ECC、parity要求接入中断。

教你如何书写高质量的Verilog代码?

-

Verilog

+关注

关注

31文章

1374浏览量

114734 -

时钟

+关注

关注

11文章

2000浏览量

135284 -

编程

+关注

关注

90文章

3724浏览量

97458 -

中断

+关注

关注

5文章

920浏览量

43885 -

代码

+关注

关注

30文章

4977浏览量

74417

原文标题:高质量的verilog代码是什么样的

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Verilog HDL入门教程

Verilog HDL入门教程

华为Verilog HDL入门教程的PDF电子书免费下载

分享一些优秀的verilog代码 高质量verilog代码的六要素

分享一些优秀的verilog代码 高质量verilog代码的六要素

评论