电子发烧友网报道(文/吴子鹏)温度控制在半导体制造领域的应用非常广泛。比如,在单晶炉中,温度变化会影响到晶体的生长;在芯片测试系统里,温度在一定范围的变化,可以看到芯片在工作温度范围里,在内部热应力、漏电电流和电气性能等关键性能方面的变化;在封装环节,出色的温度控制能够应对晶圆和PCB板的翘曲问题。这样的案例不胜枚举。

近日,在ERS媒体见面会上,该公司分享了他们为半导体行业提供的创新的温度测试解决方案,包括用于晶圆测试的温度卡盘、热拆键合/翘曲矫正一体机,以及独立的翘曲矫正设备等。

用于晶圆测试的温度卡盘

探针台作为晶圆测试的关键设备,将测试机输出激励信号进行互通与信号反馈,最终完成测试数据的获取采集。在晶圆测试的探针台里,温度卡盘的作用是提供测试所需要的温度环境,比如晶圆测试可能会需要300℃的温度环境,或者500℃的温度环境。

在极端的温度下,如果温度卡盘本身的质量不过关,那么就可能导致出现严重的热漂移问题,影响探针和Pad点的对准。ERS自1970年开始涉足晶圆针测温度控制技术研究,深知温度对设备的测试结果有着重大影响,致力于推出温度卡盘系统,以满足市场对温度测试的需要。公司副总裁兼ERS中国总经理周翔指出,“随着科技的发展,终端电子产品的种类越来越丰富,对芯片测试的需求也就越多,其中最重要的参数便是温度,比如广泛应用在汽车内的芯片,就必须要保证在极寒天气正常运作。”

媒体会上,ERS向参会媒体展示了该公司旗舰温度卡盘系统——AC3 Fusion。

AC3 Fusion,图源:ERS

AC3 Fusion是AC3系列升级迭代的产品,不仅系统本身精进了能耗控制技术,也能够更好地赋能芯片产业以及下游终端产业响应全球主要国家和地区推行的“碳中和”目标。AC3 Fusion主要有以下几点优势:

• 温度范围广:-60℃- +400℃

• 使用CDA空气作为制冷剂

• 无与伦比的可靠性和极长的使用寿命

• 近乎于零的维护要求

• 升温速度极快

• -40℃ - +150℃范围内均匀性稳定在±0.5℃

• fA级的超低噪声指标性能

• 适用于各类手动、半自动、全自动探针台

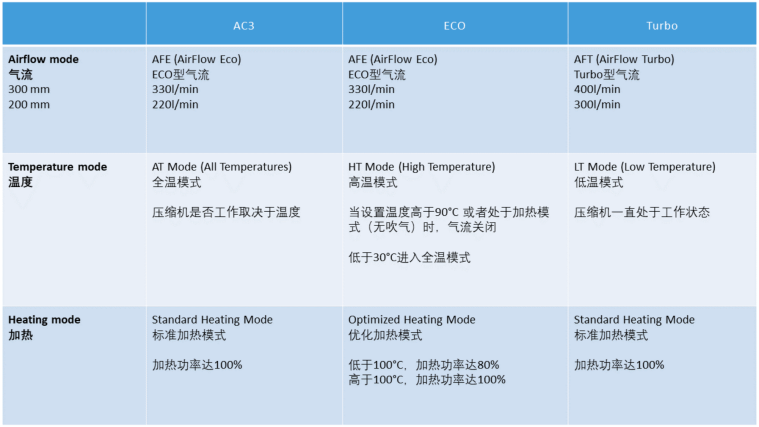

除了上述性能有优势以外,AC3 Fusion还提供了三种工作模式,包括AC3模式、Turbo模式和ECO模式。其中,AC3模式沿用传统AC3温度卡盘系统;Turbo模式与AC3相比,转换时间提高40%,特别适用于零下40度及以下的低温测试环境;ECO模式节约能耗最高可达65%,是理想的室温或高温晶圆针测解决方案。

图源:ERS electronic

除了主打产品温度卡盘,ERS也提供很多定制卡盘,比如高压大电流卡盘、温度高均匀性卡盘、强真空卡盘、超低噪声卡盘等,以满足市场上的差异化需求。

ERS赋能先进封装发展

在半导体领域,目前先进封装概念大热,主要应用面向高性能计算、高端服务器等领域,拥有倒装芯片(FlipChip,FC)结构封装、晶圆级封装(WaferLevelPackage,WLP)、2.5D封装、3D封装等多种形式。知名半导体分析机构Yole预计,到2025年先进封装的市场规模将占到整个封装市场的49.4%,成为后续封装市场的主要增长引擎。

面向先进封装领域,本次媒体会上,ERS介绍了该公司的扇出型晶圆级/面板级热拆键合/翘曲矫正机。

周翔称,晶粒偏移(Die Shift)和翘曲(Warpage)是目前扇出型封装面临的主要问题。ERS公司提供的全自动热拆键合/翘曲矫正一体机ADM330,全自动翘曲矫正机WAT330,以及全自动面板级热拆键合机APDM650等设备,能够帮助行业更好地应对这些难题。

ADM330的主要性能优势有:

• 支持300/330mm晶圆

• 集成晶圆翘曲控制系统

• 翘曲测量和激光标记流程化

• 处理过程中对晶圆仅施加极小的压力

• 温度范围:20℃ - 240℃

• 独特的温度卡盘设计使其兼具强真空性能

• 符合GEM300标准,适用于工业4.0

WAT330的主要性能优势有:

• 可处理化合物晶圆规格:300mm

• 搭载ERS三温滑动专利技术

• 矫正晶圆翘曲能力:±5mm

• 输出翘曲典型值:<1mm

• 全程检测并矫正翘曲

APDM650的主要性能优势有:

• 最大可处理的面板规格:650x650mm

• 温度均匀性可稳定在 ±3℃ @200℃

• 自动脱粘

• 搭载三温滑动专利技术

• 根据不同的EFEM配置实现定制化

• 全程安全操作

另外,慕尼黑当地时间5月31日,ERS宣布开发了一种史无前例的晶圆翘曲测量和分析设备——Wave3000。得益于其先进的光学扫描测量方法,Wave3000可以准确地测量晶圆在特定处理位置的变形,并提供全面精准的翘曲分析,这对于确保先进封装设备的质量至关重要。

持续看好中国市场

根据周翔的介绍,ERS自2018年进入中国市场,发展非常迅速。2022年,该公司中国区营收已经占到总营收的40%,有着惊人的增速。并且,后续ERS将加大对中国市场的投入。

慕尼黑当地时间6月29日,ERS宣布,公司与上海晶毅电子科技有限公司联手在上海成立ERS中国实验室。这一合作建立的实验室将为双方提供一个为客户展示产品demo、提供现场产品测试的平台。通过技术交流和资源共享,更准确地了解客户的需求,精准定位,从而加速产品开发和市场推广速度。

图源:ERS

周翔表示,“共同建立实验室,是与晶毅合作以来一个重要的里程碑。通过共享技术和资源,我们将能够更敏锐地了解市场动态以及客户需求,从而为客户提供更及时更优质的解决方案。”

发布评论请先 登录

ERS:专注晶圆温度针测和扇出型先进封装,继续深耕中国市场

ERS:专注晶圆温度针测和扇出型先进封装,继续深耕中国市场

评论