一

HPM6200 系列 PLA 整体结构

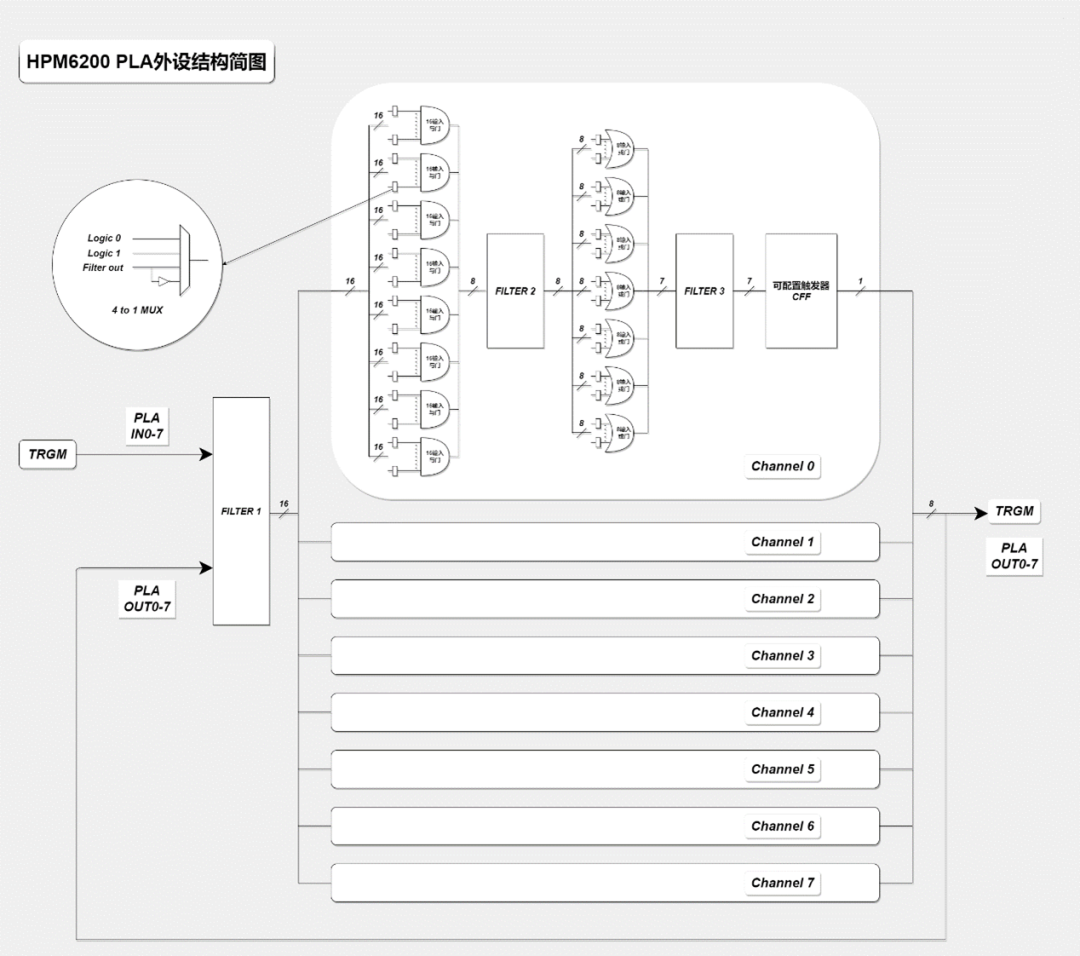

HPM6200 系列的 UM 中带有 PLA 的结构简图。为了方便大家把握整体结构,我也绘制了一个稍微更详细的结构图,将 PLA 外设中的大部分元素都展示出来,并给出了单个通道内的具体结构。

从总体来看,PLA 外设拥有 8 输入、8 反馈、8 输出,其中 8 输入、8 反馈是内部的 8 个通道共享,8 输出则是每个通道使用一个。输入、输出均连接到 TRGM 外设,再通过 TRGM 连接到定时器、编码器、外部引脚等地方。需要注意的是,PLA 的 8 输入、8 输出并非全部都能引出至外部引脚中。每个 PLA 外设都连接到一个指定的 TRGM 外设,而每个 TRGM 外设最多仅可连接 12 个外部引脚,同时 TRGM 还可能有其他信号需要接到外部引脚中,如果想要使用更多外部引脚,则还需要使用 TRGM 间连接等方式。因此,在设计 PLA 程序时需要尽可能提前考虑 I/O 安排的问题。

每个 PLA 外设由一个滤波器 FILTER1 和 8 个通道组成,FILTER1 对输入和反馈信号进行滤波后,宽度为 16bit 的信号将同时输入到 8 个通道之中(这个扇出也挺惊人的)。每个通道的输出宽度均只有 1bit,8 个通道合并组成的 8bit 就是 PLA 外设的输出。下面我们将分别对 PLA 滤波器和单个通道进行介绍。

二

PLA 外设中的滤波器

和我们之前介绍过的 PLA 结构相比,HPM6200 系列的 PLA 最大的特点就是多出了一些滤波器。每个 PLA 外设都有一个 FILTER1 滤波器,8 个通道中每个通道还各有一个 FILTER2 滤波器和 FILTER3 滤波器。目前,文档中并没有向我们介绍这些滤波器的设计目的,不过我们也不难从其功能中窥探一二。无论是 FILTER 1, 2 还是 3,他们的功能基本一致:将输入信号经过同步、边沿检测、软件注入和扩展滤波四个环节后输出。

1. 同步

文档中并没有告诉我们同步功能的具体实现方式,不过在这一段描述里面,我们可以大致猜测出很多信息:

FILTER_SYNC_LEVEL 位选择同步器级数,清 0 时为 2 级同步,置 1 时为 3 级同步。根据该位的设置,同步器会将信号延时 2 个或者 3 个时钟周期。

2级、3 级同步可选,听上去就与跨时钟域处理中的同步器很像。比较了解 FPGA 或 IC 设计的朋友知道,同步器是减少亚稳态对逻辑电路影响的一个常用措施,PLA 外设可以接受外部输入的信号,自然也算是一种“跨时钟域”传递信号的过程。同时,增加同步功能还有利于避免出现组合逻辑电路的竞争-冒险,毕竟 FPGA 和 CPLD 开发时有 EDA (尽管 EDA 也不完全可靠)工具帮忙看着,我们在和 PLA 玩耍的时候就没那么好的条件了。因此我们不妨猜测同步功能实际上就是使用 2/3 级触发器构成的同步器。

2. 边沿检测

这一功能很好理解,将边沿转为脉冲,此处不再赘述。

3. 软件注入

这一功能也很好理解:强制将输出设置为高电平或低电平。实际上各逻辑门前的四选一 MUX 也能实现类似的功能,这一功能更多是为可配置触发器 CFF 或者是降低配置复杂度而生的。

4. 扩展滤波

扩展滤波要比上面三个功能复杂得多,文档也并没有讲得特别清楚,下面我将结合实际例子,分别介绍它的四个滤波类型效果。

在开始之前,我们首先要了解 PLA 外设的时钟。PLA 外设挂载在 AHB/APB 总线下,因此也受在 AHB/APB 时钟(默认 200MHz)驱动。在上文提到的同步器同步周期数量中,2/3 级同步就是指的 AHB/APB 时钟的 2/3 个周期。扩展滤波功能最高支持 65535 周期的扩展,对应的 AHB/APB 时钟周期数也为 65535 周期,单个周期的时间为 5ns,这在我们后续的计算中会常常用到。对于 hpm_sdk v1.2 以前的版本,周期数配置部分存在一个小 bug,需在代码中将计算出来的周期数乘二。

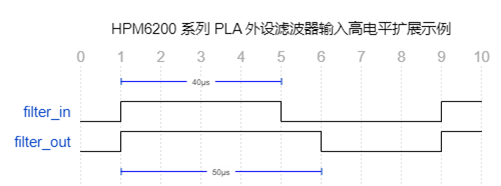

(1)输入高电平扩展

这一个模式相对比较好理解:扩展高电平的长度,也就是在输入信号变为低电平以后,输出信号仍会保持高电平,时间为设定的周期数。下图给出了一个例子。输入信号是周期为 80μs,占空比 50% 的 PWM 信号,滤波器设置为输入高电平拓展,周期数为 2000,输出信号较输入信号延迟10μs 变为低电平。

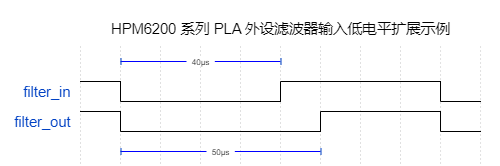

(2)输入低电平扩展

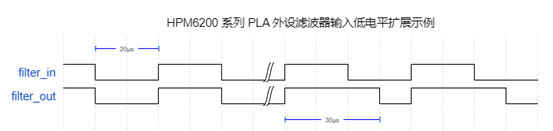

这一个模式正好与上一个模式相反。下图输入信号仍是周期为 80μs,占空比 50% 的 PWM 信号,滤波器设置为输入低电平拓展,周期数为 2000,输出信号较输入信号延迟 10μs 变为高电平。

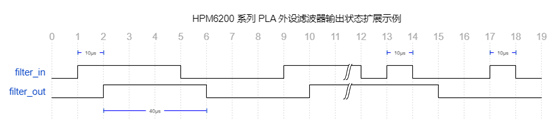

(3)输出状态扩展

这一个模式可以看作是以上两种模式的加和:既延长低电平时间,也延长高电平时间。输入信号发生变化时,输出信号将先在设定的周期数内维持现有状态,结束后跟随输入信号变化。这一模式可以起到两个效果,一是将脉冲宽度小于设定周期数的脉冲全部过滤掉,二是将脉冲宽度大于设定周期数的脉冲延迟设定周期后输出。

下图前半段输入信号是一个脉冲宽度为 40μs 的 PWM 波,输出信号对比输入信号延迟了 10μs;在后半段将输入信号和输出信号对比,则可以发现所有宽度不大于 10μs 的波形都被过滤掉了。

(4)输入跳变扩展

这一模式下输出信号跟随输入信号变化,但是当输出信号发生过跳变以后,在设定周期数的时间内,输出信号将保持不变,随后输出信号继续跟随输入信号的变化。

下图中前半段滤波器设置的周期数为 2000,对应 10μs 的时间,因此对于半周期 20μs 的 PWM 信号不会产生任何影响;后半段滤波器设置的周期数为 6000,对应 30μs 时间,因此在输入信号从高电平跳变为低电平以后,输出信号还会继续保持高电平直至 30μs 结束。

三

PLA 外设通道结构

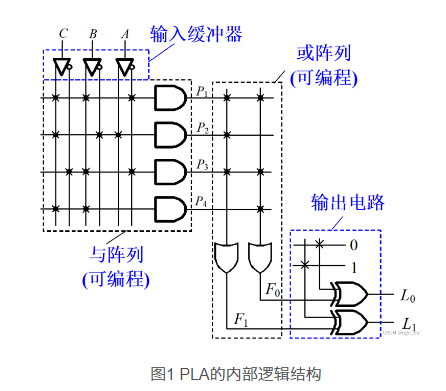

1. 与- 或阵列

每个通道的 16 信号输入会分别接入到 8 个 16 输入与门中,对单个输出信号最高支持 8 个最小项相加(8 个与门),并可生成 7 个输出信号(7 个或门)。每个逻辑门的输入端都有一个四选一 MUX,可选逻辑 1、逻辑 0、原信号和原信号取反四种输入。

2. 可配置触发器

CFF 可被配置为 D 触发器、双边沿 D 触发器、JK 触发器、T 触发器、锁存器、运算器和直接输出信号这几种功能。CFF 的输出即为其所在通道的输出,输出信号宽度 1bit,输入信号宽度则为 7bit,CFF 配置为各类触发器时,触发器的使能、置位、同步/异步复位、时钟等信号均来自于 7bit 宽度的输入信号,具体的分配表可见 UM 文档。除了使用输入信号以外,CFF 还可以使用 AHB/APB 的时钟。

四

如何使用 HPM_SDK 中的PLA驱动

在之前介绍的各种含有 PLA 的芯片基本都会配置对应的 EDA 工具,用户一般可以使用 verilog 编程或者图形化界面编程,由 EDA 工具生成比特流。比如 PSoC 芯片用户可以使用图形化界面编辑状态机的状态转移条件,再由软件完成后端的处理。HPM6200 的 PLA 则没有使用这种开发方式,而是将所有的可配置项均以寄存器的方式暴露给 CPU,CPU 设置好对应的寄存器以后,PLA 即可开始工作。

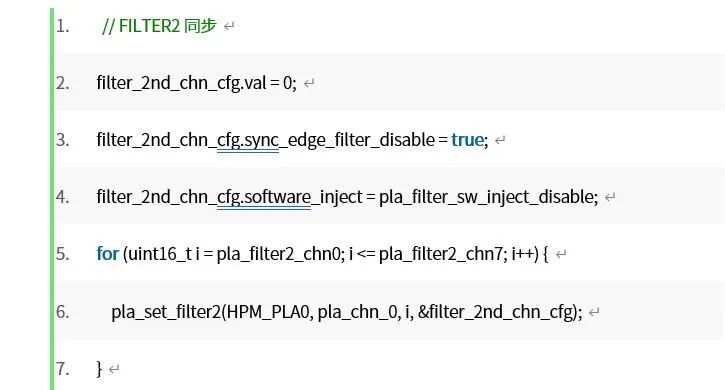

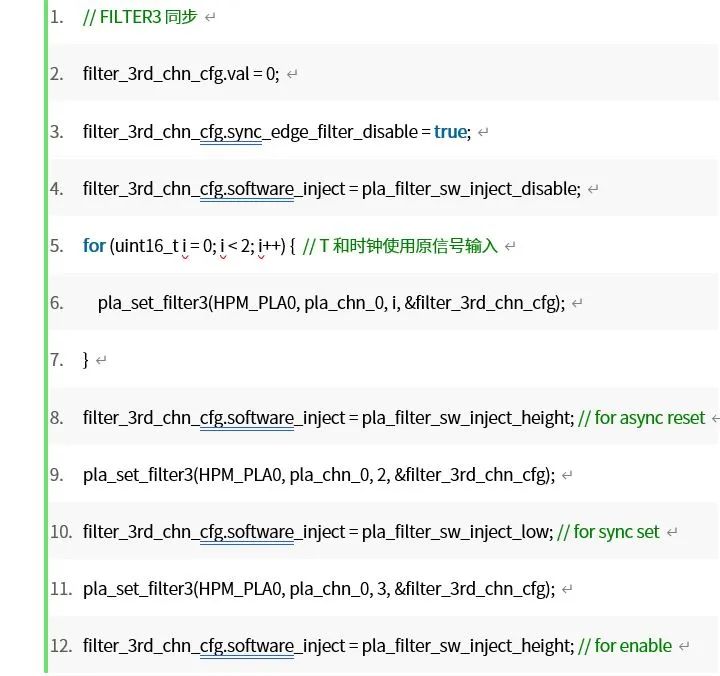

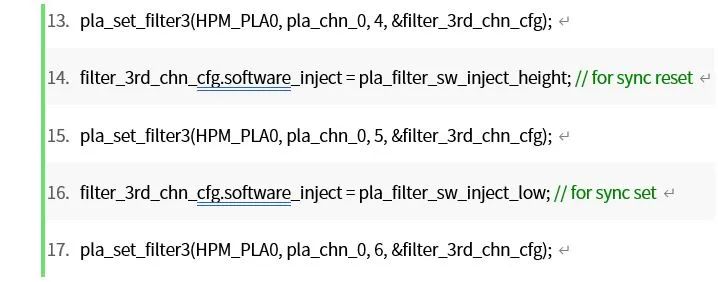

1. FILTER

滤波器的可配置项非常多,包括是否同步、是否启用边沿检测、是否软件注入等一系列内容,不过最关键的其实是准确把握配置的数量。PLA 中有 1 个 FILTER1、8 个 FILTER2 和 8 个 FILTER3,FILTER1/2/3 中分别有 16/8/7 个信号,每一个信号都可以独立设置上述介绍过的所有滤波功能,也就是共有 136 个信号,很容易错配、漏配。因此,除了所有通道共用的 FILTER1 单独配置以外,FILTER2/3 建议和它们所在的通道一同配置,避免混淆的同时,如果部分通道没有使用,也就不需要对它们的 FILTER2/3 进行配置了。

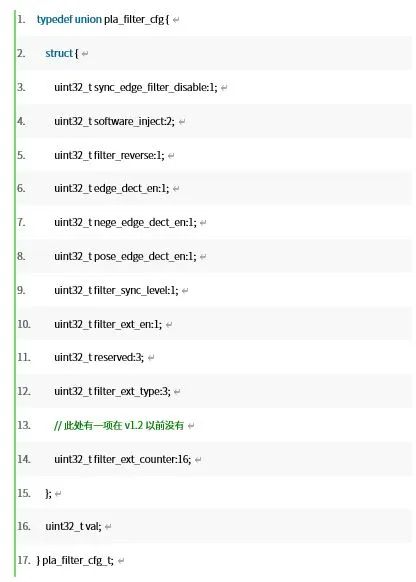

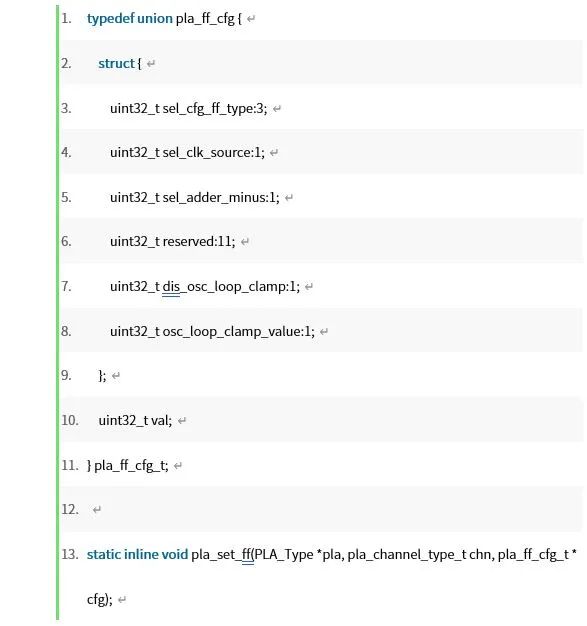

滤波器的配置结构体是一个位域结构体,使用四个字节保存一个信号的滤波选项,其每个成员的功能结合手册也非常容易理解,注意,配置结构体里面并没有任何关于该配置位于哪个通道、哪个滤波器等位置的信息。结构体填充完成以后,则需要使用以下几个函数完成设置:

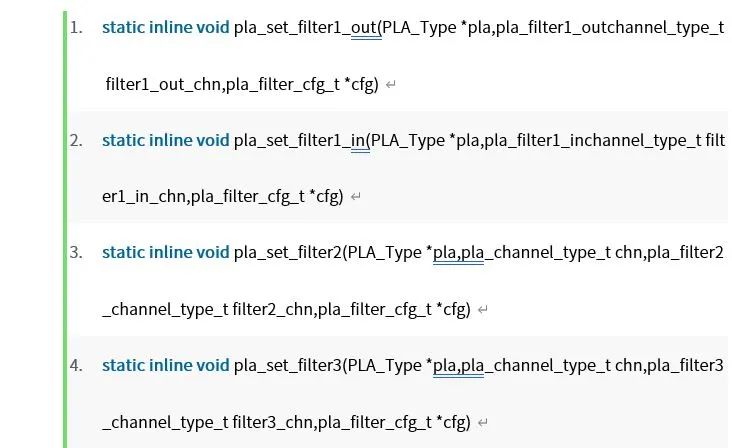

这里面实际上有不少容易踩坑的地方。例如 FILTER2/3 都只有一个函数,而 FILTER1 有 in/out 两个函数。实际上 in/out 两个函数分别负责 FILTER1 16 个信号里面前 8 个和后 8 个信号的配置,原因大概是前 8 个是 PLA 的输入信号,后 8 个则是 PLA 的输出信号反馈回来的。

刚刚提到的滤波器配置结构体里面并没有关于位置的信息,因此这些信息要以参数的形式提供给设置函数。以在通道 3 的 FILTER2 为例,使用 pla_set_filter2() 时不仅要写明通道 3,还要指出是 FILTER2 8 个信号中的具体哪一个信号。而 SDK 中通道参数和信号参数分别叫 chn 和 filter2_chn,使用时一定要注意区分两者之间的差别。

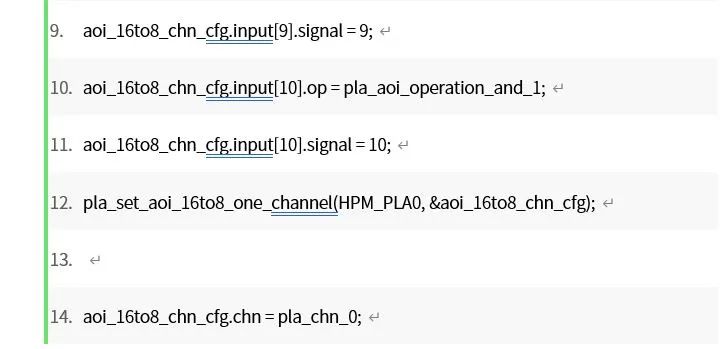

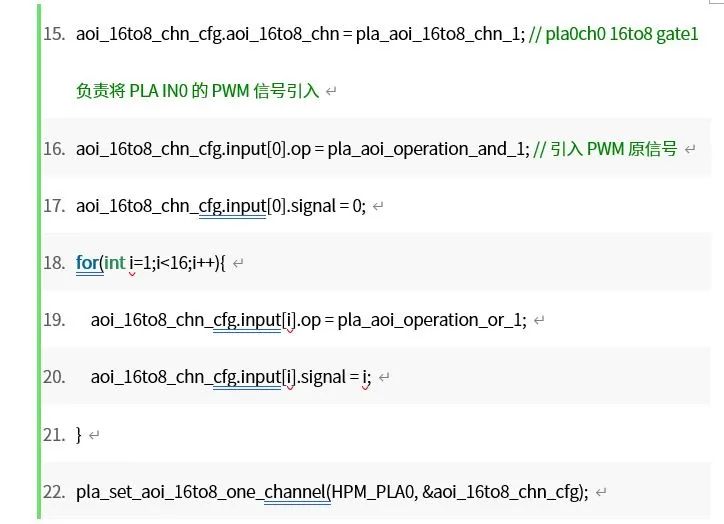

2. 与门

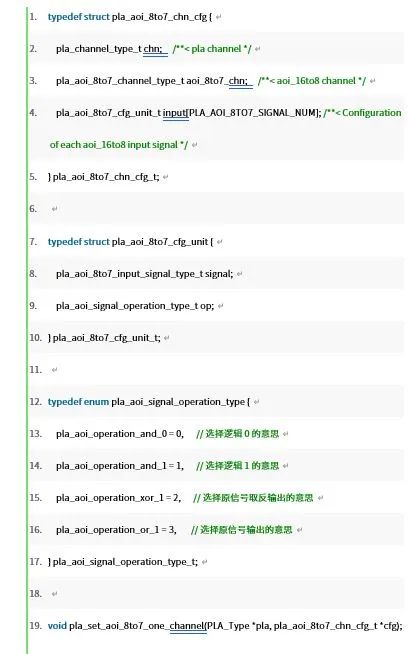

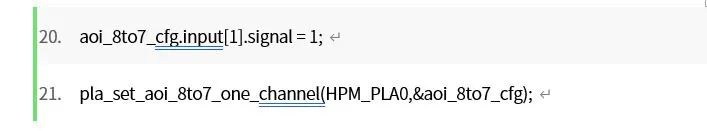

16 输入与门本身只有一个可配置的内容:各输入信号的 MUX 选项。不过同样需要注意数量和位置的问题。8 个通道里面,每个通道有 8 个与门,每个与门又有 16 个 MUX。当然,除了没有使用的通道无需配置以外,部分没有使用的与门也可以不进行设置,默认状态下与门将输出低电平。

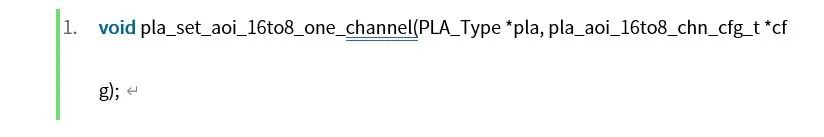

与门的配置结构体是 pla_aoi_16to8_chn_cfg,可以对一个与门进行配置,记得不要被它名字里面那个 chn 给欺骗了。结构体里面有 pla channel 和 aoi_16to8 channel 两个“通道”成员,一个指的是 PLA 的通道,另一个则是指 8 个与门的编号。个人认为这样设计其实容易混淆,可以在命名方面更加有区分度一些。

一个与门中有 16 个 MUX,因此 pla_aoi_16to8_chn_cfg 里面有长度为 16 的 MUX 配置结构体 pla_aoi_16to8_cfg_unit_t 数组。MUX 配置结构体的 signal 成员是信号的编号;op 成员的四个选项对应 MUX 的四个选项,对应关系在上面的代码注释中给出。

最后我们需要使用以下函数对一个与门进行配置。

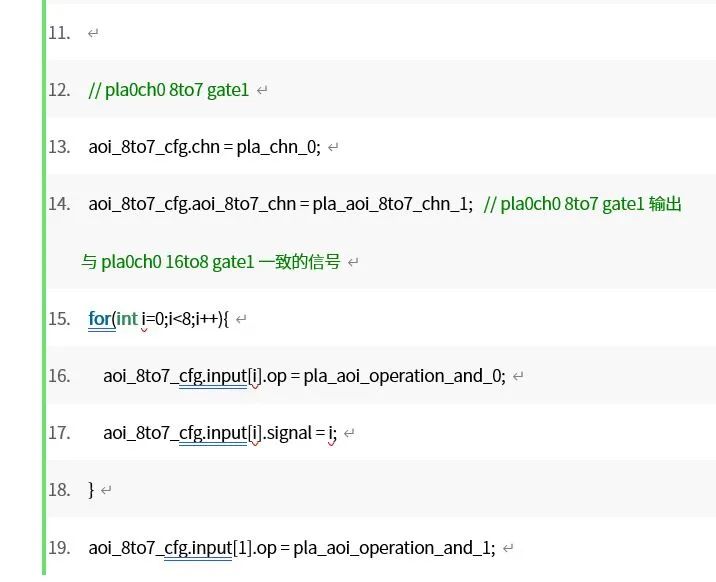

3. 或门

或门的代码和注意事项和与门大同小异,数量上一个通道有 7 个或门,每个或门有 8 个 MUX,比与门会少不少,其余部分基本一致,参照使用即可。

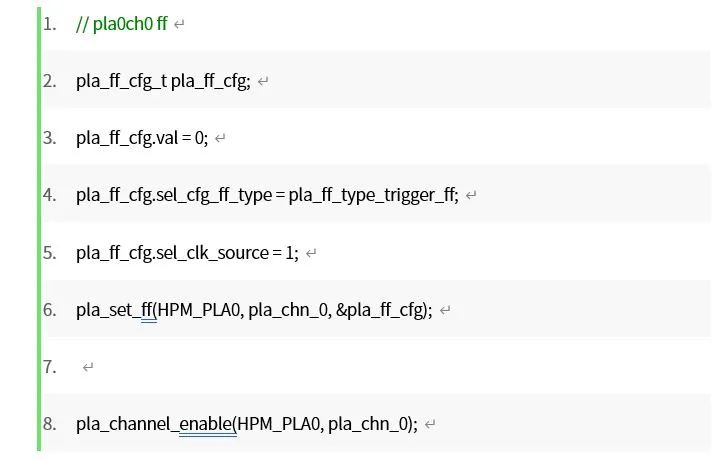

4. 可配置触发器

CFF 可配置的内容并不多,主要就是功能选择和时钟源,具体情况可参考源代码。需要注意的是触发器的同步复位、同步置位、异步复位、异步置位等信号有的是高电平有效,有的则是低电平有效,且有优先级顺序,使用时需要对照手册仔细调整。

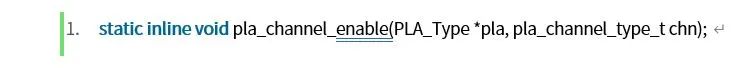

5. 使能 PLA

在完成上述全部配置完成以后,还需要对每一个通道进行使能。

在没有使能的情况下,PLA 的寄存器可以作为 1KB 的 APB SRAM 使用。

五

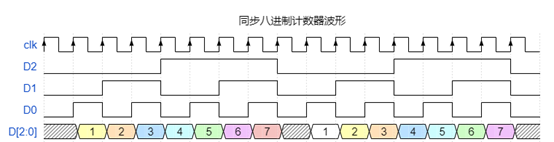

一个简单的例子:同步八进制计数器

1. 概述

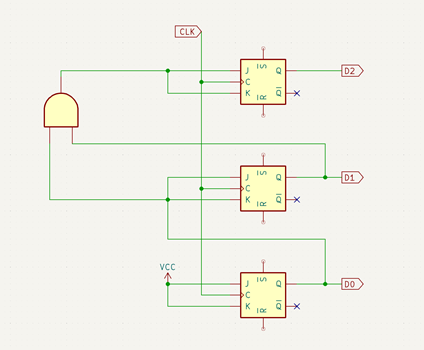

在前面章节的基础上,我们将实战使用 PLA 构建一个经典的同步时序逻辑电路:同步八进制计数器。为了简化问题让大家更容易理解,我们要构建的计数器只会计数,没有复位、没有使能、没有置数,长得更像是个分频器,它的电路结构如下所示:

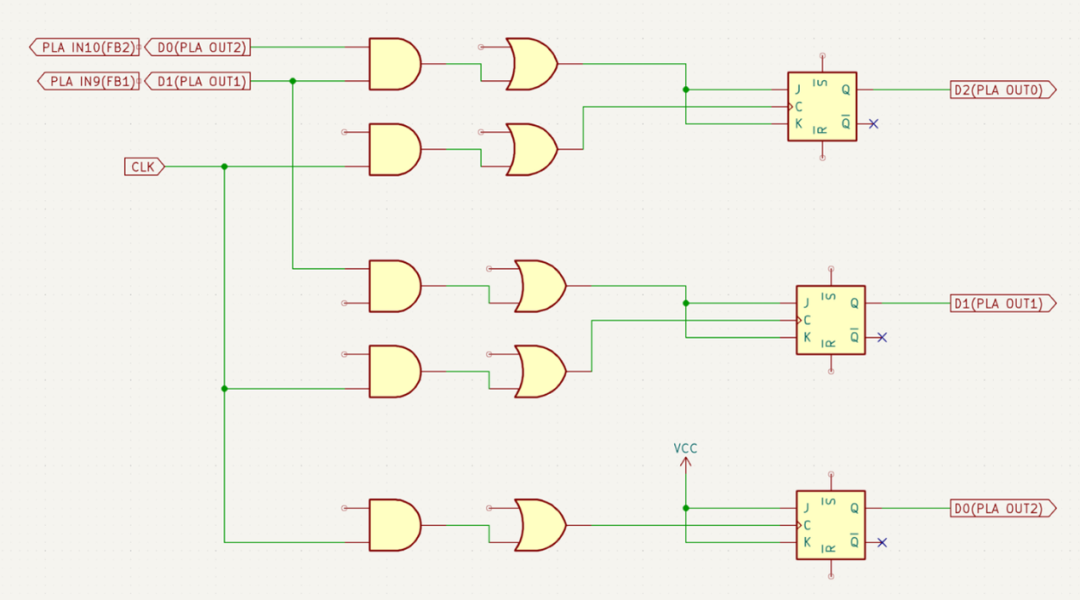

有了电路图,下一步就是将电路结构转换为 PLA 的配置代码。不过,由于 PLA 是与或结构,我们不妨进一步直接将使用到的与门、或门和各种信号都绘制出来,在编码时将会更加方便。

对照上图,我们可以提炼出以下信息:

· 此电路使用了 3 个 PLA 通道,每个通道的 CFF 均配置为 T 触发器(图上是 JK,实际功能是 T)

· 触发器时钟使用外部时钟PLA OUT0\OUT1\OUT2 分别作为计数器 D2\D1\D3 的输出

· OUT1\OUT2 将作为反馈信号进入通道 1 和 通道 2

2. 工程准备

本部分包括新建工程、使用 GPTMR 产生 1M PWM 作为时钟的代码,本文不打算讨论这一部分内容,读者可以参考 HPM_SDK 中的其他例程了解。为了区分三个通道的设置代码,在 main 函数前声明了三个通道的配置函数。

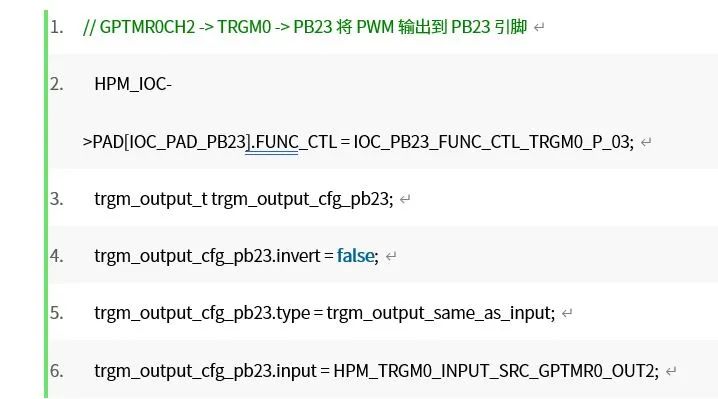

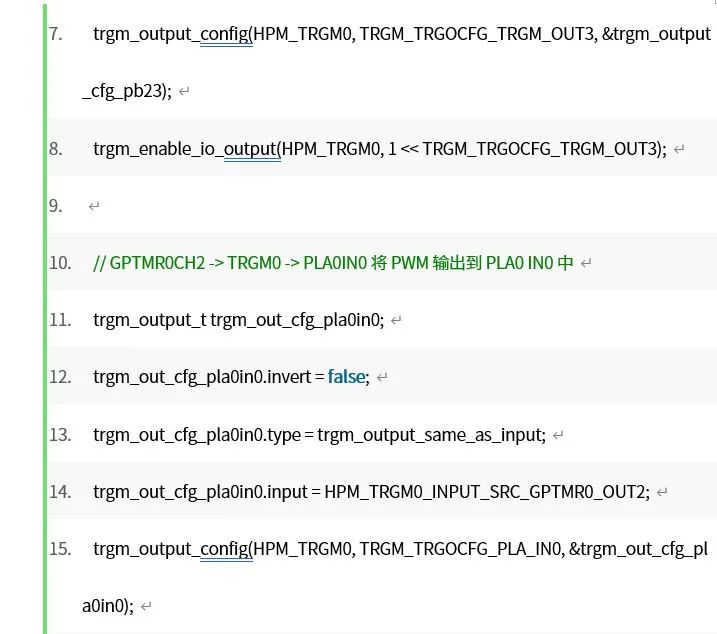

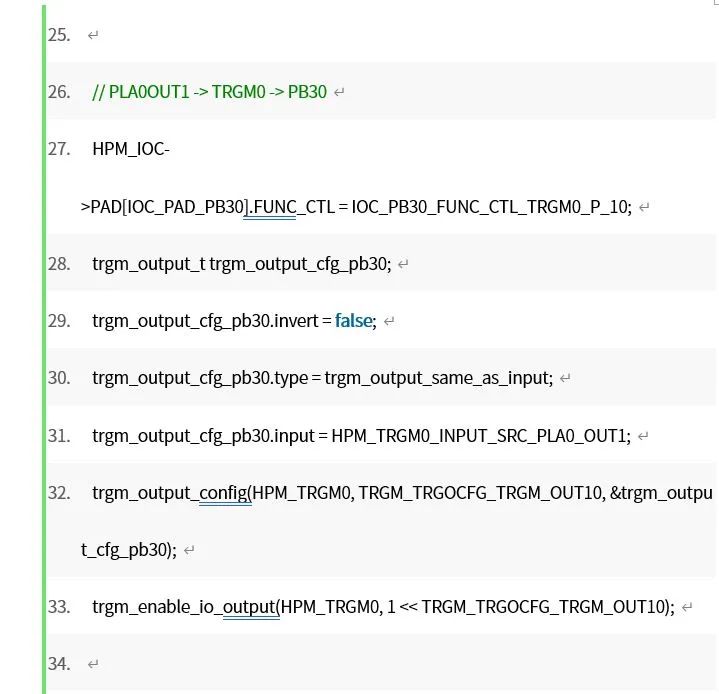

3. TRGM 与 I/O

PLA 并没有专属于自己的输入输出引脚,和其他增强运动控制系统外设一样,所有输入输出信号都要通过 TRGM 处理。因此,这里的代码将 GPTMR0 CH2 的 PWM 输出引入到了 PLA0 IN0 中,将 PLA0 OUT0/1/2 输出到三个外部引脚中。为了方便对比时钟波形和计数器输出,还将 GPTMR CH2 的 PWM 也输出到外部引脚中。

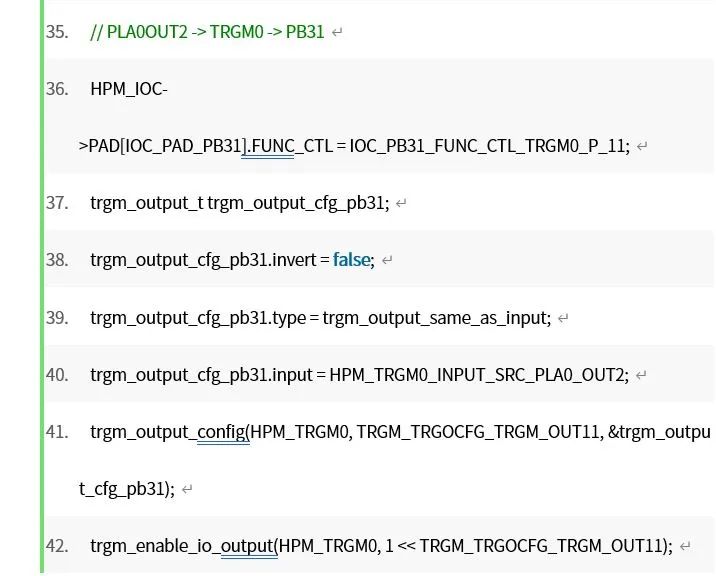

4. FILTER1

FILTER1 并没有特别的功能需求,因此我们只需要开启同步功能即可。

5. 通道 0

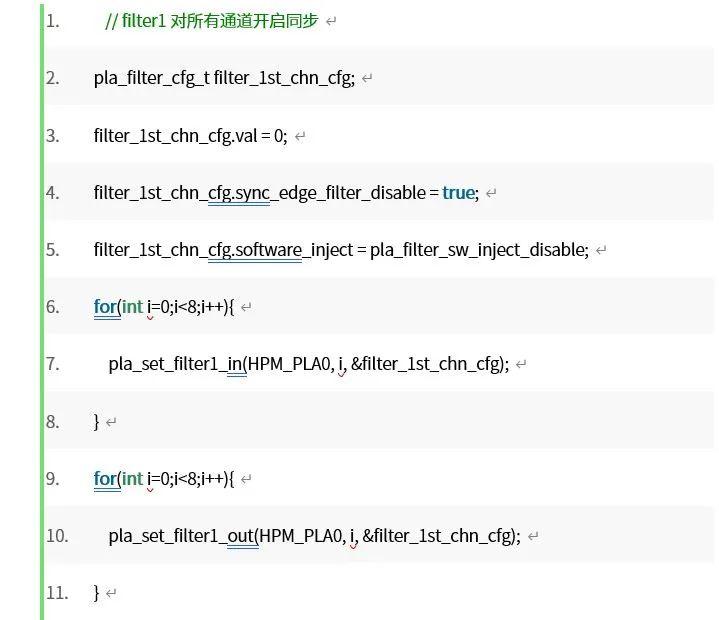

来到通道 0 的配置函数,首先声明与门阵列、或门阵列和两个滤波器的配置结构体变量。

通道 0 使用了两个与门。第一个与门根据两个反馈信号相与生成 T 触发器的 T 信号,先将它的全部 MUX 设为输出逻辑 1,再将反馈通道对应的 9、10 号 MUX 修改为输出原信号。第二个与门只需要输出 PWM 时钟信号,因此只设置一个 MUX 输出原信号,其余全部设置输出逻辑 1。

FILTER2 同样只需要设置同步。

通道 0 使用了两个或门。第一个或门需要输出与第一个与门完全相同的信号,因此 0 号 MUX 设置输出原信号,其余 MUX 输出逻辑 0(注意,没有使用的信号 MUX,一般与门设置输出逻辑 1,或门设置输出逻辑 0),第二个与门也基本一致。

FILTER3 同样设置信号同步,不过不要忘了 FILTER3 同时也输出触发器的同步异步复位置位,我们这个电路没有相关功能,因此全部根据手册设置为固定值即可。如果要使用这些功能,则需要另外构建他们的控制逻辑函数。

最后是 CFF 并使能通道。

其余两个通道配置过程大同小异,就不再复制粘贴那么多次了,完整的代码可在先楫社区中获取。最终的效果如下图所示。

六

结 语

通过介绍,相信大家对 PLA 已经有了一个较为全面的了解。在 6200 系列刚推出时,许多开发者非常关注的一点就是 PLA 外设能不能当作 FPGA 使用,对此,我个人的看法是“能,但不完全能”。PLA 拥有完备的逻辑结构,但是其资源数量注定只适合小型逻辑使用,尤其是触发器资源的缺乏,使得 PLA 很难单独构建稍复杂的时序逻辑电路。因此我们在开发 PLA 程序之前,对资源数量要把控地比较准确,以免做无用功。

除了底层资源的限制,个人认为,使用方式上 PLA 也有其遗憾之处:

重复的配置代码相当多,开发效率不高,写代码时容易发生错误

无法对内部信号进行调试,对复杂逻辑调试困难

“牵一发而动全身”,难以通过模块化设计等方式复用现有资料

基于以上原因,我认为图形化配置,程序自动生成配置代码将会是 PLA 极好的开发方式:PLA 配置项繁多但并不复杂,代码由机器生成非常合适;图形化配置的方式降低了开发者编写大量重复代码时出错的可能性,还可以通过抽象出电路图的方式协助开发者调试;甚至还可以以此为基础造出 PLA 的模拟器。

当然,即使没有这些,PLA 也仍不失为构建简单逻辑的好工具,也期待有更多开发者给出他们使用 PLA 的姿势与心得,共同学习共同进步。

-

mcu

+关注

关注

147文章

18652浏览量

388532 -

可编程逻辑

+关注

关注

7文章

526浏览量

45329 -

先楫半导体

+关注

关注

12文章

270浏览量

3170

发布评论请先 登录

可编程逻辑阵列PLA内部逻辑结构示意

针对新能源、储能、高性能控制等应用,先楫半导体推出HPM6200系列MCU

先楫半导体近日发布全新MCU通用微控制器 HPM6200 系列

可编程逻辑阵列(PLA)简介

探秘HPM6200系列MCU的可编程逻辑阵列

开发者分享|探秘HPM6200系列MCU的可编程逻辑阵列

开发者分享|探秘HPM6200系列MCU的可编程逻辑阵列

评论