当我们提到RISC-V时,我们往往会想到数字电子和计算。虽然两者之间存在很强的相关性,但仍有许多公司正在开发由 RISC-V 技术提供支持的模拟 IP 解决方案。Agile Analog 就是这样的一家公司,它以使用数字电子产品创建可配置的模拟 IP 解决方案而闻名。

本周,Agile Analog 宣布将为RISC-V应用推出完整的模拟 IP 子系统,重点放在电池供电的物联网解决方案上。在本文中,我们将了解Agile Analog 的三个 IP 子系统,以及它们将如何使 RISC-V 社区受益。

AgilePMU

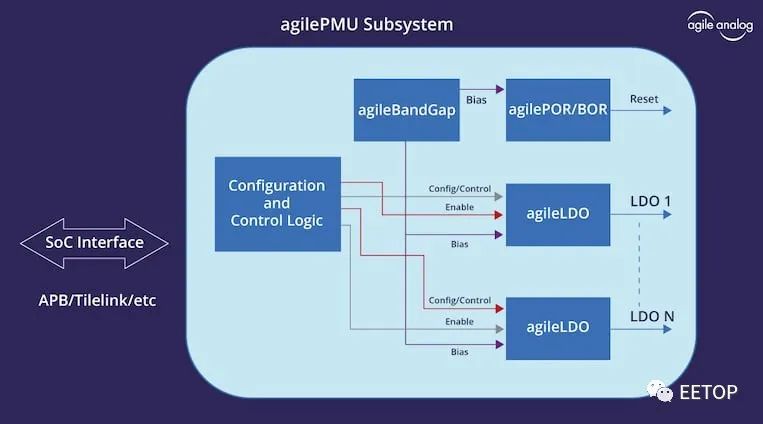

Agile Analog 向 RISC-V 生态系统推出的三个 IP 子系统中的第一个是一系列电源管理单元。这些来自 Agile Analog 的电源管理单元称为agilePMU,是用于SoC/ASIC 的高度集成 PMU。

agilePMU的框图。图片由Agile Analog提供

agilePMU 设计有一个集成数字控制器、两个可单独编程的低压降稳压器 (LDO) 和一个内部带隙电压参考,旨在将 RISC-V 系统的性能与低功耗运行融为一体。该产品旨在监控电力系统的实时状态并提供反馈以确保最佳系统性能。

AgileSMU

除了 PMU 产品,Agile Analog 还将在其RISC-V 子系统宏中 包含一个称为agileSMU的睡眠管理单元 (SMU)。

agile SMU 框图。图片由Agile Analog提供

agileSMU 是一种低功耗解决方案,旨在以及时可靠的方式将 SoC 从睡眠模式唤醒,同时最大限度地提高电源效率。为此,agileSMU 由一个范围从 32 kHz 到 20 MHz 的可编程振荡器和几个用于启动 SoC 唤醒的低功耗比较器(1.5 uA 活动电流)组成。SMU 还包括一个启动时间为 10 us、断言时间为 5 us 的上电复位 (POR),以确保 SoC 的启动复位。

在 IoT 系统中,由于主 SoC 进入睡眠模式以节省电量,因此该 SMU 可以确保低功耗运行。

Agile传感器接口

Agile Analog 的 RISC-V 产品组合中包含的三个 IP 子系统中的最后一个是其传感器接口产品,称为agileSensorIF。

agileSensorIF 解决方案旨在以高效和高性能的方式实现传感器与主 SoC 的接口。agileSensorIF 解决方案具有多个集成块,例如 ADC、DAC、低功耗模拟比较器和相关的带隙发生器。此外,该系统具有集成的配置和控制逻辑,以实现系统的可确认性和控制。

agileSensorIF的框图。图片由Agile Analog提供

与大多数Agile 解决方案一样,这些模块中的每一个都是可配置的,包括 ADC 和 DAC 的数量以及它们的位深度和采样率。达到最大值后,ADC 可以达到 12 位分辨率和 64 MSPS 的采样率,而 DAC 可以达到 12 位分辨率和 20 MSPS 的速率。

-

电源管理

+关注

关注

117文章

8540浏览量

148241 -

数字控制器

+关注

关注

0文章

122浏览量

20146 -

PMU

+关注

关注

1文章

127浏览量

23402 -

低压降稳压器

+关注

关注

1文章

111浏览量

9823 -

RISC-V

+关注

关注

49文章

2946浏览量

53534

发布评论请先 登录

rIsc-v的缺的是什么?

risc-v的发展历史

关于RISC-V学习路线图推荐

为什么选择RISC-V?

RISC-V MCU开发相关资料分享

256核!赛昉发布全新RISC-V众核子系统IP平台

RISC-V SIG成功将Chromium等桌面软件适配到openEuler RISC-V

赛昉科技发布首个国产高性能RISC-V多核子系统IP平台

赛昉科技发布全新RISC-V众核子系统IP平台

芯来科技正式发布基于RISC-V处理器的HSM子系统解决方案

如何将模拟子系统引入RISC-V呢?

如何将模拟子系统引入RISC-V呢?

评论