本土RISC-V CPU IP领军企业——芯来科技正式发布基于RISC-V处理器的HSM子系统解决方案,提供专业有效的信息安全保护以及加解密功能。

随着通信和网络的不断进步与发展,高速的信息传递和设备互联已经成为了必然的趋势,这对于信息安全保障提出了更高的要求,防止信息泄露的需求与日俱增,对于芯片的安全防护能力是极大的挑战,系统设计亟需完整的安全解决方案。

此次芯来科技发布的HSM子系统,作为针对信息安全的完整解决方案,旨在帮助各类场景对于芯片层面信息安全的需求。HSM是硬件安全模块(Hardware Security Module)的简称。HSM通过验签和加解密等功能来保护系统认证所需要的密钥和敏感数据,同时可以为在线升级、固件升级等提供安全保护,以确保传输消息和数据的机密性和可靠性。

加解密和验签等功能都依赖于较为复杂的算法,软件方案的效率较低,会影响系统整体的性能。专用于加解密和敏感数据管理的HSM硬件加速模块可以在提高运算的效率的同时提供强有力的保护。目前在汽车电子领域,HSM已经成为了必不可少的模块,且拥有用于汽车电子的特定标准,HSM通过其自己的处理器核心来执行汽车应用场景所需的所有IT安全功能。芯来科技的HSM模块已经可应用于汽车电子、网络传输、视觉安防、工业控制等领域。

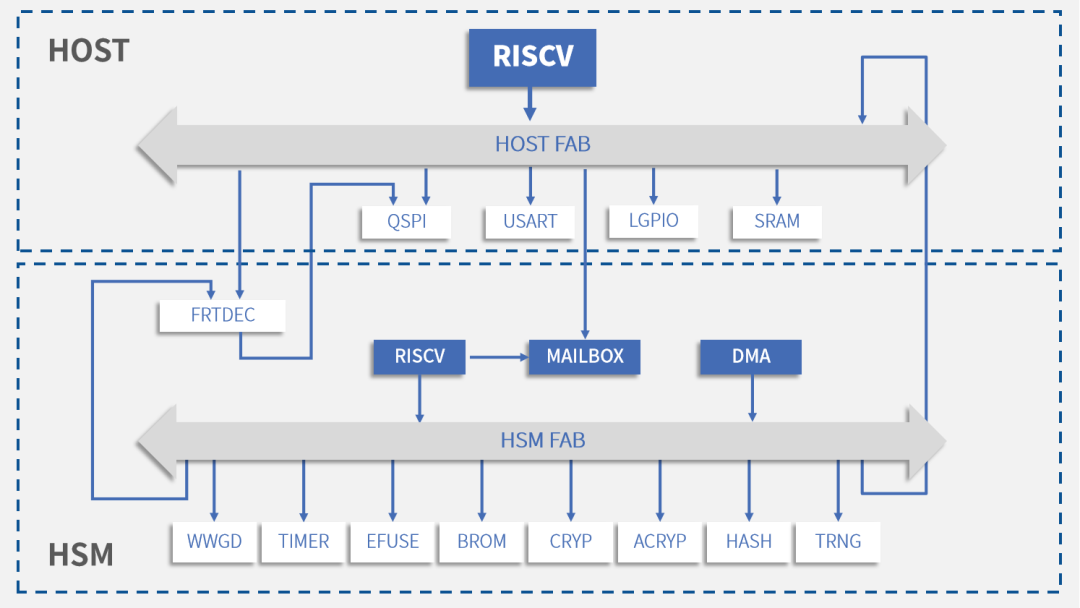

芯来科技提供与Host系统紧耦合的HSM子系统,主要包含控制、通信、加解密等部分核心模块:

芯来自研的RISC-V CPU:可根据具体需求选择N300(普通系统)、NS300(安全防护更高)以及NA300(汽车电子)

MAILBOX:HOST访问HSM内部资源的唯一通道

EFUSE:密钥等信息安全存储

BROM:HSM第一级BootLoader

CRYP:对称加解密模块

ACRYP:非对称加解密模块

HASH:哈希算法模块

TRNG:真随机数生成模块

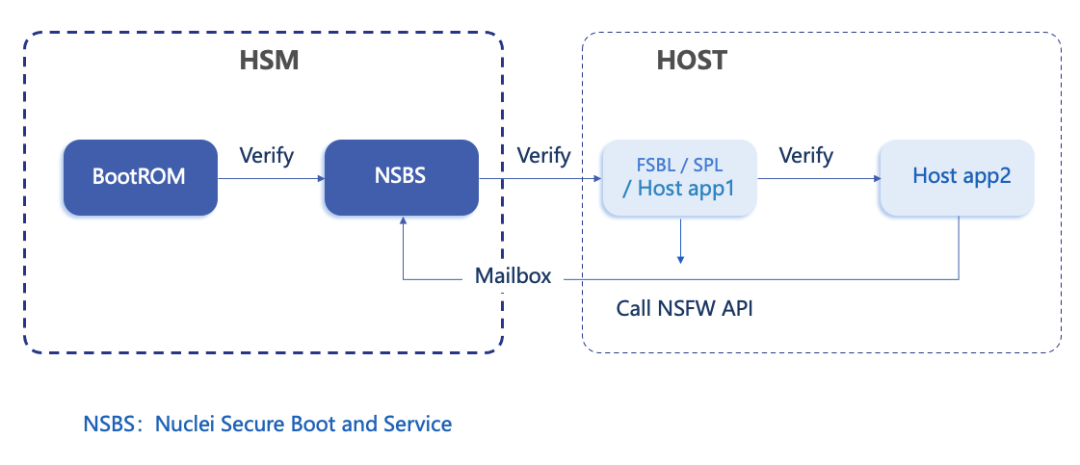

芯来的HSM模块提供完整的安全启动流程,安全启动中包含两级验证和加载启动,分别为芯片级和系统级两个层级,对应芯片厂商和系统厂商,每一级厂商都可以拥有自己的密钥对。

芯片厂商提供BootROM和一级Loader(NSBS固件),处于HSM系统中。芯片厂商的公钥用于验签一级Loader(NSBS固件),而系统厂商的公钥用于验签HOST系统的固件程序,软件启动流程如下图所示:

NSBS模块除了提供安全启动以外,还可以通过MAILBOX给HOST系统提供运行时的安全服务,包括:

密钥管理

加解密运算

哈希计算

eFuse烧写

密钥生成

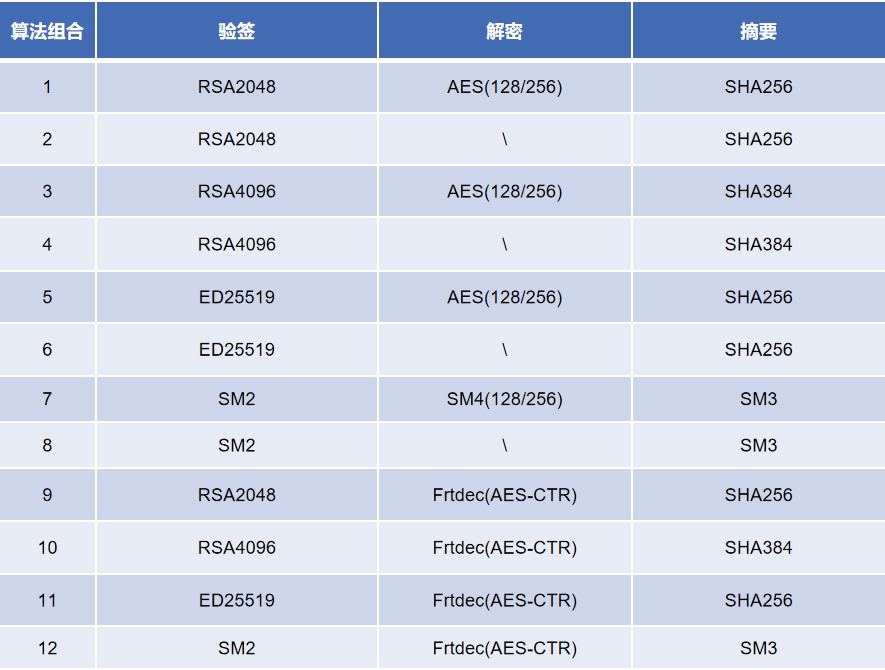

HSM Secure Boot支持12种安全启动组合,支持动态选择:

Secure Boot支持全流程系统仿真:

提供模版配置文件,一键加密打包脚本以及生成相配套的eFuse初始化文件

支持两级安全启动全流程仿真

Secure Boot提供完整的FPGA测试环境:

FPGA环境下支持和仿真环境相同的原始固件

提供功能完善的上位机工具,支持生成并烧写eFuse配置文件和打包原始固件,不需要额外的烧写工具

芯来的HSM提供非对称认证和对称加解密解决方案:

非对称认证,主要用于验签:

芯片厂商和系统厂商拥有各自独立的密钥对;

支持ED25519,RSA2048/4096以及国密SM2验签算法

对称加解密,主要用于固件加解密

芯片厂商和系统厂商各自拥有根密钥

支持AES和国密SM4加解密算法

支持RFC3394定义的AES以及GB/T 36624-2018定义的SM4密钥封装算法,提供更高的安全性能

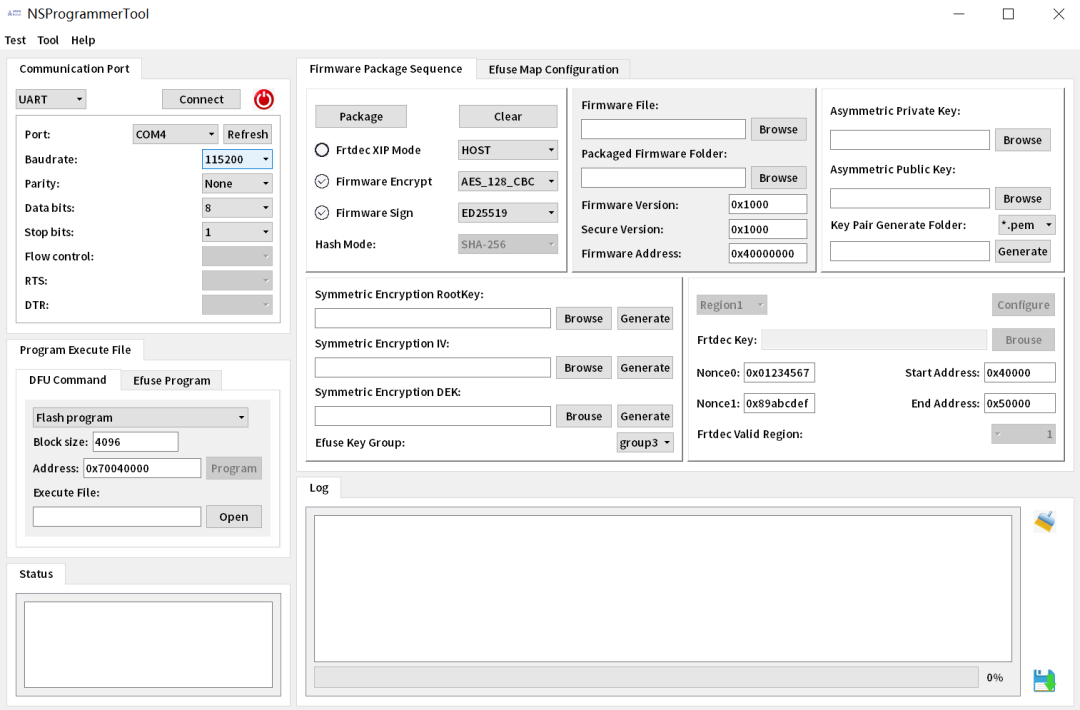

芯来科技为HSM解决方案提供功能完整丰富的上位机工具(NSTools):

该上位机工具提供两大功能,帮助客户更便捷的使用HSM方案:

固件打包功能:

支持两级镜像的打包,多级密钥生成

根据UI界面的配置,生成固件头,加密固件,计算固件摘要和签名,生成打包后二进制文件

生成eFuse配置文件

烧写功能:

DFU:烧写或者擦除Nor Flash指定某个扇区以及整片,可以实现在线更新固件

eFuse烧写:单bit或者单word烧写,根据生成或者指定的eFuse配置文件进行批量烧写

除了上述功能以外,芯来HSM解决方案还支持其它六大安全特性: 安全存储

支持flash数据通路上的on-the-fly硬件流解密

密钥销毁

支持备份密钥

支持密钥销毁

防止代码回滚

支持固件版本管理

锁定软件bootloader更新

支持限制软件bootloader,提高安全性;

生命周期管理

开发模式

量产模式

支持备份镜像,支持多种加解密算法

信息安全的保护是当下电子产业必不可少的元素。RISC-V作为开放标准的、可扩展的指令集能够进一步提高了HSM子系统的灵活性以及高度可定制性,同时为国产自主提供了更稳定的基础。芯来科技背靠中国本土市场,将不断完善以芯来RISC-V CPU为核心的HSM安全方案特性,致力于打造完整的信息安全解决方案,配合行业的演进以及发展趋势,目前HSM安全方案已经落地,并且正式进入了商用阶段。

关于芯来科技 芯来科技成立于2018年,一直专注于RISC-V CPU IP及相应平台方案的研发,是本土RISC-V领域的代表性企业。

芯来科技从零开始,坚持自研,打造了N/U、NX/UX四大通用CPU IP产品线和NS、NA、NI三个专用CPU IP产品线。其中:

* N/U(支持SV32 MMU)是32位架构,主要用于边缘计算、低功耗和IoT场景;

* NX/UX(支持SV39和SV48 MMU)是64位架构,主要用于数据中心、网络安全、存储等高性能应用场景;

* NS(Security)面向支付等高安全场景;

* NA(Automotive)面向功能安全汽车电子场景;

* NI(Intelligence)面向AI等高性能计算场景。

目前已有超过200家国内外正式授权客户使用了芯来科技的RISC-V CPU IP,遍及AI、汽车电子、5G通信、网络安全、存储、工业控制、MCU、IoT等多个领域。

审核编辑:刘清

-

处理器

+关注

关注

68文章

20149浏览量

247177 -

上位机

+关注

关注

27文章

994浏览量

56713 -

加解密

+关注

关注

0文章

18浏览量

6691 -

RISC-V

+关注

关注

48文章

2793浏览量

51915 -

芯来科技

+关注

关注

0文章

78浏览量

3907

原文标题:芯来科技正式发布HSM安全子系统方案,进一步拓展RISC-V应用领域

文章出处:【微信号:nucleisys,微信公众号:芯来科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

直播预约 |开源芯片系列讲座第30期:“一生一芯”计划——从零开始设计自己的RISC-V处理器芯片

为什么RISC-V是嵌入式应用的最佳选择

睿思芯科携灵羽处理器亮相2025 RISC-V中国峰会

芯来科技新一代RISC-V高性能处理器IP UX1030H 全面支持RVA23

香橙派发布RISC-V高性能智能网关解决方案OrangePi R2S,赋能智能家居和工业互联网

HPM5E31IGN单核 32 位 RISC-V 处理器

HXS320F28027数字信号处理器(32位RISC-V DSP)

2025芯来RISC-V技术研讨会苏州站成功举办

赛昉科技推出RISC-V PLC工业自动化解决方案

Imagination放弃RISC-V处理器内核开发

Andes晶心科技推出D45-SE RISC-V处理器

HighTec C/C++编译器套件全面支持芯来RISC-V IP

芯来科技正式发布基于RISC-V处理器的HSM子系统解决方案

芯来科技正式发布基于RISC-V处理器的HSM子系统解决方案

评论