01 发起沿和捕获沿

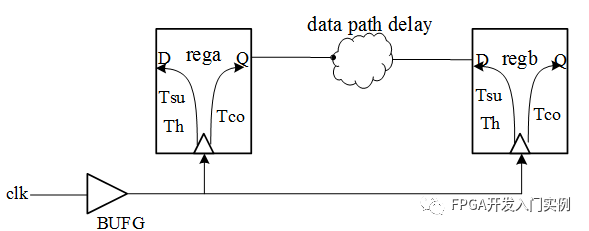

下图是一个经典时序分析模型,无论寄存器A与寄存器B是否在同一个芯片中,下列概念均适用。

02 时序路径

2、FPGA内部REGA时钟端口到REGB的数据端口

3、FPGA末级寄存器的时钟端口到器件B的输入数据端口

4、组合逻辑路径,FPGA输入端口到输出端口

1 源端时钟路径(红色)

2 数据路径(蓝色)

3 目的端时钟路径(黄色)

03 数据到达时间与数据需求时间

在clk时刻参考时间为0的条件下,进行数据到达时间、时钟到达时间、数据要求时间(建立时间)、数据要求时间(保持时间)的时序分析。

1.数据到达时间

数据到达时间=0+Tclka+Tco+Tdata

2.时钟到达时间

时钟到达时间=捕获沿+Tclkb

捕获沿=0+T(一个时钟周期)

时钟到达时间=T+Tclkb

3.数据要求时间-建立时间

数据要求到达时间=时钟到达时间-Tsu-setupuncertainty

=T+Tclkb-Tsu-setup uncertainty

setup uncertainty:时钟抖动造成的不确定时间。

4.数据要求时间-保持时间

数据要求保持时间=时钟到达时间+Th+hold uncertainty

=T+Tclkb+Th+hold uncertainty

hold uncertainty: 时钟抖动造成的不确定时间。

04 建立时间裕量与保持时间裕量

1.建立时间裕量

建立时间裕量=数据要求到达时间-数据到达时间

=T+Tclkb-Tsu-setupuncertainty -(Tclka+Tco+Tdata)

2.保持时间裕量

保持时间裕量=数据到达时间(新的)-数据要求保持时间

=Tclka+Tco+Tdata-Tclkb-Th-hold uncertainty

3.建立与保持时间裕量整合

建立时间裕量与保持时间裕量为正,则满足时序要求,如果时间裕量为负,则不满足时序要求。

建立时间裕量与保持时间裕量为正,则满足时序要求,如果时间裕量为负,则不满足时序要求。

系统时钟频率

Tlogic为代码导致的延时,Tnet为布线延时。

05 总结

1、发送沿通常为时序分析的参考时间点

2、通常,捕获沿=发送沿+1个时钟周期

3、建立时间与保持时间是由芯片工艺本身决定。提高系统时钟频率由决Tdata定。

-

FPGA设计

+关注

关注

9文章

431浏览量

28218 -

寄存器

+关注

关注

31文章

5620浏览量

130455 -

时序分析

+关注

关注

2文章

130浏览量

24280 -

CLK

+关注

关注

0文章

132浏览量

18104

发布评论请先 登录

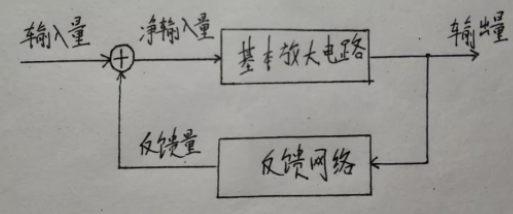

放大电路中反馈的基本概念及判断方法

总结一下在时序分析中的基本概念及基本术语

总结一下在时序分析中的基本概念及基本术语

评论