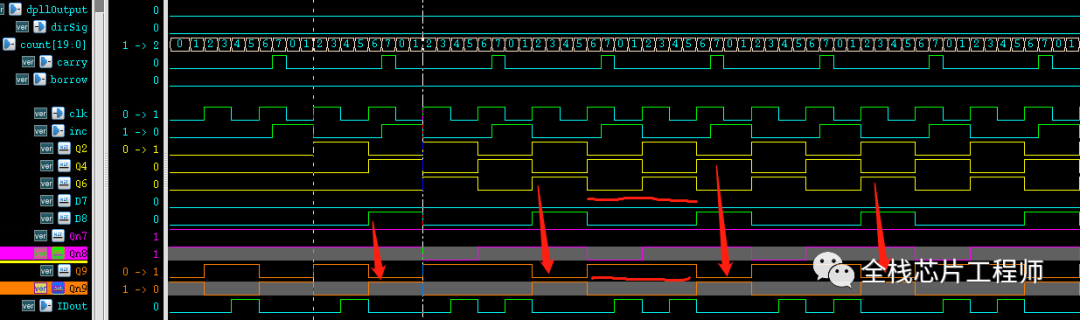

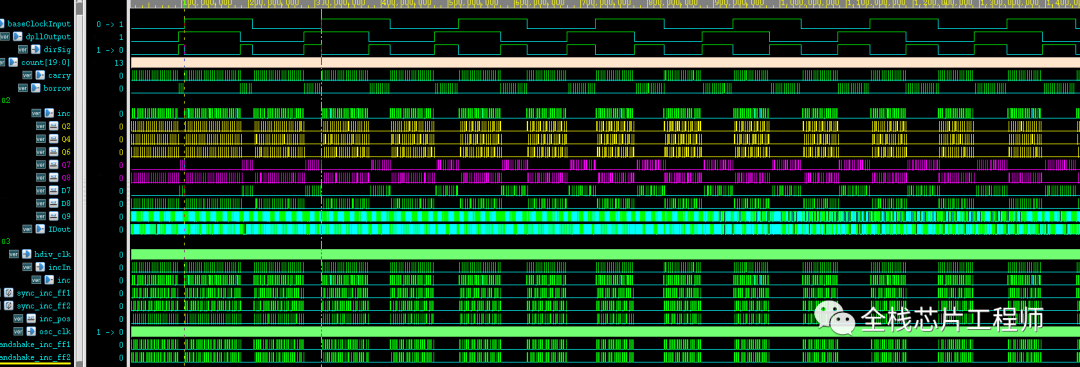

数字PLL中会利用到JK触发器,JK触发器的J=1,K=1时,JK触发器输出取反,即二分频。

当有进位脉冲信号CARRY时,则在输出的二分频信号中插入半个脉冲,以提高输出信号的频率;

当有借位脉冲信号BORROW时,则在输出的二分频信号中减去半个脉冲,以降低输出信号的频率。

DRC、LVS run一下:

最近准备集成64位双核RISCV处理器、LPDDR4、MIPI、ISP、VPU,开发一款多媒体SoC芯片,TSMC12nm工艺。数据涉密,架构开放讨论。

欢迎加入【全栈芯片工程师】知识星球,手把手教你设计MCU、ISP图像处理,从算法、前端、DFT到后端全流程设计。

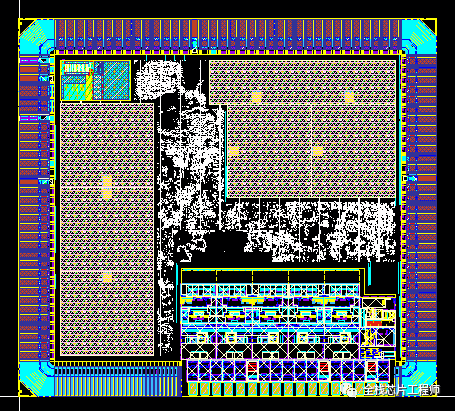

实战MCU+ISP图像处理芯片版图

实战ISP图像算法效果

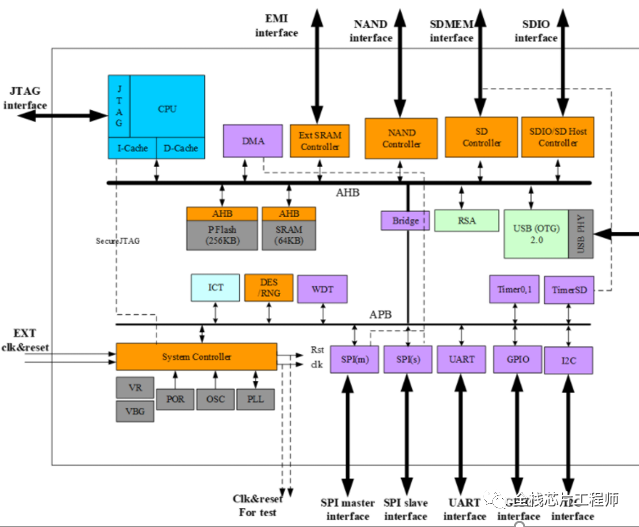

知识星球发起MCU项目启动,大家一起参与MCU项目规格启动讨论,我把设计、验证、DFT、后端的知识点全部罗列出来,大家一起来完善。

以项目驱动的方式介绍MCU芯片全流程设计的方法;提炼相关的检查列表、signoff checklist的样本;让星球成员熟悉SoC架构、设计流程、开发进度、项目管理;

责任编辑:彭菁

-

soc

+关注

关注

40文章

4621浏览量

230096 -

触发器

+关注

关注

14文章

2065浏览量

63536 -

MCU芯片

+关注

关注

3文章

260浏览量

13019

原文标题:数字PLL设计实战(一)

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

EDA全流程的重要意义,以及国内EDA全流程进展

无线充电器方案XS016MCU+全桥/半桥驱动芯片

建立完善的硬件设计全流程解决方案

芯片制造全流程及详解

芯片的制造全流程

芯片的制造全流程

数字芯片验证流程

MCU芯片全流程设计的方法

MCU芯片全流程设计的方法

MCU芯片全流程设计的方法

评论