仿真和验证是开发任何高质量的基于 FPGA 的 RTL 编码过程的基础。在前文中,我们介绍了面向实体/块的仿真,并介绍了如何在虹科的IP核中执行面向全局的仿真。

前文回顾

虹科干货 | 如何测试与验证复杂的FPGA设计(1)——面向实体或块的仿真

虹科干货 | 如何测证复杂的FPGA设计(2)——如何在虹科的IP核中执行面向全局的仿真

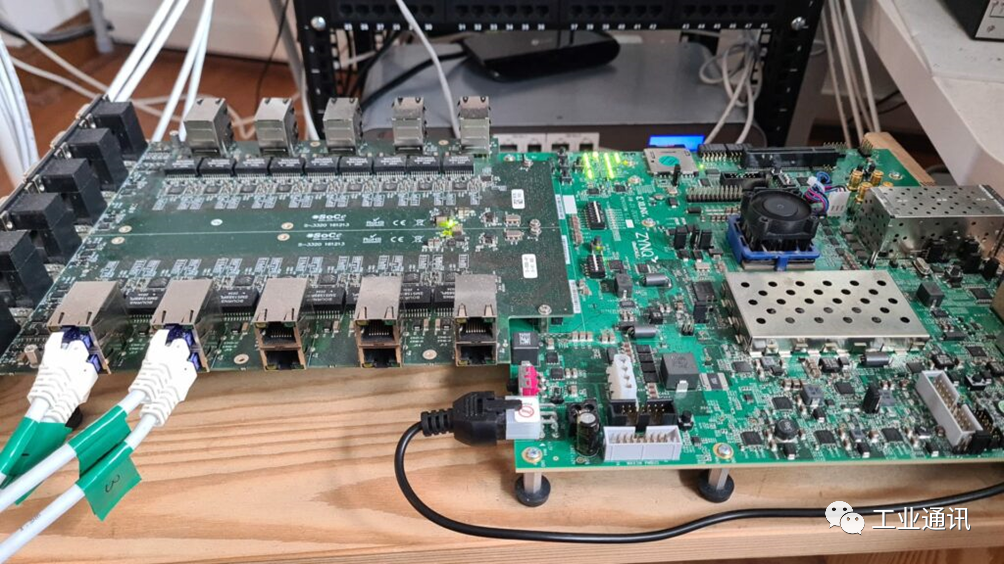

尽管扩展的仿真计划提供了良好的可信度,但仍有许多corner的情况无法在虚拟环境中验证。对于这些情况,开发人员需要制定基于硬件的测试计划,而这也是获得高质量结果的最后一步。在本篇文章中,我们将对介绍第三个关键步骤——在硬件平台上验证IP核。

硬件测试

硬件测试是为IP核产品执行高质量测试和验证计划的最后一步,主要可以分为以下几个阶段:

1

测试准备

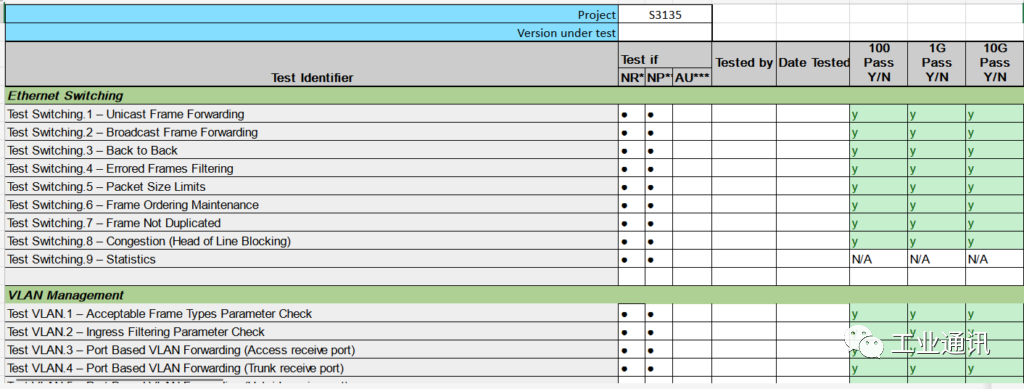

该阶段定义了在产品开始测试之前必须完成的步骤。在这个阶段,需要制定测试计划文档,里面详细描述了必须在 DUT(被测设备)上执行的每一项测试。

2

测试执行

测试执行阶段主要是执行上一个阶段中制定的测试用例

3

问题报告

该阶段需要检查和报告在测试执行期间检测到的所有问题,虹科技术团队将提供一个问题电子表格,其中将记录在测试阶段检测到的每个问题。每当注册新问题时,都会向开发团队报告,并且能够追踪哪些问题已解决,哪些问题仍有待审查。

4

测试结束

该阶段确定测试阶段何时完成,并创建测试结果文档,其中将包含成功执行的测试的摘要以及有关测试的更多相关信息。

虹科SoC-e测试工具

为了优化测试执行过程,我们使用了虹科SoC-e测试工具,以进行自动化测试。该工具考虑了以下内容:

DUT配置过程

流量注入和嗅探

记录从DUT 返回的流量

验证保存的日志

将DUT 设置为原始状态

虹科SoC-e测试软件架构

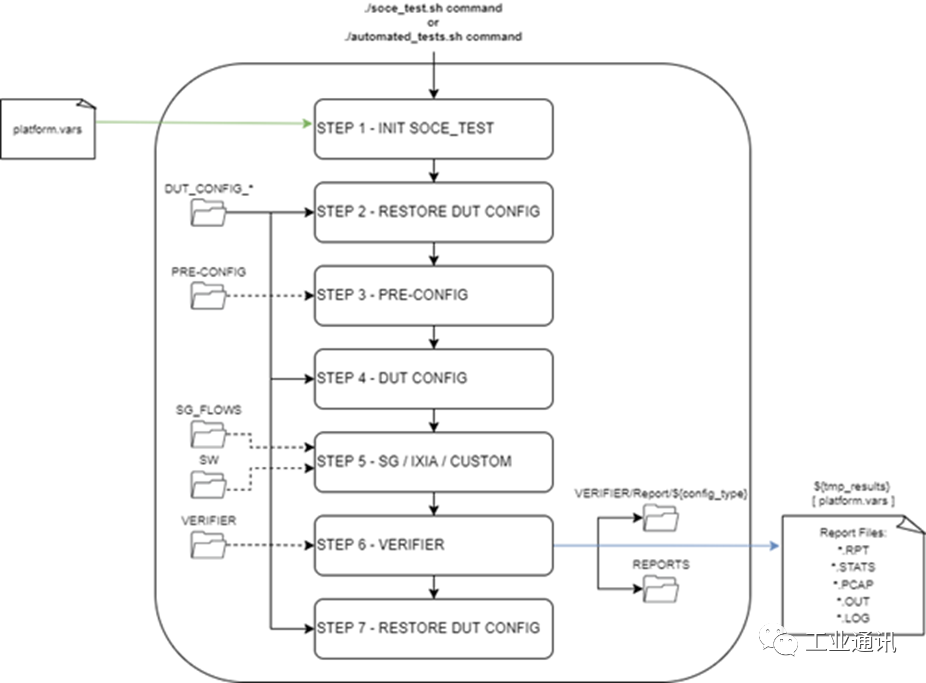

该工具的第一步与DUT 配置的执行有关。这是通过名为 Platform.vars 的输入配置文件完成的。通过该文件,用户可以配置不同的参数,如 DUT SSH 参数、主机 PC 的IP 地址或网络接口。

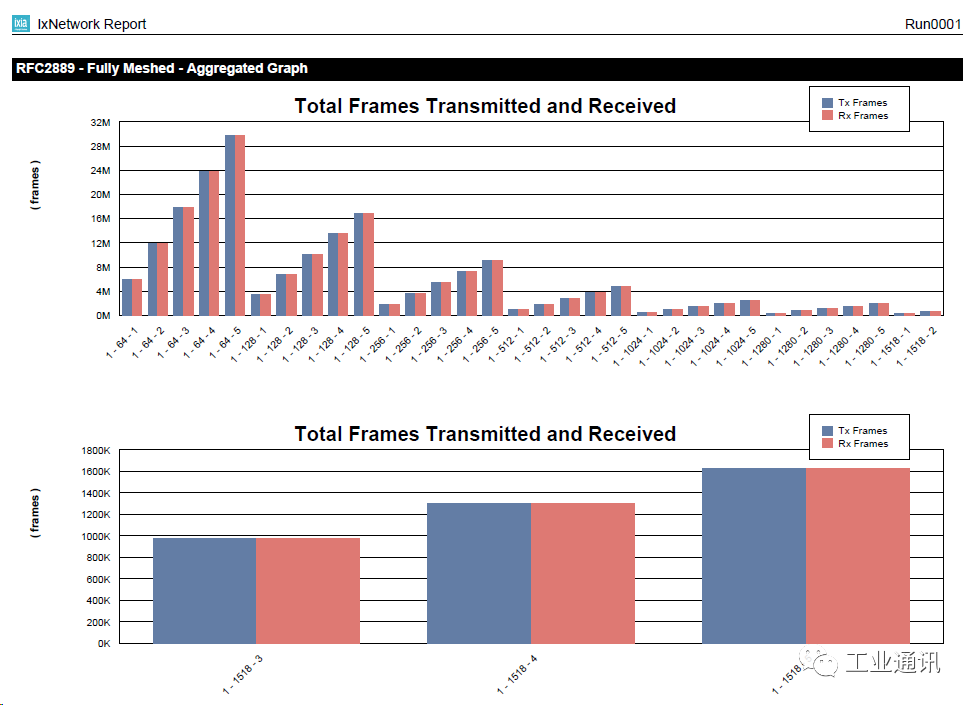

第二步,完成TS(测试站)和 DUT之间的流量注入和嗅探。我们有不同的第三方设备用作测试站,但最常用的设备之一是IXIA Novus One Plus。流量可以通过 IXIA 的 Python API 轻松发送。数据包操作是通过 Scapy Python 模块完成的。尽管 Scapy 允许传输该工具生成的所有流量,但它是使用不同的工具tcpreplay执行的。这使我们能够克服由 Scapy 引起的带宽和准确性方面的某些限制。在此步骤中,测试提供了自定义流量的灵活性,以验证不同的 DUT 功能。可扩展性不是问题,因为该工具支持添加额外的流量和测试端口。

第三步,该工具使用测试站或通过 Linux tcpdump 软件登记来自 DUT 的流量。

第四步,在虹科SoC-e测试工具验证上一步中存储的信息(统计、寄存器转储(dump)等),以检查一切是否正常。通过这两个步骤,SoC-e 测试工具为测试用例的验证提供了一个很好的解决方案。

最后,第五步,也是最后一步。最后一步的主要目的是将 DUT 配置恢复到其原始状态,因为它可能在测试期间被修改。

-

FPGA设计

+关注

关注

9文章

431浏览量

28215

发布评论请先 登录

高性价比ECU测试验证方案:虹科PCAN-USB Pro FD助力打造更加灵活的 HiL 测试平台

再获国际权威认可!虹科方案荣登CiA官方期刊

寻找8路CAN FD/2路1000BASE-T1通讯测试设备?虹科一体化方案重塑测试效率

虹科一体化车载测试实现多协议数据零丢包

虹科HK-CoreTest:专业的CAN/CAN FD总线测试软件,高效易用

汽车CAN/以太网一体化测试板:虹科多协议车载测试解决方案

德思特方案 | 整车 GNSS 产线测试,3 分钟高精度验证

寻找中文版车载总线测试软件?虹科HK-CoreTest:本土化智能测试解决方案

圆满收官 | 虹科CAN总线专题全系列直播精华回顾已上线!

新品发布 | 车辆矢量测试难?虹科WVS系统来破局

虹科案例 | 为什么汽车零部件头部企业,选择虹科方案做方向盘EOL测试?

直播回顾 | 硬核干货放送,虹科CAN总线应用层直播助您告别低效联调,破解车载网络开发核心难题

虹科车辆网络通讯测试主板:双系统适配 × 工业级稳定 × 零门槛部署

虹科干货 | 如何测试与验证复杂的FPGA设计(3)——硬件测试

虹科干货 | 如何测试与验证复杂的FPGA设计(3)——硬件测试

评论