3D IC Testing

审稿人:北京大学 冯建华

审稿人:北京大学 张兴 蔡一茂

https://www.pku.edu.cn

10.9先进表征技术与测试技术

第10章 集成电路基础研究与前沿技术发展

《集成电路产业全书》下册

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

集成电路

+关注

关注

5446文章

12468浏览量

372687

发布评论请先 登录

相关推荐

热点推荐

电机控制专用集成电路PDF版

作速度调节器、电流调节器、基极驱动电源等方面的应用。

除前几章各种电机专用驱动器集成电路外,在第11章介绍有较宽适用性的单管、半桥、H桥和三相逆变桥智能功率集成电路,包括典型产品、水平和应用示例。

为

发表于 04-22 17:02

中国集成电路大全 接口集成电路

资料介绍本文系《中国集成电路大全》的接口集成电路分册,是国内第一次比较系统地介绍国产接口集成电路的系列、品种、特性和应用方而知识的书籍。全书共有总表、正文和附录

发表于 04-21 16:33

国内集成电路产业高质量发展应有五个着力点

集成电路作为信息产业的底座与核心,已经成为发展新质生产力的重要载体,也对科技创新和产业创新的深度融合提出更为迫切的需求。 “集成电路自身就是发展新质生产力的重要阵地,是科技创新的‘出题

集成电路产业新地标 集成电路设计园二期推动产业创新能级提升

在2025海淀区经济社会高质量发展大会上,海淀区对18个园区(楼宇)的优质产业空间及更新改造的城市高品质空间进行重点推介,诚邀企业来海淀“安家”。2024年8月30日正式揭牌的集成电路设计园二期就是

硅集成电路技术的优势与挑战

硅作为半导体材料在集成电路应用中的核心地位无可争议,然而,随着科技的进步和器件特征尺寸的不断缩小,硅集成电路技术正面临着一系列挑战,本文分述如下:1.硅集成电路的优势与地位;2.硅材料对CPU性能的影响;3.硅材料的技术革新。

集成电路为什么要封胶?

集成电路为什么要封胶?汉思新材料:集成电路为什么要封胶集成电路封胶的主要原因在于提供多重保护和增强性能,具体来说包括以下几个方面:防止环境因素损害:集成电路在工作过程中可能会受到静电、

集成电路的引脚识别及故障检测

一、集成电路的引脚识别 集成电路是在同一块半导体材料上,利用各种不同的加工方法同时制作出许多极其微小的电阻、电容及晶体管等电路元器件,并将它们相互连接起来,使之具有特定功能的电路。半导

2025年,多地筹谋集成电路产业

2025年1月14日,北京市第十六届人民代表大会第三次会议开幕,北京市市长殷勇作政府工作报告。政府工作报告中指出,2024年北京市人工智能核心产业规模突破3000亿元,集成电路重大项目顺利实施。并提出,2025年将强化科技创新

TSV三维堆叠芯片的可靠性问题

孔质量和 信赖性保证难度大 ;(2) 多层芯片堆叠结构的机械稳 定性控制难度大 ;(3) 芯片间热管理和散热解决方案 复杂 ;(4) 芯片测试和故障隔离、定位困难。 2.1 TSV 孔的质量和可靠性问题 作为三维集成电路中的垂直互连通道,TSV 孔 的质量和可靠性对系

集成电路电磁兼容性及应对措施相关分析(三)集成电路ESD 测试与分析

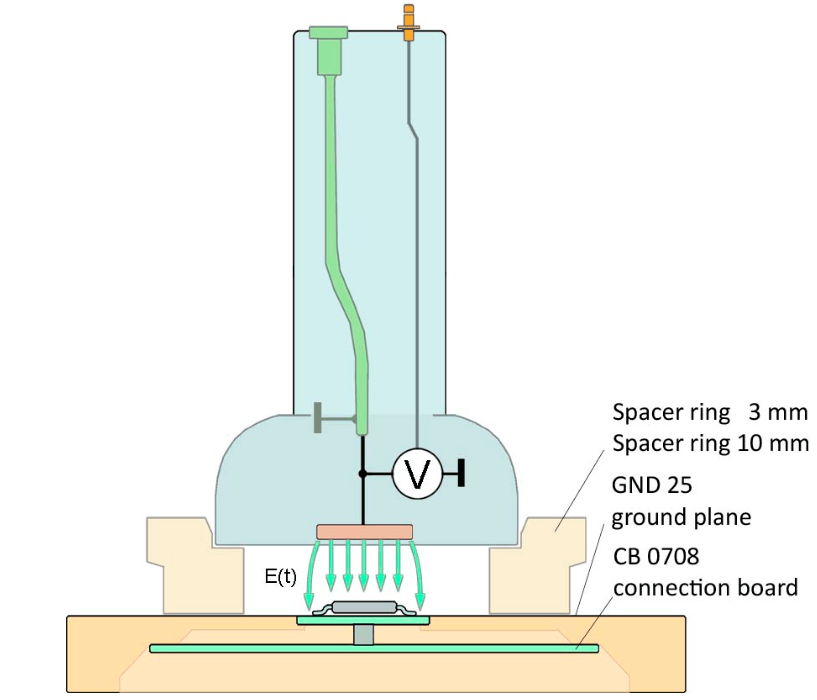

测量对于确定IC的EMC特性是必要的。只有准确了解IC的EMC特性,才能在生产前采取有效的预防措施,提高产品的抗ESD能力和EMC性能,避免后期因ESD干扰导致的产品故障和成本增加等问题集成电路ESD测试与分析1、测试环境与电场

集成电路电磁兼容性及应对措施相关分析(三)—集成电路ESD 测试与分析

和成本增加等问题 。 三、集成电路ESD 测试与分析 1、测试环境与电场产生 图5 使用 ESD 发生器的测量设置l 测试环境,

10.9.6 三维集成电路测试∈《集成电路产业全书》

10.9.6 三维集成电路测试∈《集成电路产业全书》

评论