引言

器件尺寸的不断缩小促使半导体工业开发先进的工艺技术。近年来,原子层沉积(ALD)和原子层蚀刻(ALE)已经成为小型化的重要加工技术。ALD是一种沉积技术,它基于连续的、自限性的表面反应。ALE是一种蚀刻技术,允许以逐层的方式从表面去除材料。ALE可以基于利用表面改性和去除步骤的等离子体或热连续反应。

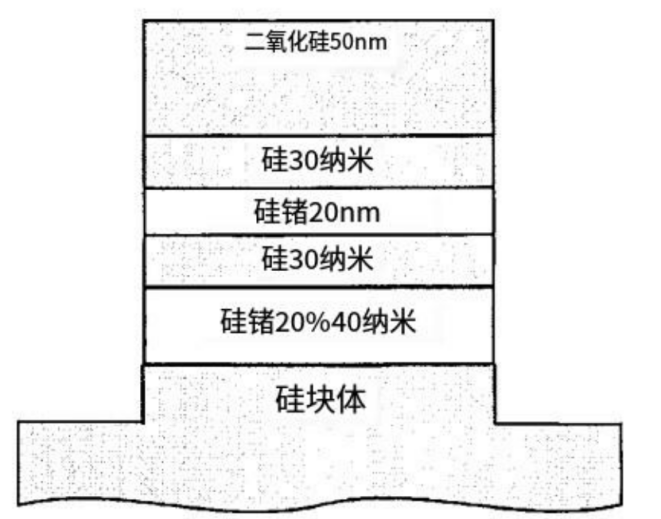

SiGe是制造新型器件所需的具有高载流子迁移率技术上的重要材料。SiGe可用于需要高电子迁移率的器件,如MOSFETs和纳米线晶体管。SiGe还具有对FinFETs、Si/SiGe量子点、直接带隙发射器、中红外波导、超宽带光子学和MEMS器件有用的特性,制造SiGe器件需要蚀刻SiGe。此外,在形成用于纳米晶体管结构的Si纳米线和纳米片时,SiGe也被用作牺牲层。

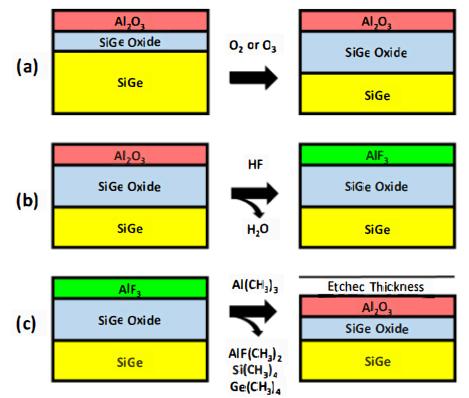

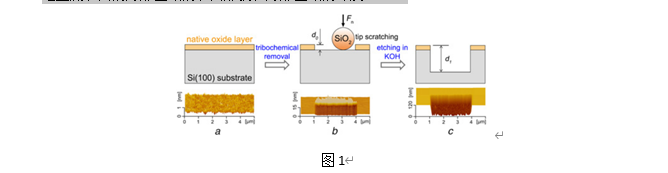

在本文中,英思特报道了利用氧气(O2)、臭氧(O3)、氟化氢(HF)和三米铝[Al(CH3)3]的SiGe。图1显示了这个曝光序列的示意图。

图1:基于O2或O3的氧化,通过HF的氟化的配体交换和转化图

实验与讨论

SiGe的热退火是在暖壁热台型反应器中进行的,其反应器壁保持在160℃。使用筒形加热器加热样品台,样品温度在225℃和290℃之间变化。样品通过重力保持在水平样品台上,其厚度为100纳米的SiGe膜组成。该SiGe膜位于Si(100)晶片上厚度为100纳米的热SiO2层上。

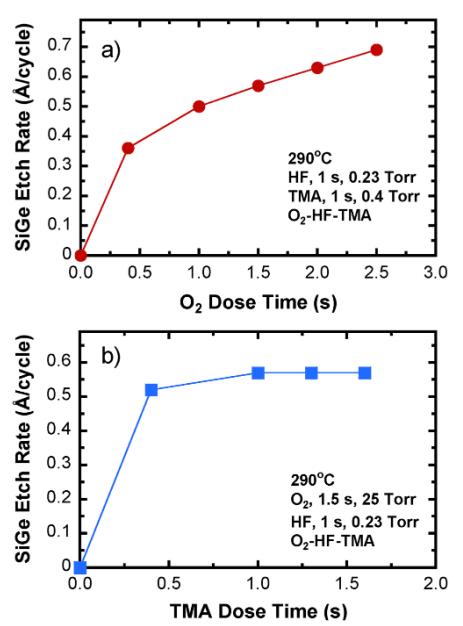

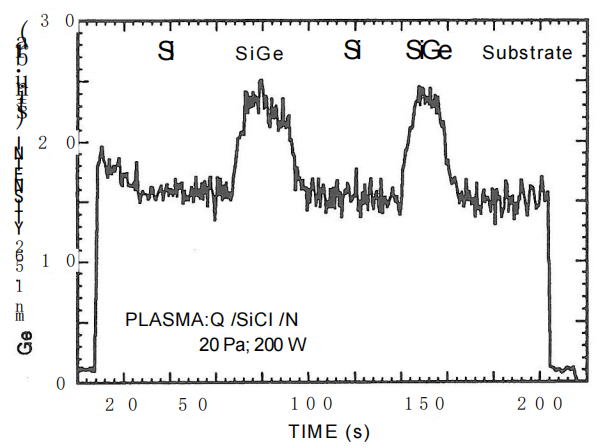

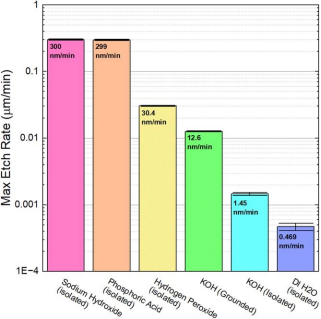

图2显示了SiGe蚀刻速率相对于剂量的变化,以及依赖于温度的SiGe蚀刻速率。图中显示了硅锗蚀刻速率与氧化、转化、氟化和配体交换反应剂量时间的关系。在这个实验中,将SiGe热退火期间TMA和HP的剂量时间固定在1秒,氧剂量时间在0.4秒和2秒之间变化。剂量时间的增加导致Si(100)和LPCVD Si的增加。

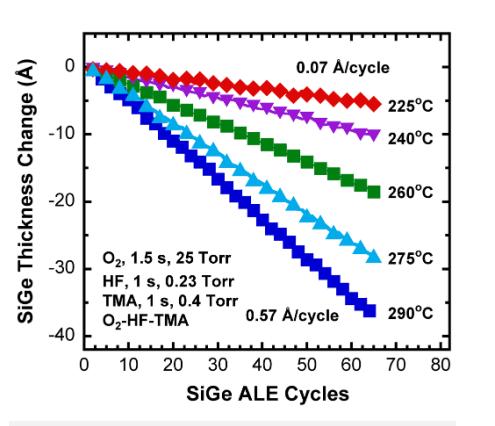

图3显示了SiGe蚀刻速率与TMA剂量时间的关系。Si(100)只在三个不同的温度下进行。TMA的剂量时间在0.4秒和1.7秒之间变化。这些温度产生的活化势垒为6.0千卡/摩尔。此外,硅、氮的腐蚀与硅锗腐蚀速率是HF剂量时间的函数有关。与粘性流条件相比,使用静压的On和导管的TMA剂量分别为1.5s和1.0s。

图2:290℃时SiGe蚀刻速率与剂量时间的关系

图3:不同温度下SiGe厚度变化与ALE循环次数的关系

结论

英思特使用氧化和“转化-蚀刻”机制,研究了SiGe的热ALE。SiGe膜厚度和SiGe膜上的表面氧化物层厚度都在热退火期间使用原位光谱椭偏术来监控,并分析测量了从225℃到290℃的温度依赖性蚀刻速率。

使用-HF-TMA反应序列的其他实验表明,TMA和HF反应是自限性的,并且该反应在290℃时具有合理的自限性。原子力显微镜图像显示,热ALE与-HF-TMA反应顺序没有使SiGe膜变粗糙。

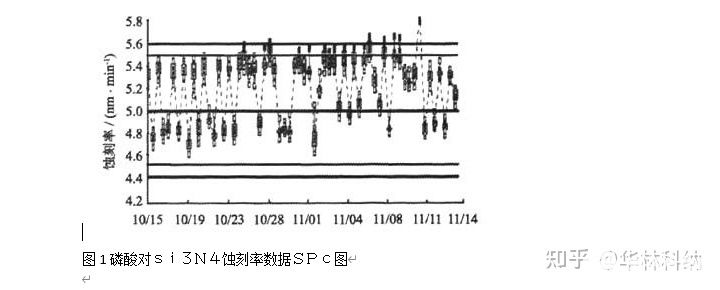

与使用2-HF-TMA反应顺序的Si或si3n 4相比,SiGe热ALE对SiGe也是非常有选择性的。使用氧化和转化-蚀刻机制的SiGe的热退火对于制造SiGe器件应该是有用的。此外,使用SiGe作为牺牲层,SiGe的热退火可以用于形成Si纳米线和Si纳米片。

江苏英思特半导体科技有限公司主要从事湿法制程设备,晶圆清洁设备,RCA清洗机,KOH腐殖清洗机等设备的设计、生产和维护。

审核编辑 黄宇

-

半导体

+关注

关注

336文章

29977浏览量

258031 -

晶圆

+关注

关注

53文章

5344浏览量

131665 -

SiGe

+关注

关注

0文章

99浏览量

24449 -

蚀刻

+关注

关注

10文章

428浏览量

16463

发布评论请先 登录

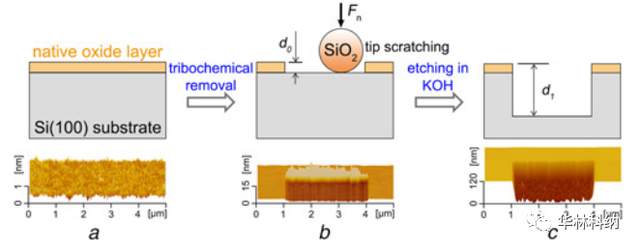

利用原子力显微镜测量硅蚀刻速率

蚀刻简介

晶片边缘蚀刻机及其蚀刻方法

关于原子层蚀刻的分析和介绍

蚀刻简介

详解SiGe的蚀刻和沉积控制

微细加工湿法蚀刻中不同蚀刻方法

如何利用原子力显微镜测量硅蚀刻速率

Si/SiGe多层堆叠的干法蚀刻

锗化硅(SiGe)和硅(Si)之间的各向同性和选择性蚀刻机制

通信——通过表面电荷操纵控制锗的蚀刻

利用氧化和“转化-蚀刻”机制对富锗SiGe的热原子层蚀刻 引言

利用氧化和“转化-蚀刻”机制对富锗SiGe的热原子层蚀刻 引言

评论