我用一个或多或少完整的NVMe VIP测试用例示例结束了我的上一篇博客文章,试图展示从基本设置到执行NVM写入然后读取的所有内容。我们将在这里稍微改变一下,从 NVMe 命令转移到一些可用于协助您测试的 VIP 功能。

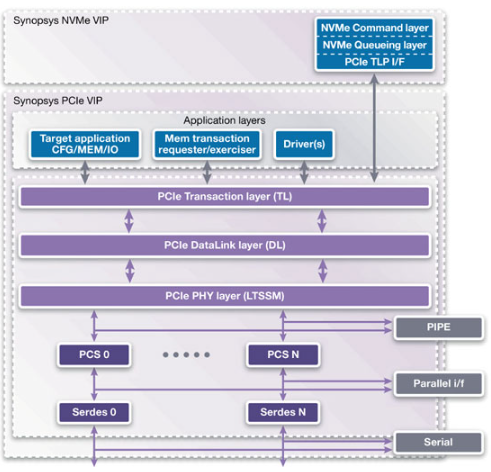

在这里,您可以了解有关适用于 NVMe 和 PCIe 的 Synopsys VC 验证 IP 的更多信息。

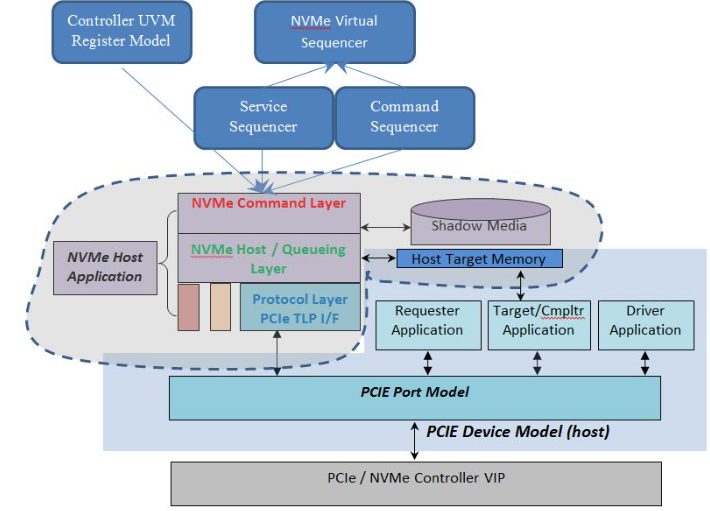

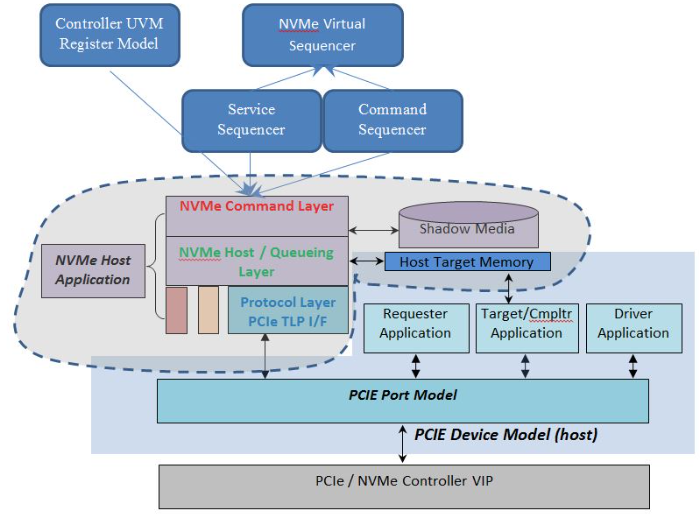

为了让您保持新鲜感,我们将继续参考此图:

如前所述,NVMe VIP 提供了一组丰富的功能来帮助测试。

后台流量

您将在上图中注意到位于 PCIE 端口模型(请求者、目标/cmpltr 和驱动程序)之上的几个应用程序。这些是可用于源(和接收)PCIe 流量(不是专门进出 NVMe)的 PCIe 应用程序。特别:

驱动程序应用程序 – 如果您想生成各种类型的TLP(例如CfgWr,IORd,MemWr),此应用程序就是您的工具。TLP 的各个字段是可配置的,并且会检查收到的完成(例如来自 MemRd 请求)的有效性和正确的数据。您还可以根据需要使用此工具配置或监控 DUT。

目标/完成者应用程序 – 如果远程端点(例如控制器 DUT)将(非 NVMe)流量发送到此主机 VIP,Target 应用程序将执行该请求,将其转过来并生成一个或多个(根据需要和/或配置)完成操作返回到端点。提供定时和数据包大小控制,以及用于详细 TLP 修改的多个回调。

请求者申请 – 此应用程序会向目标生成恒定的 TLP 负载。它可用于创建后台流量,或在目标上造成负载。流量速率、大小和类型都是可配置的。

错误注入

VIP 的一个重要且有用的功能是内置错误注入。NVMe VIP 提供了一种简单但非常强大的机制来导致错误注入,而不必使用回调和定向测试来导致错误。对于每个“脚本...”用户可用的任务(有关详细信息,请参阅以前的帖子),有一个“错误注入”参数。可以使用各种参数填充此参数,以导致该 NVMe 命令发生特定的错误注入。对命令有效的特定错误注入由潜在错误条件控制(根据 NVMe 规范)。

例如,检查“创建 I/O 提交队列”命令的规范会向我们显示该命令可能导致的几个错误,例如“完成队列无效”、“队列标识符无效”和“超出最大队列大小”。您只需要提供类似的错误注入代码,然后会发生以下几件事,而不是创建定向测试来导致这些情况:

VIP 将查找要生成的导致错误的相应值。

这些值将被放置在适当的数据结构中(例如提交队列条目)。

收到错误后,我们会自动禁止显示可能以其他方式引起的任何警告(毕竟这是一个错误)。

如果预期的错误没有到达,它将被标记。

然后,系统已准备好(如果需要)在没有错误注入的情况下重新运行命令。

用户无需进一步工作来测试错误 – 无需设置回调,无需抑制错误。一切都处理得干净透明。

除了 NVMe 层的注入错误之外,您还可以提供协议错误注入。例如,要在 PCIe DL 层导致 LCRC 错误,使用相同的过程:只需为该 LCRC 添加错误注入参数,它就会发生,检查、重试并重新检查事务。所有这些都是在没有任何用户帮助的情况下发生的。

队列围栏

在主机内存中创建队列时,控制器可能会生成错误的内存请求,并可能非法访问队列。这些访问由主机的队列屏蔽机制捕获和标记。主机了解哪些操作(即读取或写入)以及哪些地址对控制器访问有效,并将警惕地监视控制器的访问,以确保它不会尝试(例如)从完成队列读取或写入提交队列。队列和队列条目边界的有效性同样检查。

卷影磁盘

主机 VIP 内置的是一个卷影磁盘,用于跟踪和记录对各种控制器命名空间的块数据写入。一旦发生有效的写入,它就会提交到影子,以后的读取访问将与影子数据进行比较。尽管VIP用户肯定拥有可用的实际读/写数据,但他们无需进行数据比较/检查 - NVMe主机VIP会以静默和自动的方式处理此问题。

控制器配置跟踪

与卷影磁盘类似,主机还跟踪连接到系统的控制器的配置。这有几部分:

寄存器跟踪 – 当控制器 NVMe 寄存器被写入时,主机会“窥探”此写入,并将其存储在本地“寄存器影子”中。VIP 的进一步操作可以参考此内容,以确保操作对于控制器的当前状态有效和/或合理。

识别跟踪 – 正如我们在示例中(在最近几集中)中看到的那样,NVMe 协议让我们同时执行“识别控制器”和“识别命名空间”命令来收集控制器信息。这些信息的相关部分也会保存以供VIP使用。

特征跟踪 – “设置功能”命令用于配置控制器的各种元素——我们监视并收集“设置”和“获取功能”命令信息(根据需要),以完成主机VIP对控制器当前配置和状态的理解。

审核编辑:郭婷

-

控制器

+关注

关注

114文章

17886浏览量

195203 -

寄存器

+关注

关注

31文章

5620浏览量

130440 -

nvme

+关注

关注

0文章

301浏览量

23916

发布评论请先 登录

NVMe高速传输之摆脱XDMA设计18:UVM验证平台

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

NVMe高速传输之摆脱XDMA设计33:初始化功能验证与分析

NVMe高速传输之摆脱XDMA设计34:初始化功能验证与分析2

NVMe高速传输之摆脱XDMA设计37:队列管理功能验证与分析1

NVMe高速传输之摆脱XDMA设计40:队列管理功能验证与分析4

NVMe高速传输之摆脱XDMA设计42:DMA 读写功能验证与分析

如何使用Xilinx AXI VIP对自己的设计搭建仿真验证环境的方法

Cadence推出15种新验证 IP(VIP)解决方案

使用AXI VIP的几个关键步骤及常见功能

覆盖模型 – 填补内存VIP的漏洞

NVMe VIP架构:主机功能

新思科技PCIe 7.0验证IP(VIP)的特性

NVMe VIP:验证功能

NVMe VIP:验证功能

评论