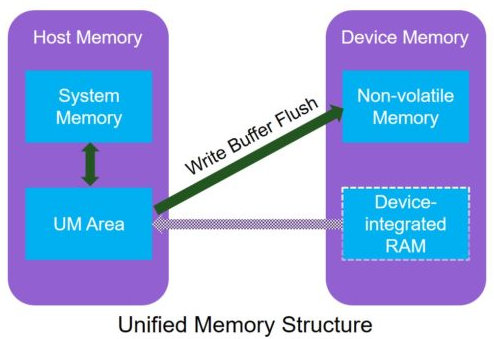

以更低的成本获得更高的存储性能可能会在存储设备的设计中造成瓶颈。为了实现更高的性能,设备必须使用片上DRAM,这增加了总体成本。这就是统一内存扩展(UME),JEDEC规范的出现。它被定义为 JEDEC UFS(通用闪存)规范的扩展。JEDEC UFS设备使用NAND闪存技术进行数据存储。统一内存 (UM) 允许用户将部分主机内存用作设备的内部存储器。由于主机内存已经以大容量提供,因此此机制为设备提供了更大的空间,以用作写入缓冲区 (WB) 缓存或存储逻辑到物理 (L2P) 地址转换表等信息。UM 区域在物理上位于主机端,但最终属于设备,从而取代了设备集成的 RAM,并降低了总体成本。较大的空间可用性意味着设备可以存储大量 L2P 表信息的 WB,从而提高存储性能。

UFS 设备使用扩展的 UFS 传输协议 (UTP) 定义与 UFS 主机通信。每当设备要覆盖 UM 区域中的数据时,都会通过 WB 刷新操作将其写入非易失性存储器,如下所示。

UM 可能包含下面列出的大多数缓存。设备将根据需要更新这些缓存,以便主机和设备具有相同的数据。

L2P 表缓存

WB 缓存

L2P 表缓存标签

WB 缓存标签

统一内存初始化和配置

通过对 dUMAreaSize 属性进行编程,将可用的 UM 区域空间传送到设备。它还将通过 bMaxUMPIURequests 属性传达支持的未完成 UM 请求数,通过同时处理多个 UM 请求来提高性能。主机通过设置 fUM 标志来启用 UM 操作,并轮询该标志,直到设备将其清除。

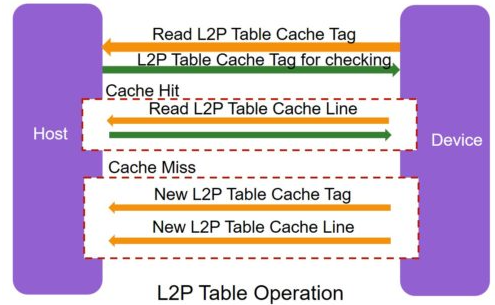

L2P 表操作

设备将读取主机端存在的 L2P 表缓存标记,并将其与自己的副本进行比较。如果发生缓存命中,设备将读取 L2P 表缓存行,否则它将使用新的 L2P 表缓存标记和行更新主机缓冲区,如下所示。仅当更新设备端 L2P 缓存时,才需要执行此操作。

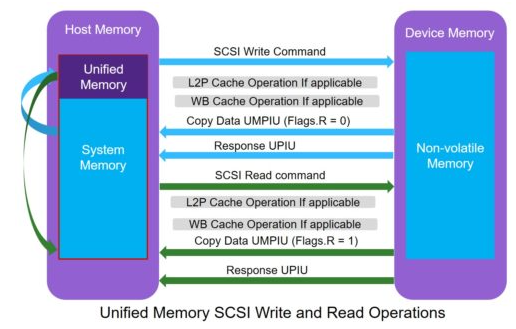

统一内存读/写操作

当主机发送写入请求时,设备将启动 L2P 缓存操作(如果适用)。然后它将读取 WB 标签进行检查。如果发生高速缓存冲突和脏污,则应在 SCSI 数据阶段(从系统内存复制到 UM)之前刷新 WB 行。当主机发送读取请求时,设备将启动 L2P 缓存操作(如果适用)。然后它将读取 WB 标签进行检查。如果缓存命中,它将请求从 UM 复制到系统内存,否则设备将通过“数据输入”UPIU(UFS 协议信息单元)将数据发送到主机。

统一内存的优势

UM 的访问速度远高于非易失性存储器。在访问 L2P 信息时,如果存在缓存未命中,非 UM 方法需要从非易失性存储器中获取此信息。相反,UME方法可以从系统内存中提供此功能,从而将L2P表访问时间缩短十倍。

UM 提供的缓冲区多于设备集成的 RAM;因此,可以存储更多的L2P信息,从而降低缓存未命中率。

统一内存的缺点

主机维护两个内存副本,而不是指向 UM 内存的系统内存。

与设备集成的 RAM 相比,UM 访问的延迟可能更高且更不稳定;但是,除了 UM 区域使用之外,系统可能会通过使用较小的 RAM 来权衡。这可以降低成本,同时为某些读/写访问保留较长的响应时间。

UM 提供空间来存储大量 WB 和 L2P 数据,从而实现更高的性能。因此,不需要大量的设备集成RAM,这有助于降低系统成本和读取延迟。

审核编辑:郭婷

-

DRAM

+关注

关注

41文章

2403浏览量

189657 -

NAND

+关注

关注

16文章

1767浏览量

141318 -

存储器

+关注

关注

39文章

7761浏览量

172295

发布评论请先 登录

怎样使移动电话存储子系统的功耗降至最低

更高的集成度、更低的成本需要更深入的系统理解

低成本高性能宽带光载无线系统

进阶的电动两轮车:更低成本,更高性能的BMS解决方案

对更高的集成度、更低的成本需要更深入的系统的理解

如何实现多速率以太网以更低的成本实现更高的速度

使用TPS25961获得性能更高、空间更小、成本更低的保护功能

以更低的系统成本实现更高的移动存储性能

以更低的系统成本实现更高的移动存储性能

评论