大侠好,欢迎来到FPGA技术江湖。本系列将带来FPGA的系统性学习,从最基本的数字电路基础开始,最详细操作步骤,最直白的言语描述,手把手的“傻瓜式”讲解,让电子、信息、通信类专业学生、初入职场小白及打算进阶提升的职业开发者都可以有系统性学习的机会。

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。后续会陆续更新 Xilinx 的 Vivado、ISE 及相关操作软件的开发的相关内容,学习FPGA设计方法及设计思想的同时,实操结合各类操作软件,会让你在技术学习道路上无比的顺畅,告别技术学习小BUG卡破脑壳,告别目前忽悠性的培训诱导,真正的去学习去实战应用,这种快乐试试你就会懂的。话不多说,上货。

数字电路中的组合逻辑

根据逻辑功能的不同特点,可以将数字电路分为两大类,一类称为组合逻辑电路(简称组合电路),另一类称为时序逻辑电路(简称时序电路)。

在组合逻辑电路中,任何时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。这就是组合逻辑电路在逻辑功能上的共同特点。在上一节中,设计的三人表决器就是组合逻辑电路,输出与输入一一对应,和其他无关,输入发生改变,输出立刻跟着改变。

组合逻辑的设计方法在逻辑代数基础中有一定的简单的叙述。

根据现有的资源做出合理的假设(通过为1、还是为0,不同的硬件可能会是不同的结构)。

根据设计要求和假设,列出真值表。

根据真值表得出表达式,并化简(公式化,卡诺图)。有时需要化简为与非的形式或者其他形式。

根据化简后的布尔表达式做出电路结构,并且验证。

如果最后结果出现错误,上述所有步骤都要检查,如果上述步骤都没有问题,可以考虑电路结构中的连接问题或者器件的损坏。

下面利用一个三人表决器的电路设计来说明一些问题。此电路有三个输入(A、B、C),一个输出(Y),只有当两个及两个以上输入赞成时,Y输出赞成。

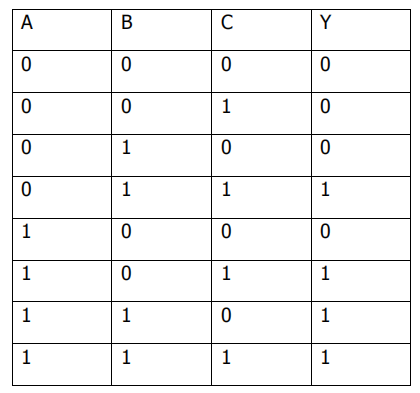

设赞成为1,不赞成为0。根据设计要求得出如下真值表:

图1 :三人表决器真值表

根据真值表中Y为1的项列出来,对应的A、B、C为1,则留下变量,为0,则留下反变量。

Y = A'BC+AB’C+ABC’+ABC;

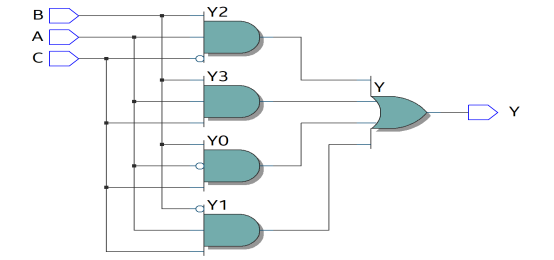

根据上述布尔表达式,我们得出逻辑电路图:

图2 :三人表决器的逻辑电路图

如果所有的逻辑都按照这种写法的话,那么很多的逻辑就会变的很复杂,并且会浪费很多的资源。我们考虑一下,电路既然是按照布尔表达式做出来的,那么布尔表达式能不能化简一下呢?

Y = A'BC+AB’C+ABC’+ABC;

= A'BC+ ABC +AB’C+ ABC+ ABC’+ABC;

= BC(A' + A) + AC(B+B') + AB(C+C')

= BC+AC+AB

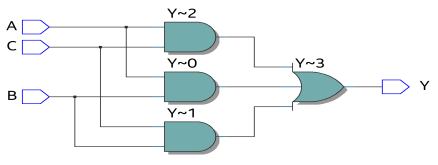

上述布尔表达式所对应的逻辑电路图如下:

图3 :化简后的布尔表达式所对应的电路图

思考 :半加器、全加器、多路选择器、乘法器、除法器等常用组合逻辑电路的设计与实现?

在设计组合逻辑时,分析和设计都是在输入、输出处于稳定的逻辑电平下进行的。为了保证系统工作的可靠性,有必要再观察一下当输入信号逻辑电平发生变化的瞬间电路的工作情况。

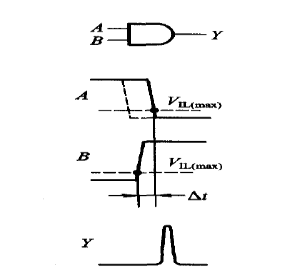

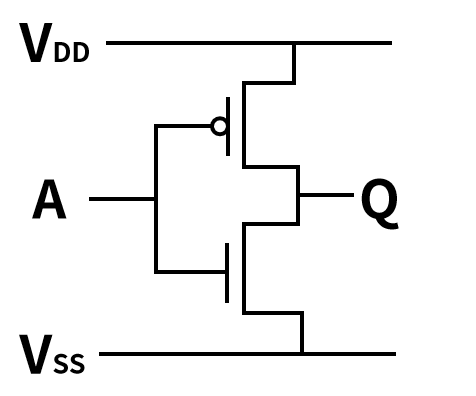

在图1-28所示的与门电路中,稳态下无论A=1、B=0还是A=0、B=1,输出都应该是Y=0;但是输入信号A从1变为0时,如果B从0变为1,由于某些原因(布线的宽度、厚度、温度等),B先从0变为1了,这样在极短的时间内出现了A和B都是1的情况,与门电路就会输出一个极窄的Y=1的尖峰脉冲,或称为电压毛刺。这个尖峰脉冲不符合门电路稳态下的逻辑功能,因而它是系统内部的一种噪声。

图4 :与门由于竞争而产生的尖峰脉冲

将门电路两个输入信号同时向相反的逻辑电平跳变(一个从1变为0,另一个从0变为1)的现象称为竞争。

在有竞争时,不一定都会产生尖峰脉冲。例:在上述的与门中,如果A先于B发生了改变,此时就不会产生尖峰脉冲。

思考:可以尝试分析一下或门,分析或门是否有可能会产生尖峰脉冲?

与门和或门在竞争时,都有可能产生尖峰脉冲。与门和或门是复杂数字逻辑电路中的两个基本门电路,A、B经过不同的传输途径达到,那么在设计时往往难于准确知道A、B到达次序的先后,以及它们在上升时间和下降时间上的细微差异。因此,我们只能说只要存在竞争现象,输出就有可能出现违背稳态下逻辑关系的尖峰脉冲。

由于竞争而在电路输出端可能产生尖峰脉冲的现象称为竞争-冒险。

如果后续电路是一个对尖峰脉冲敏感的电路,那么这种尖峰脉冲将可能使后续电路发生误动作。

思考:如果存在竞争冒险现象的话,应该怎么避免?

可以在输出端接入滤波电容;由于竞争-冒险而产生的尖峰脉冲一般都很窄,所以在输出端并接一个很小的滤波电容就足以把尖峰脉冲的幅度削弱至门电路的阈值电压一下。这种方法简单易行,而缺点是增加了输出电压波形的上升时间和下降时间,使波形变坏。

引入选通脉冲;由于电路的延迟产生的尖峰脉冲是极窄的,如果在输入(输出)信号稳定后,我们再去选取结果作为输出,此时的结果就是正确的。那么此时的选通脉冲就必须要要在稳定后再能出现,否则也无济于事。

修改逻辑设计;此方法的局限性比较大,不再做过多介绍。

通过对组合逻辑的认识,感觉自己已经可以设计任何电路。只要按照标准的设计流程,我们都可以很快的做出电路。

思考 :目前需设计一个自动售货机,贩卖售价为三元的饮料,要求每次只能投入一个一元的硬币。可想而知,我们投入第一个硬币没有反应;投入第二个硬币没有反应;当我们投入第三个硬币时,售货机会给我们一瓶饮料。如果内部是组合逻辑的话,三次投硬币的输入并没有任何改变,但是产生了不同的结果,显然内部结构不是单纯的组合逻辑。内部的功能有一定的记忆性功能,能够清楚的记得之前我们投入的硬币的数量。此时我们应该如何去设计电路。

组合逻辑电路中,任一时刻的输出信号仅取决于当时的输入信号。

更多热点文章阅读

-

电子技术

+关注

关注

19文章

935浏览量

60374 -

电子发烧友论坛

+关注

关注

5文章

198浏览量

1874

原文标题:【教程分享】FPGA零基础学习:数字电路中的组合逻辑

文章出处:【微信号:gh_9b9470648b3c,微信公众号:电子发烧友论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

零基础玩转Linux+Ubuntu实战视频课程

掌握数字设计基础:迈向芯片设计的第一步

高速数字电路设计与安装技巧

FPGA在机器学习中的具体应用

【教程】零基础!手把手教你使用STM32F4进行E22-400T22S编程通信

零基础学习LuatOS编程:快速上手开发实战教程!

【教程分享】FPGA零基础学习:数字电路中的组合逻辑

【教程分享】FPGA零基础学习:数字电路中的组合逻辑

评论