SOC V1.1 项目即将上线!!!

这是一款基于处芯积律SOC V1.0进行升级的项目,主要面向初级工程师/学生的IC实践项目。

SOC V1.1包括一个SOC验证环境和一套QSPI验证环境。

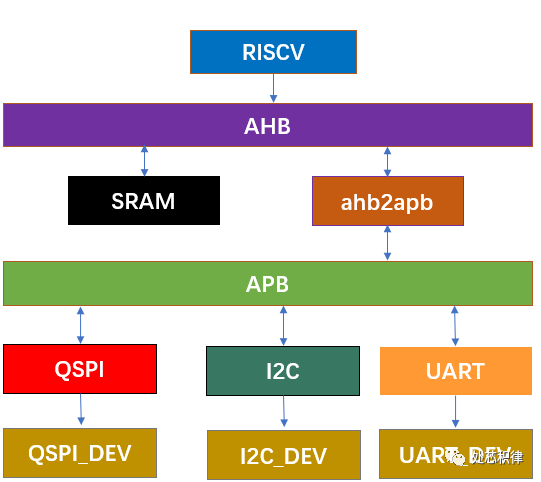

SOC验证环境

以下是SOC V1.1的SOC环境框图

相较于SOC V1.0,SOC V1.1有以下亮点:

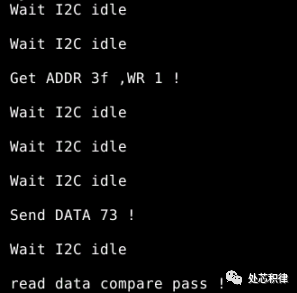

在SOC V1.1的项目中,我们集成了I2C的device,UART的device,方便大家测试I2C和UART的功能。

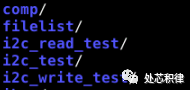

2. 跑仿真环境更加简洁

相较于SOC V1.0的编译环境和仿真环境放在一起,SOC V1.1 将编译文件和仿真文件分开,并且每个test 都有自己的仿真目录。

3.跑仿真指令更加简单

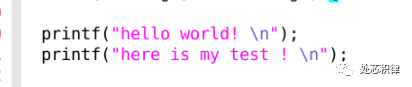

编译:make comp 执行: make run_xxx 4.实现C代码中字符串打印

麻雀虽小,五脏俱全。作为学习型SOC验证项目,处芯积律SOC V1.1是一款性价比极高的实践项目。

QSPI 验证环境

1. 更加完善的验证环境

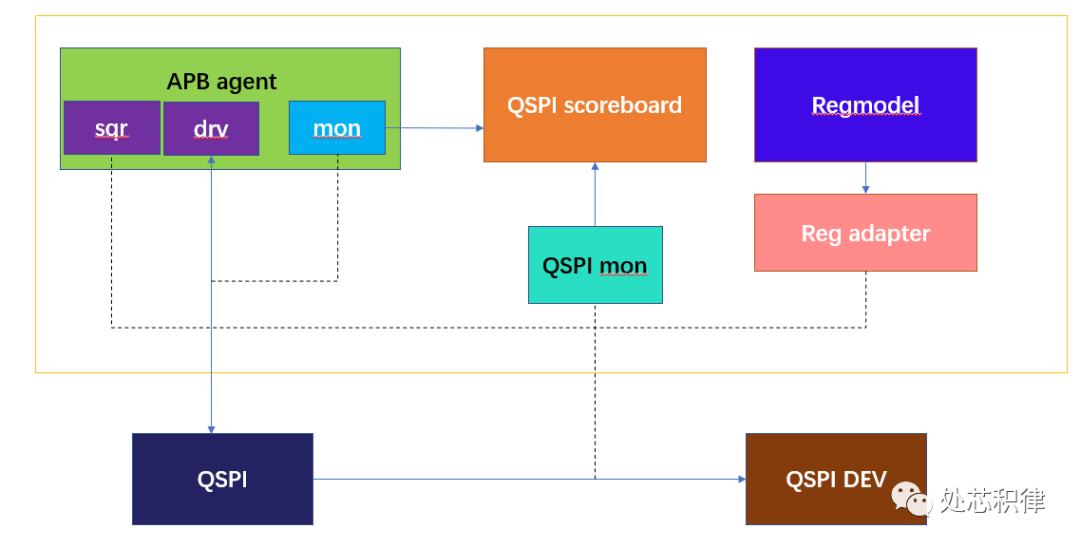

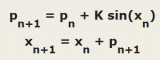

相较于SOC V1.0 简单的QSPI验证环境,SOC V1.1做了升级,加入了reference model。

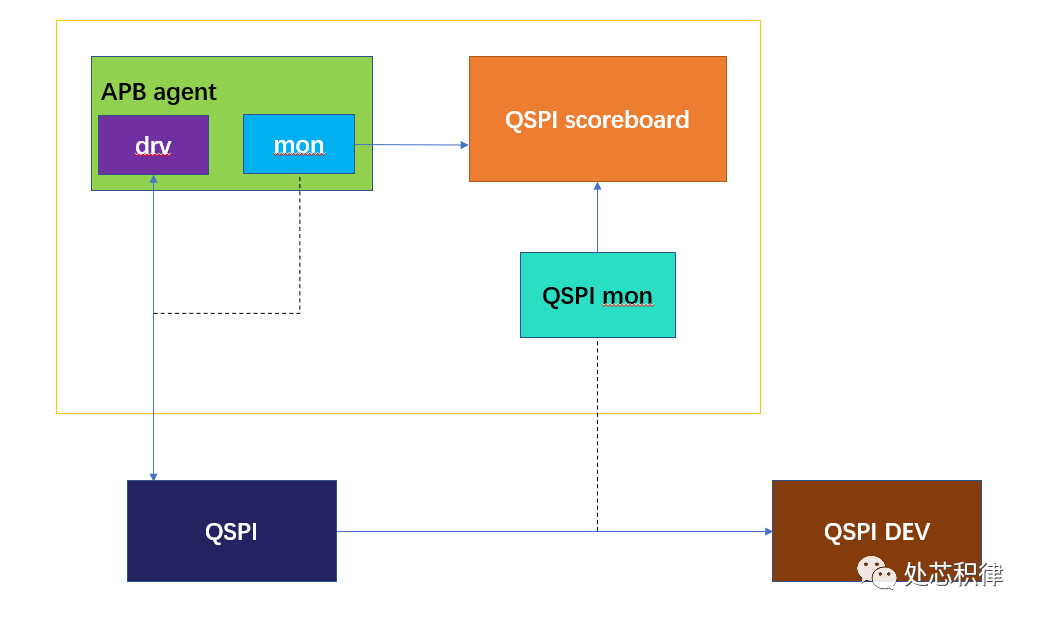

1.0的QSPI环境

1.1的 QSPI 环境

2. 更完善的验证计划

在SOC V1.0 中,我们未提供 testplan;

在SOC V1.1 中,我们提供了完善的QSPI 验证计划。

3. 更多的验证用例

在test 上,我们针对 QSPI开发了14只test,包含了random test 和 direct test。

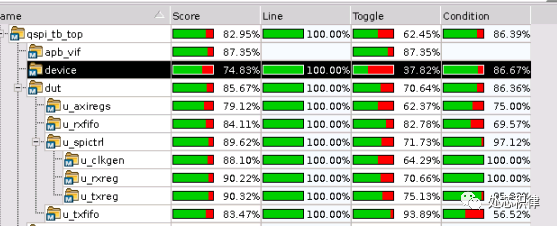

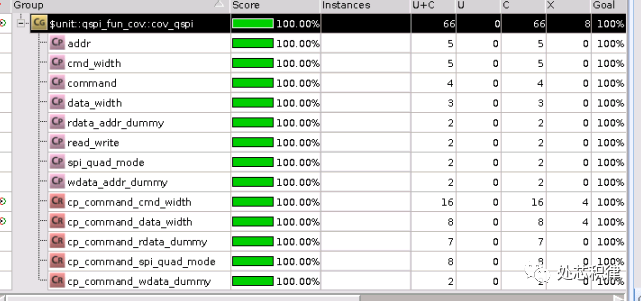

4. 更全的coverage

同时,我们在coverage 上面,将line coverage 收集到 100%。

除了line coverage,本次project 中引入function coverage,我们也将其收集到100%。

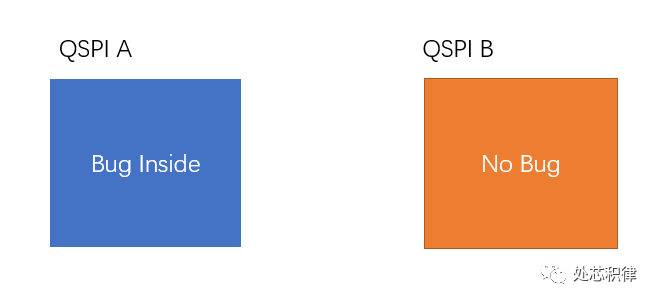

5. 提供有问题的代码供大家debug

为了让大家快速掌握项目,我们提供了两个版本的RTL。一份RTL里面有很多bug,另一份RTL是我们验证过的。大家可以在找bug的过程中加深环境、协议和设计的理解。

审核编辑 :李倩

-

soc

+关注

关注

40文章

4632浏览量

230227 -

仿真

+关注

关注

55文章

4538浏览量

138684 -

uart

+关注

关注

22文章

1322浏览量

107008

原文标题:SOC项目上新啦!看看我们做了哪些改进?

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

NVT2008电平转换器,上电时输出阶跃问题求解

当前VisionFive开发板上的JH7100 SoC对于NVDLA软件站适配的情况是什么样的?

芯片印刷除钨浆料的改进

如何使用CMSIS DAP仿真器调试,通过NucleiStudio调试蜂鸟SOC

如何在Vivado上仿真蜂鸟SOC,仿真NucleiStudio编译好的程序

全国产SoC片上系统无线模块技术深度解析与应用指南

AUDIO SoC的解决方案

了解SOLIDWORKS202仿真方面的改进

上能电气助力金华600MW农光互补光伏发电项目并网

超小型Neuton机器学习模型, 在任何系统级芯片(SoC)上解锁边缘人工智能应用.

基于DE1-SOC开发板的oneAPI实验教程(2)

Altera Agilex 3 FPGA和SoC产品介绍

SOC项目上新啦!做了哪些改进?

SOC项目上新啦!做了哪些改进?

评论